一种多相位时钟生成电路.pdf

是你****松呀

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种多相位时钟生成电路.pdf

本申请公开了一种多相位时钟生成电路,包括:第一分频器,接收第一时钟信号并对第一时钟信号进行分频生成具有多个相位的第二时钟信号;第二分频器,连接第一分频器并对第二时钟信号中某个相位的时钟信号进行分频;若干个依次连接的第一锁存电路,第二分频器输出分频后的时钟信号到第一个第一锁存电路,每个第一锁存电路对上一个第一锁存电路输出的时钟信号进行延迟并输出到下一个第一锁存电路;若干个第一逻辑电路,分别接收第一分频器和其中一个第一锁存电路的输出,进行逻辑运算后生成第三时钟信号。第一时钟信号、第二时钟信号和第三时钟信号的频

一种无死区的高速时钟相位检测电路.pdf

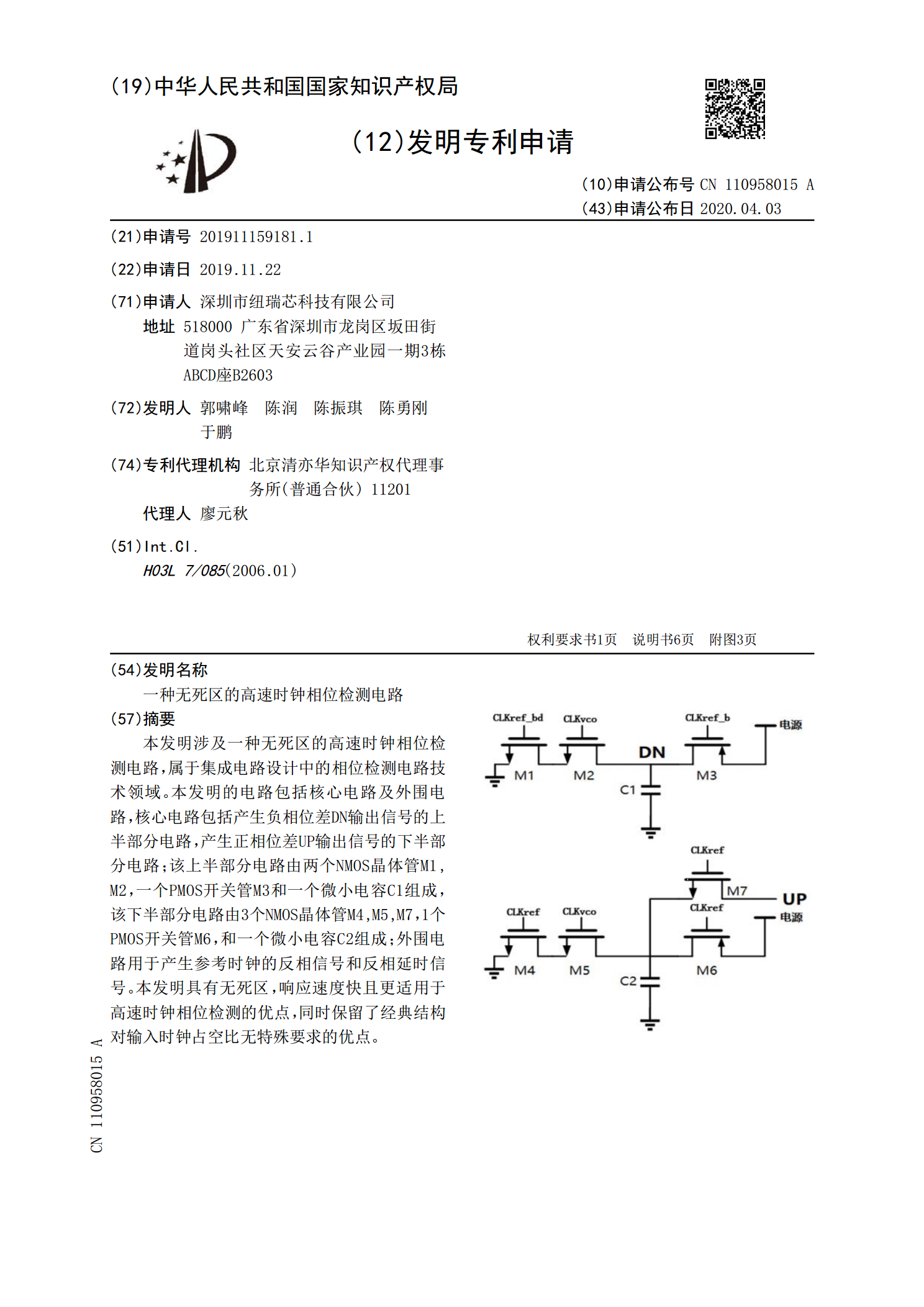

本发明涉及一种无死区的高速时钟相位检测电路,属于集成电路设计中的相位检测电路技术领域。本发明的电路包括核心电路及外围电路,核心电路包括产生负相位差DN输出信号的上半部分电路,产生正相位差UP输出信号的下半部分电路;该上半部分电路由两个NMOS晶体管M1,M2,一个PMOS开关管M3和一个微小电容C1组成,该下半部分电路由3个NMOS晶体管M4,M5,M7,1个PMOS开关管M6,和一个微小电容C2组成;外围电路用于产生参考时钟的反相信号和反相延时信号。本发明具有无死区,响应速度快且更适用于高速时钟相位检测

用于驱动像素的时钟生成电路.pdf

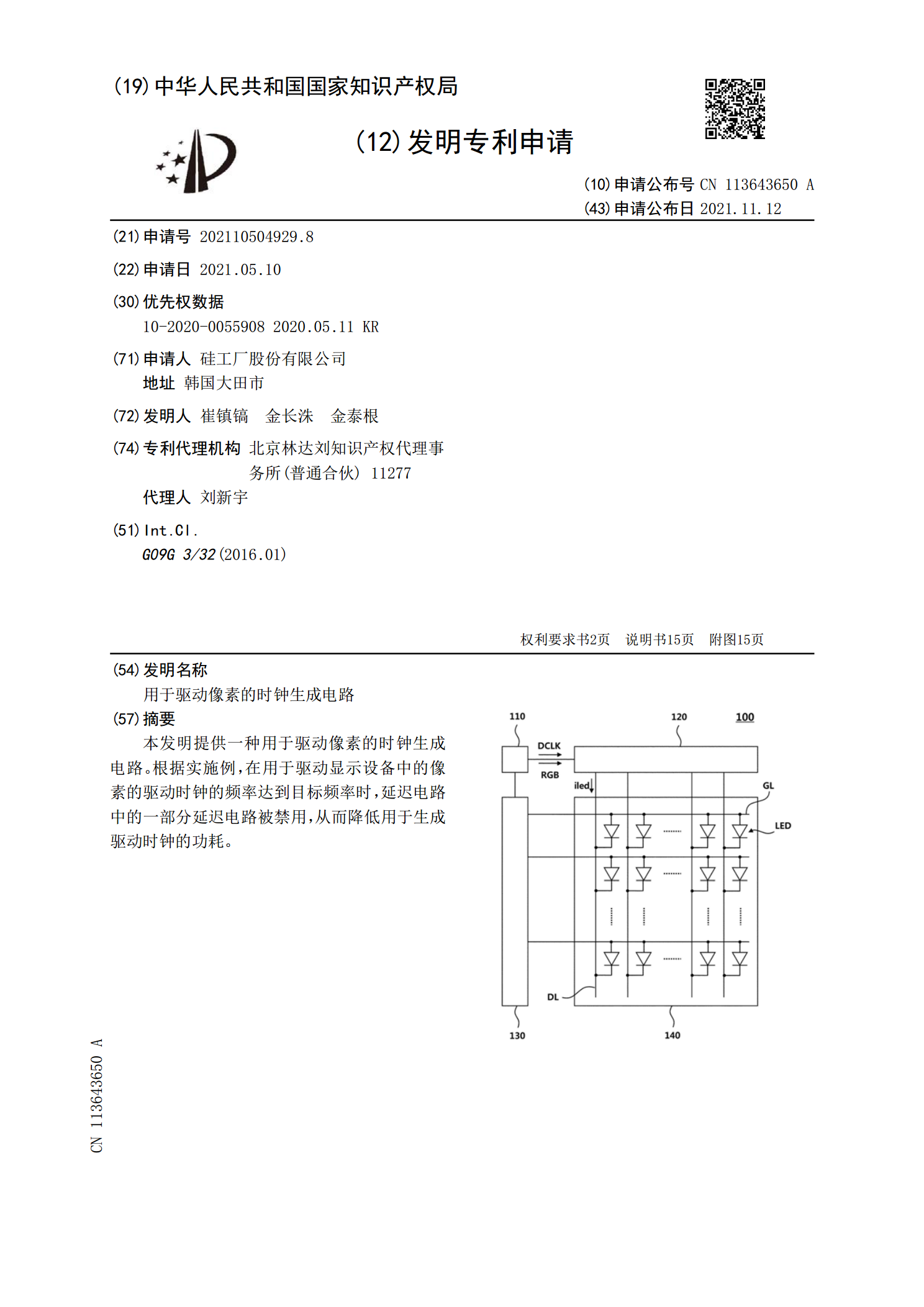

本发明提供一种用于驱动像素的时钟生成电路。根据实施例,在用于驱动显示设备中的像素的驱动时钟的频率达到目标频率时,延迟电路中的一部分延迟电路被禁用,从而降低用于生成驱动时钟的功耗。

一种用于高速串行收发器的时钟相位对齐方法及电路.pdf

一种用于高速串行收发器的时钟相位对齐方法及电路。方法包括步骤1:在N个参考时钟信号周期内,对待处理通道的并行时钟信号采样,以获取N个采样结果,采样结果为第一数值或第二数值,N>1;步骤2:根据N个采样结果中第一数值的个数,确定计数结果;步骤3:多次调整并行时钟信号的相位,并在每次调整后重复步骤1和步骤2,以获得数值从0到N的多个计数结果;步骤4:绘制延迟时间与对应的计数结果的关系曲线;步骤5:根据关系曲线的上升沿或下降沿对应的延迟时间,对并行时钟信号进行相位调整;步骤6:对其他待处理的通道重复步骤1

一种实现高精度相位差控制的多相时钟产生方法和电路.pdf

本发明涉及一种实现高精度相位差控制的多相时钟产生方法,在于使多相时钟产生电路以差分信号的形式输出n路相位差等距的时钟信号,还在于使n路时钟信号通过匹配电路、差分传输线分别传输至相应的可控延时电路中进行相位校正,然后将校正的n路时钟信号分别传输至受驱动端。本发明提供的方法通过在时钟信号传输的过程中增设一可控延时电路来对各路时钟信号的相位进行校正,从而使得能够对多相时钟之间的相位差实现高精度的控制。