一种具有双数据通道的EtherCAT主站系统.pdf

戊午****jj

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种具有双数据通道的EtherCAT主站系统.pdf

本申请公开了一种具有双数据通道的EtherCAT主站系统,包括微处理器、随机存取单元、FPGA模块和以太网物理层模块,并通过以太网物理层模块连接一组伺服从站;通过随机存取单元配合微处理器对EtherCAT主站协议栈进行运行和维护;过程数据驱动模块以驻留在FPGA存储模块中的过程数据镜像为数据源,使用实时数据通道实现主站的周期性通信;微处理器无需取走过程数据镜像,而是通过地址映射通信总线进行字节访问。本申请利用硬件优化了数据传输路径,降低了周期性通信的延迟和抖动,可实现较短的主站周期,适用于数控机床高速插补

EtherCAT通信系统主站及通信方法.pdf

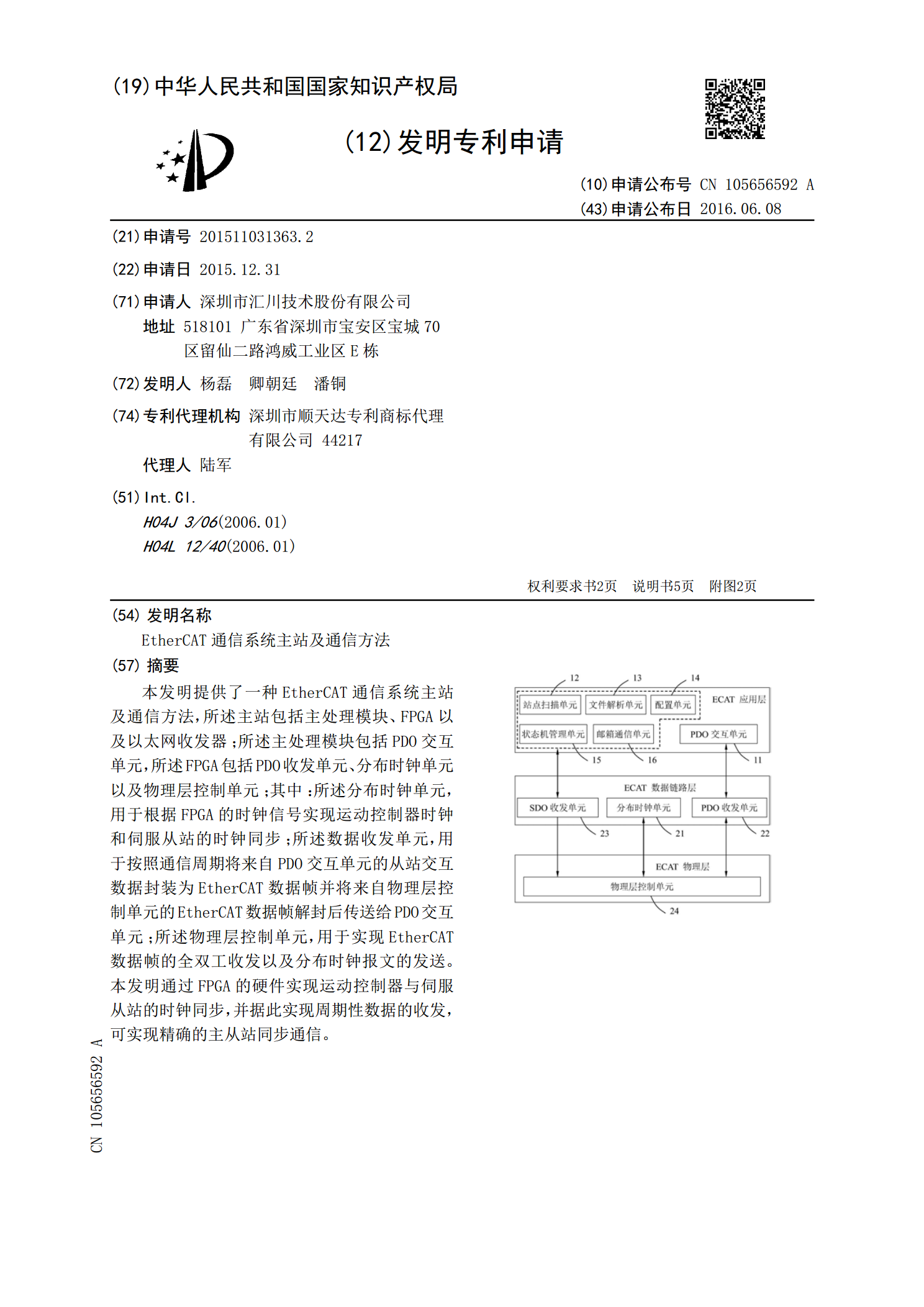

本发明提供了一种EtherCAT通信系统主站及通信方法,所述主站包括主处理模块、FPGA以及以太网收发器;所述主处理模块包括PDO交互单元,所述FPGA包括PDO收发单元、分布时钟单元以及物理层控制单元;其中:所述分布时钟单元,用于根据FPGA的时钟信号实现运动控制器时钟和伺服从站的时钟同步;所述数据收发单元,用于按照通信周期将来自PDO交互单元的从站交互数据封装为EtherCAT数据帧并将来自物理层控制单元的EtherCAT数据帧解封后传送给PDO交互单元;所述物理层控制单元,用于实现EtherCAT数

高速高精多通道数控系统中基于FPGA的EtherCAT主站设计的开题报告.docx

高速高精多通道数控系统中基于FPGA的EtherCAT主站设计的开题报告开题报告:高速高精多通道数控系统中基于FPGA的EtherCAT主站设计一、选题背景和意义(一)选题背景随着机床自动化程度的不断提高,数字化、网络化和智能化成为机床发展的趋势,数字化控制系统中的数字信号处理技术应用越来越广泛,而FPGA作为一种可编程逻辑器件,因其高速、高精度、低延迟等优点,广泛应用于数字信号处理领域,并在数字信号处理的硬件实现中发挥着非常重要的作用。以太网通讯技术是现在数字化控制系统中广泛使用的通讯技术之一,而其最流

高速高精多通道数控系统中基于FPGA的EtherCAT主站设计的任务书.docx

高速高精多通道数控系统中基于FPGA的EtherCAT主站设计的任务书任务书一、任务背景随着现代工业不断发展和进步,对于高速高精多通道数控系统的需求也越来越高,而这种系统对于控制的要求也越来越高。在工业控制中,以太网通信技术已经得到了广泛的应用,而EtherCAT作为实时以太网通信技术的代表,在高速高精多通道数控系统中也有着广泛的应用。因此,如何实现基于FPGA的EtherCAT主站设计成为了一个重要的研究方向和解决方案。二、任务目标本次任务的目标是设计基于FPGA的EtherCAT主站。具体目标如下:1

一种EtherCAT主站的通讯方法、装置以及介质.pdf

本申请公开了一种EtherCAT主站的通讯方法,在接收到上电信号后,调用存储于本地系统中的程序,并根据程序获取各从站的待配置信息,然后配置并分发各待配置信息至各从站,控制各从站进入OP状态。相对于当前技术中,需要上位机配置ARM芯片。采用本技术方案,通讯所需的指令已提前存储于ARM芯片中,在接收到上电信号后,自动运行ARM芯片内的程序实现与从站的信息交互,使通讯脱离上位机的配置,提高了通讯的灵活度。并且,通讯所需的协议全部集成在ARM芯片中,无需额外购买专用的协议芯片,减少了通讯的成本。本申请还公开了一种