LDMOS器件制作方法、LDMOS器件和终端设备.pdf

映雁****魔王

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

LDMOS器件制作方法、LDMOS器件和终端设备.pdf

本发明公开了一种LDMOS器件制作方法,包括在衬底或外延层上形成浅沟槽隔离、栅介质层并定义多晶硅栅;形成高能量漂移区和RESUR层注入区,以及低能量漂移区;多晶硅栅进行光刻,刻蚀后保留光刻胶,进行注入形成体区;形成侧墙,在体区形成第一重掺杂区和第二重掺杂区,在低能量漂移区形成第一重掺杂区,沉积金属硅化反应阻挡介质层;在多晶硅栅、第一重掺杂区和第二重掺杂区和表面形成金属硅化物;沉积绝缘介质刻蚀停止层,沉积层间介质层;形成多个接触孔和第一金属层,近沟道一侧的第一部分接触孔通过金属层短接至栅极,靠近漏极一侧的第

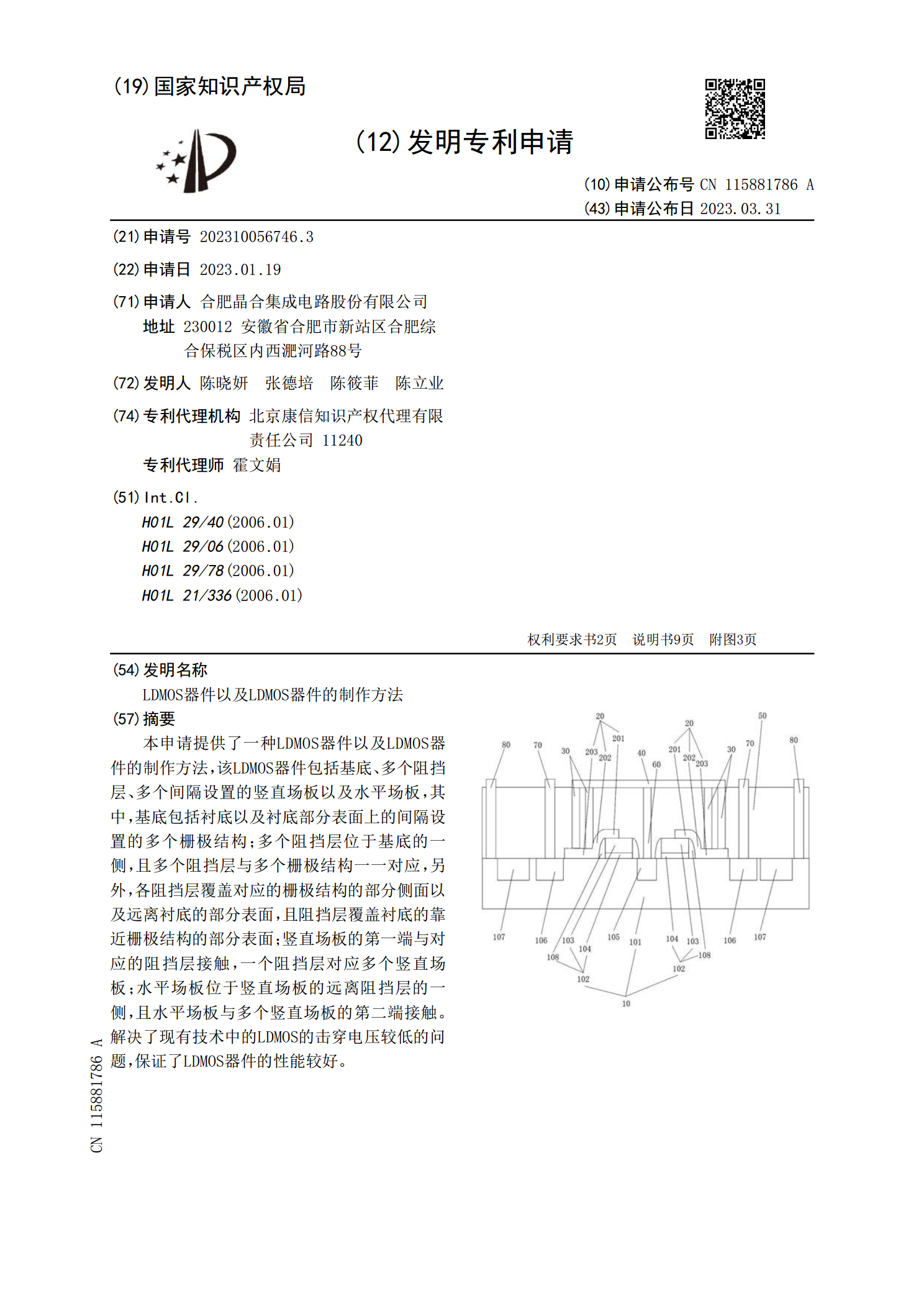

LDMOS器件以及LDMOS器件的制作方法.pdf

本申请提供了一种LDMOS器件以及LDMOS器件的制作方法,该LDMOS器件包括基底、多个阻挡层、多个间隔设置的竖直场板以及水平场板,其中,基底包括衬底以及衬底部分表面上的间隔设置的多个栅极结构;多个阻挡层位于基底的一侧,且多个阻挡层与多个栅极结构一一对应,另外,各阻挡层覆盖对应的栅极结构的部分侧面以及远离衬底的部分表面,且阻挡层覆盖衬底的靠近栅极结构的部分表面;竖直场板的第一端与对应的阻挡层接触,一个阻挡层对应多个竖直场板;水平场板位于竖直场板的远离阻挡层的一侧,且水平场板与多个竖直场板的第二端接触。解

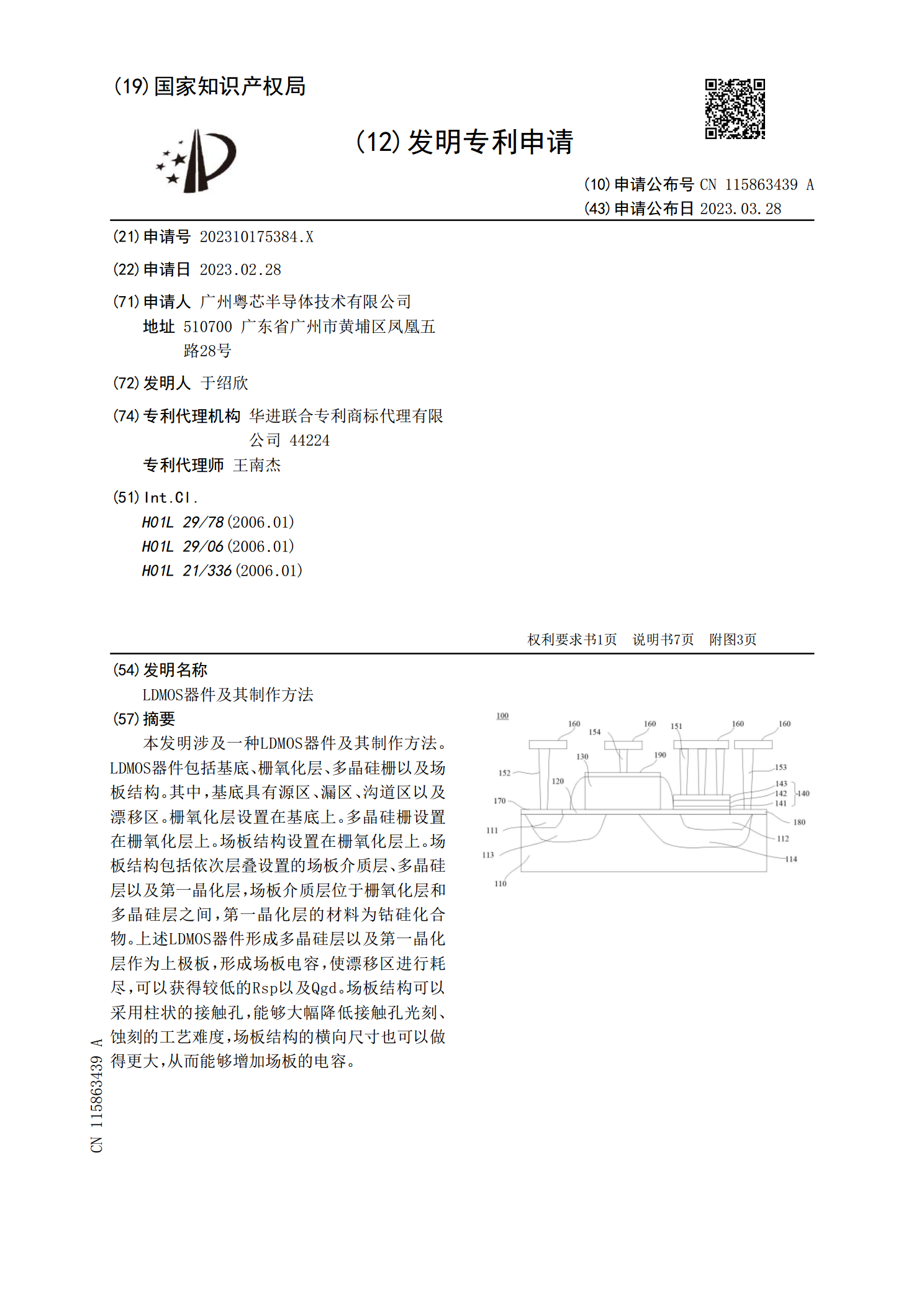

LDMOS器件及其制作方法.pdf

本发明涉及一种LDMOS器件及其制作方法。LDMOS器件包括基底、栅氧化层、多晶硅栅以及场板结构。其中,基底具有源区、漏区、沟道区以及漂移区。栅氧化层设置在基底上。多晶硅栅设置在栅氧化层上。场板结构设置在栅氧化层上。场板结构包括依次层叠设置的场板介质层、多晶硅层以及第一晶化层,场板介质层位于栅氧化层和多晶硅层之间,第一晶化层的材料为钴硅化合物。上述LDMOS器件形成多晶硅层以及第一晶化层作为上极板,形成场板电容,使漂移区进行耗尽,可以获得较低的Rsp以及Qgd。场板结构可以采用柱状的接触孔,能够大幅降低接

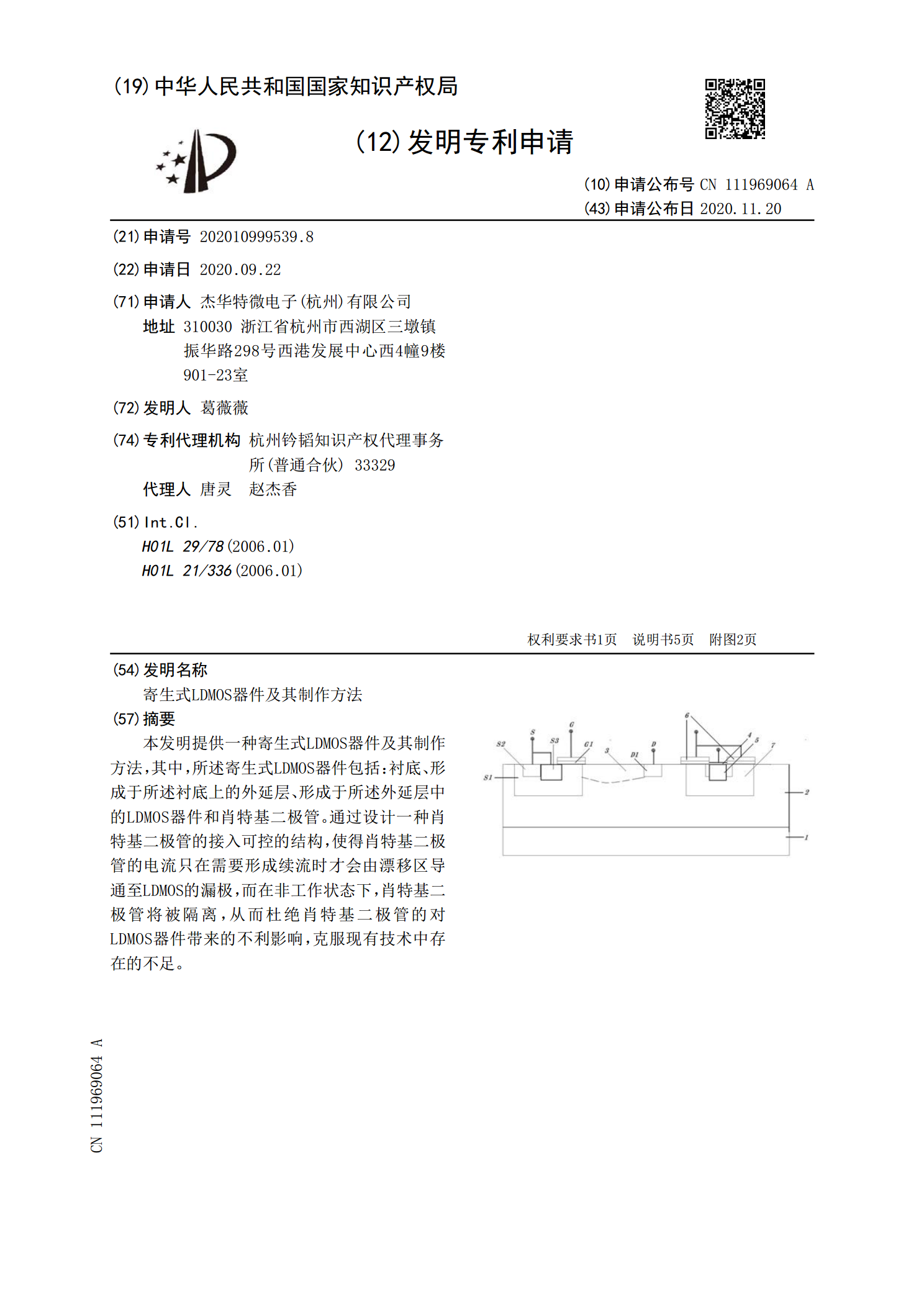

寄生式LDMOS器件及其制作方法.pdf

本发明提供一种寄生式LDMOS器件及其制作方法,其中,所述寄生式LDMOS器件包括:衬底、形成于所述衬底上的外延层、形成于所述外延层中的LDMOS器件和肖特基二极管。通过设计一种肖特基二极管的接入可控的结构,使得肖特基二极管的电流只在需要形成续流时才会由漂移区导通至LDMOS的漏极,而在非工作状态下,肖特基二极管将被隔离,从而杜绝肖特基二极管的对LDMOS器件带来的不利影响,克服现有技术中存在的不足。

LDMOS器件性能研究与综述.docx

LDMOS器件性能研究与综述LDMOS(LaterallyDiffusedMetal-Oxide-Semiconductor)器件是一种常用的功率器件,主要应用于射频和微波功率放大器等高功率应用中。本文将针对LDMOS器件的性能特点进行研究和综述。LDMOS器件由多个Metal-Oxide-Semiconductor(MOS)结构组成,其中金属电极被侧向扩散,形成巨型杂散极结构。这种侧向扩散结构使得LDMOS器件具有低电阻和高耐压的特点,适用于高功率应用。同时,LDMOS器件还具有良好的热稳定性和高频特性