沟槽栅的制造方法.pdf

邻家****mk

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

沟槽栅的制造方法.pdf

本发明公开了一种沟槽栅的制造方法,包括:步骤一、在半导体衬底表面形成沟槽。步骤二、形成第一氧化层,第一氧化层形成后需要使沟槽的顶部保持为开口状态并在沟槽内包围处第二沟槽。步骤三、沉积第二介质层,第二介质层形成后需要使沟槽的顶部开口保持或封闭。步骤四、进行第一次化学机械研磨工艺使第二沟槽外第二介质层都去除,保留的所述第二介质层覆盖位于在所述第二沟槽的侧面和底部表面。步骤五、以保留的第二介质层为掩膜对第一氧化层进行从顶部到底部的第二次刻蚀以形成栅极底部氧化层。步骤六、去除第二介质层。步骤七、进行栅氧化层的生长

沟槽栅的制造方法.pdf

本发明公开了一种沟槽栅的制造方法,包括步骤:步骤一、在半导体衬底表面形成沟槽;步骤二、形成第一氧化层;步骤三、根据沟槽的深宽比选用涂布层并形成将沟槽完全填充的涂布层;步骤四、采用干法刻蚀工艺对涂布层进行全面回刻;步骤五、以保留于沟槽底部的涂布层为掩膜进行第一氧化层的湿法刻蚀形成栅极底部氧化层;步骤六、去除涂布层;步骤七、进行栅氧化层的生长。本发明能采用较低成本实现BTO,从而能降低工艺成本;能在更小深宽比的沟槽中形成良好的BTO,从而能适用于各种深宽比的沟槽的BTO形成,从而具有较大的使用范围。

沟槽栅的制造方法.pdf

本发明公开了一种沟槽栅的制造方法,包括:步骤一、在半导体衬底表面形成沟槽。步骤二、形成第一氧化层,第一氧化层形成后需要使沟槽的顶部保持为开口状态。步骤三、沉积第二介质层,第二介质层形成后需要使沟槽的顶部开口封闭并在沟槽内部形成一个被第二介质层所包围的空腔。步骤四、对所述第二介质层进行第一次回刻将空腔外暴露的第二介质层去除且保证空腔顶部封口处的第二介质层保留。步骤五、以空腔周侧的第二介质层为掩膜对第一氧化层进行从顶部到底部的第二次刻蚀以形成栅极底部氧化层。步骤六、去除第二介质层。步骤七、进行栅氧化层的生长。

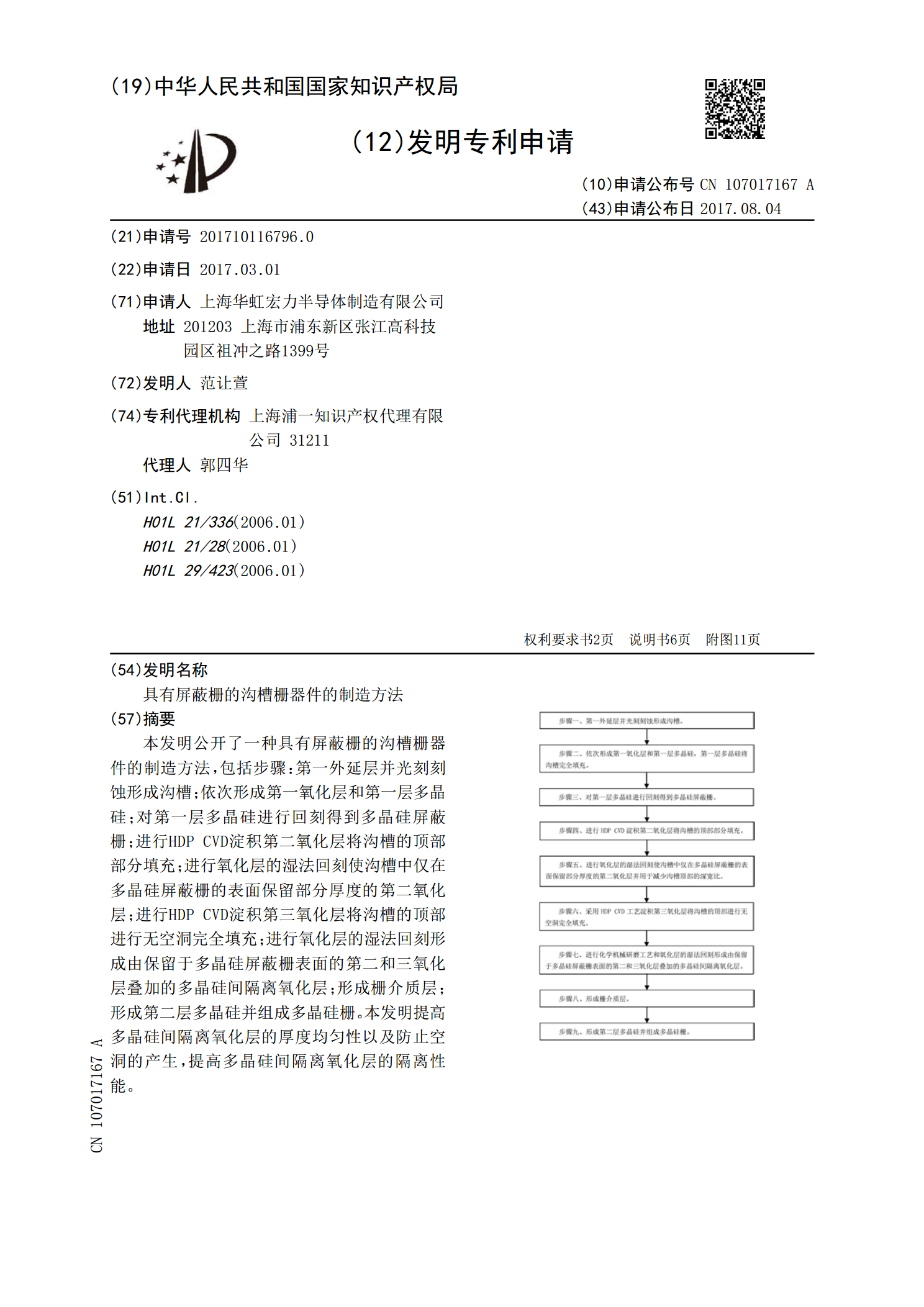

具有屏蔽栅的沟槽栅器件的制造方法.pdf

本发明公开了一种具有屏蔽栅的沟槽栅器件的制造方法,包括步骤:第一外延层并光刻刻蚀形成沟槽;依次形成第一氧化层和第一层多晶硅;对第一层多晶硅进行回刻得到多晶硅屏蔽栅;进行HDPCVD淀积第二氧化层将沟槽的顶部部分填充;进行氧化层的湿法回刻使沟槽中仅在多晶硅屏蔽栅的表面保留部分厚度的第二氧化层;进行HDPCVD淀积第三氧化层将沟槽的顶部进行无空洞完全填充;进行氧化层的湿法回刻形成由保留于多晶硅屏蔽栅表面的第二和三氧化层叠加的多晶硅间隔离氧化层;形成栅介质层;形成第二层多晶硅并组成多晶硅栅。本发明提高多晶硅

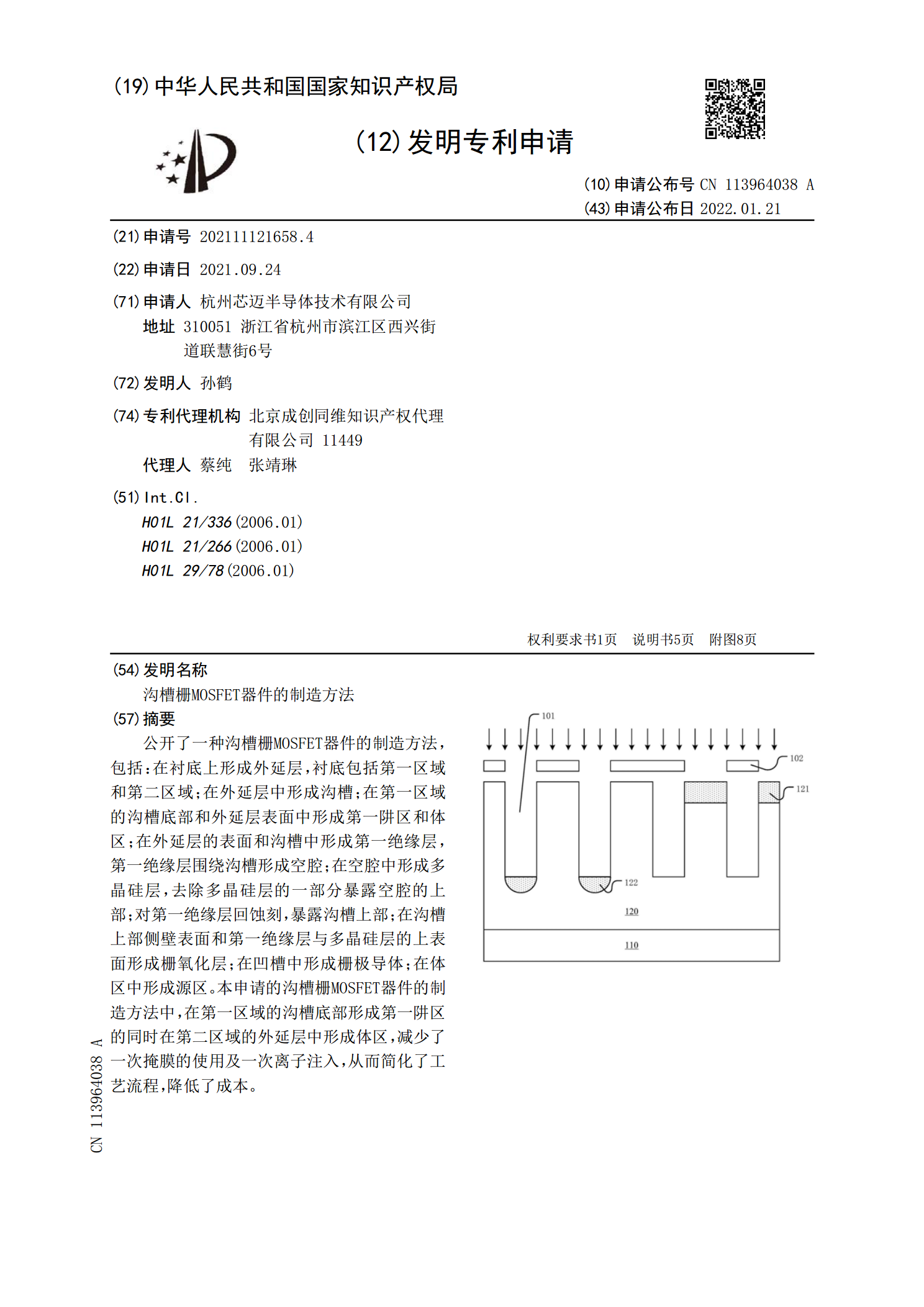

沟槽栅MOSFET器件的制造方法.pdf

公开了一种沟槽栅MOSFET器件的制造方法,包括:在衬底上形成外延层,衬底包括第一区域和第二区域;在外延层中形成沟槽;在第一区域的沟槽底部和外延层表面中形成第一阱区和体区;在外延层的表面和沟槽中形成第一绝缘层,第一绝缘层围绕沟槽形成空腔;在空腔中形成多晶硅层,去除多晶硅层的一部分暴露空腔的上部;对第一绝缘层回蚀刻,暴露沟槽上部;在沟槽上部侧壁表面和第一绝缘层与多晶硅层的上表面形成栅氧化层;在凹槽中形成栅极导体;在体区中形成源区。本申请的沟槽栅MOSFET器件的制造方法中,在第一区域的沟槽底部形成第一阱区的