改善字线多晶硅层研磨后硬掩模层厚度均匀性的方法.pdf

一吃****海逸

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

改善字线多晶硅层研磨后硬掩模层厚度均匀性的方法.pdf

本申请提供一种改善字线多晶硅层研磨后硬掩模层厚度均匀性的方法,包括:提供一衬底,衬底分为核心区和外围区,核心区上形成有多个闪存栅结构;沉积硬掩模层,覆盖核心区和外围区;刻蚀硬掩模层,在核心区的硬掩模层中形成多个条状沟槽;沉积字线多晶硅层,覆盖硬掩模层并填满多个条状沟槽;研磨字线多晶硅层和硬掩模层至硬掩模层的厚度比预定厚度多出预留部分时终止;实施浸泡工艺去除硬掩模层的预留部分。通过先将硬掩模层研磨至比预定厚度多出预留部分再实施浸泡工艺去除该预留部分的方式,提高字线多晶硅层研磨后硬掩模层厚度的均匀性,减少后续

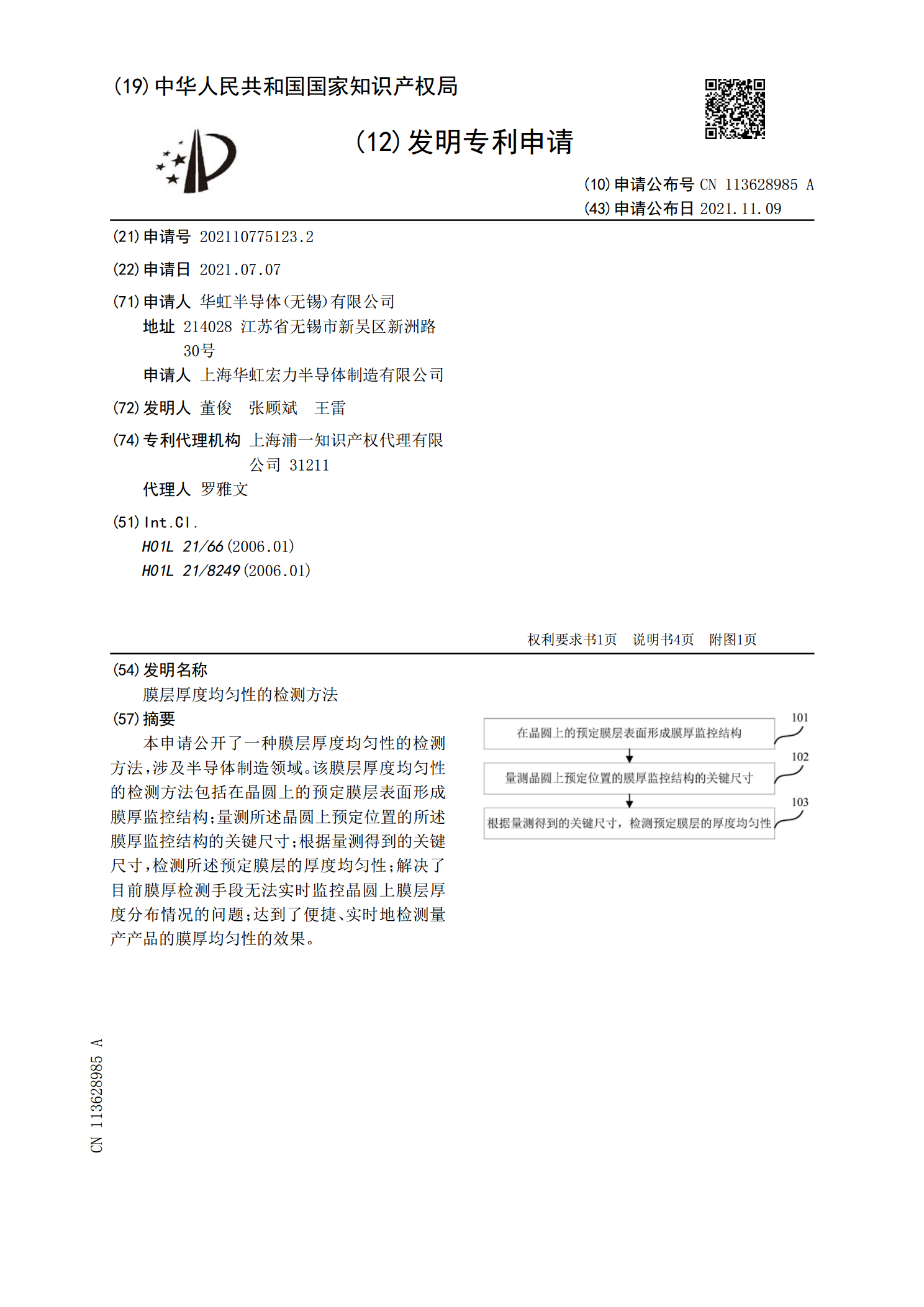

膜层厚度均匀性的检测方法.pdf

本申请公开了一种膜层厚度均匀性的检测方法,涉及半导体制造领域。该膜层厚度均匀性的检测方法包括在晶圆上的预定膜层表面形成膜厚监控结构;量测所述晶圆上预定位置的所述膜厚监控结构的关键尺寸;根据量测得到的关键尺寸,检测所述预定膜层的厚度均匀性;解决了目前膜厚检测手段无法实时监控晶圆上膜层厚度分布情况的问题;达到了便捷、实时地检测量产产品的膜厚均匀性的效果。

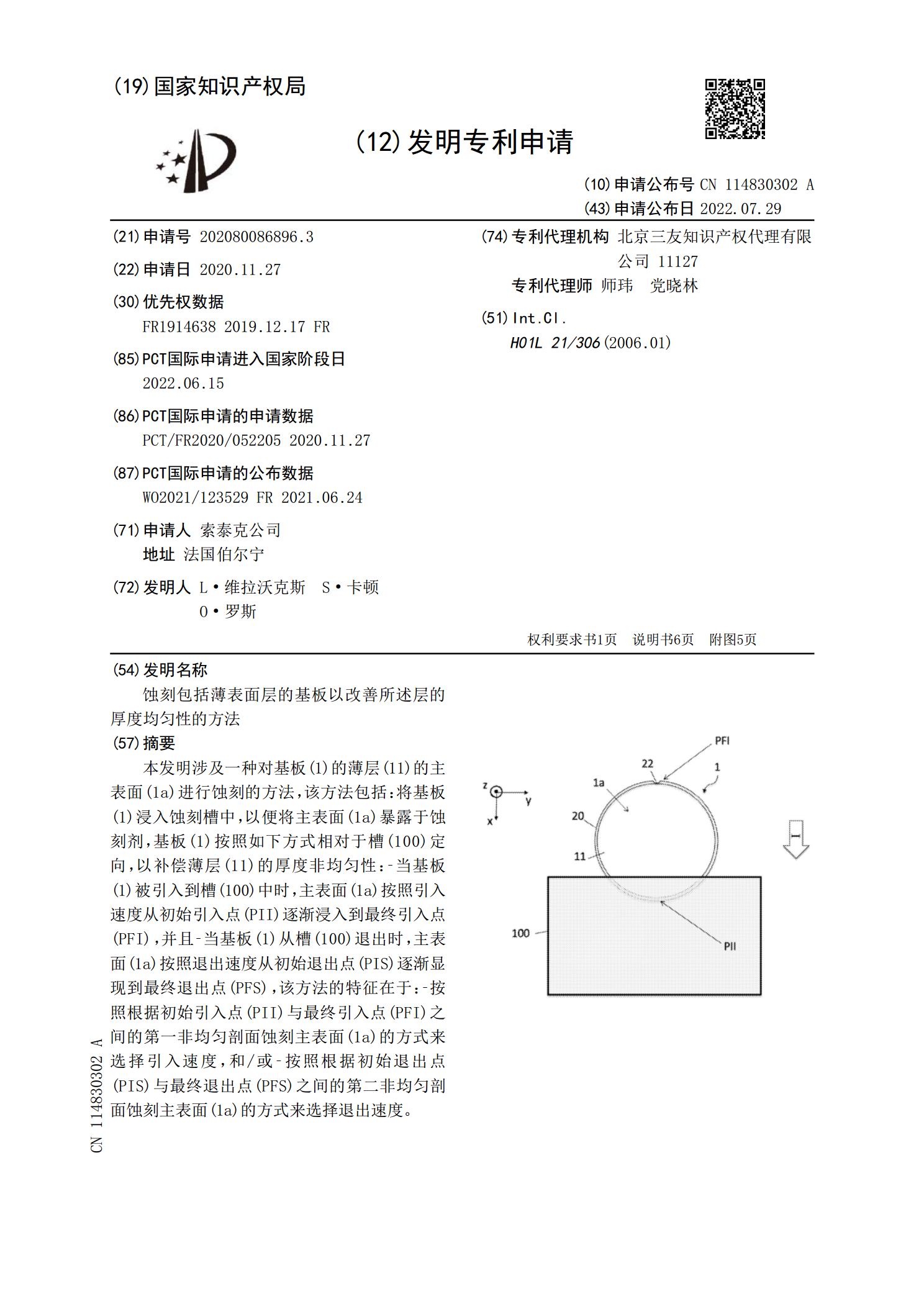

蚀刻包括薄表面层的基板以改善所述层的厚度均匀性的方法.pdf

本发明涉及一种对基板(1)的薄层(11)的主表面(1a)进行蚀刻的方法,该方法包括:将基板(1)浸入蚀刻槽中,以便将主表面(1a)暴露于蚀刻剂,基板(1)按照如下方式相对于槽(100)定向,以补偿薄层(11)的厚度非均匀性:?当基板(1)被引入到槽(100)中时,主表面(1a)按照引入速度从初始引入点(PII)逐渐浸入到最终引入点(PFI),并且?当基板(1)从槽(100)退出时,主表面(1a)按照退出速度从初始退出点(PIS)逐渐显现到最终退出点(PFS),该方法的特征在于:?按照根据初始引入点(PII

蚀刻包括薄表面层的基板以改善所述层的厚度均匀性的方法.pdf

本发明涉及一种对基板(1)的薄层(11)的主表面(1a)进行蚀刻的方法,该方法包括:将基板(1)浸入蚀刻槽中,以便将主表面(1a)暴露于蚀刻剂,基板(1)按照如下方式相对于槽(100)定向,以补偿薄层(11)的厚度非均匀性:?当基板(1)被引入到槽(100)中时,主表面(1a)按照引入速度从初始引入点(PII)逐渐浸入到最终引入点(PFI),并且?当基板(1)从槽(100)退出时,主表面(1a)按照退出速度从初始退出点(PIS)逐渐显现到最终退出点(PFS),该方法的特征在于:?按照根据初始引入点(PII

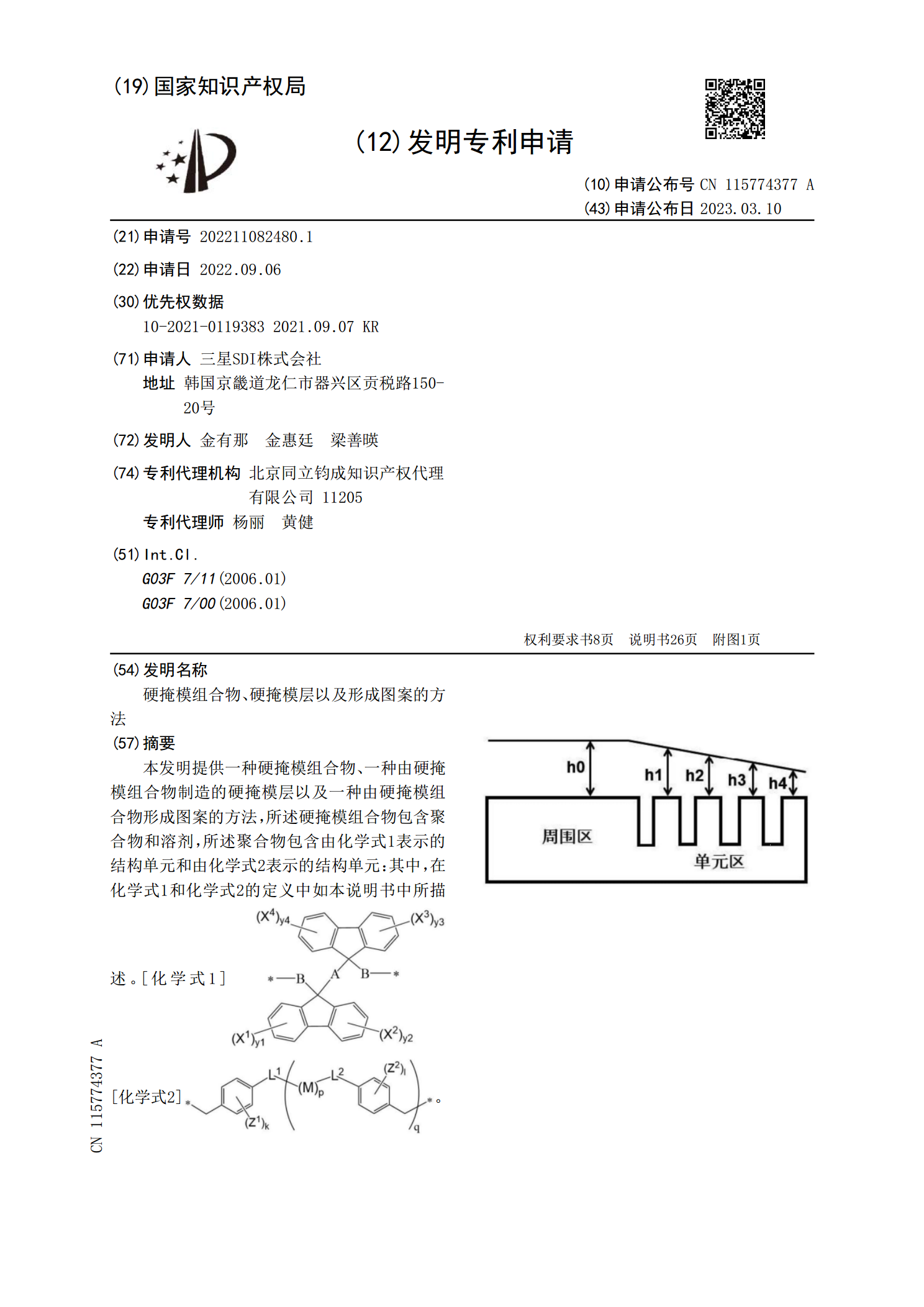

硬掩模组合物、硬掩模层以及形成图案的方法.pdf

本发明提供一种硬掩模组合物、一种由硬掩模组合物制造的硬掩模层以及一种由硬掩模组合物形成图案的方法,所述硬掩模组合物包含聚合物和溶剂,所述聚合物包含由化学式1表示的结构单元和由化学式2表示的结构单元:其中,在化学式1和化学式2的定义中如本说明书中所描述。[化学式1]