在集成电路制造期间蚀刻铜的方法.pdf

一吃****继勇

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

在集成电路制造期间蚀刻铜的方法.pdf

本发明揭露在集成电路制造期间蚀刻铜的方法。在一个示例实施例中,一种制造集成电路的方法包括:提供集成电路结构,该集成电路结构包括铜凸块结构以及位于该铜凸块结构下方并邻近该铜凸块结构的铜晶种层;以及利用湿式蚀刻化学相对该铜凸块结构选择性蚀刻该晶种层,该湿式蚀刻化学由体积百分比为约0.07至约0.36的H

一种蚀刻废液铜回收及蚀刻液再生方法.pdf

本发明公开了一种蚀刻废液铜回收及蚀刻液再生方法,包括以下步骤:步骤1:调节蚀刻废液中的铜元素浓度、氯离子浓度、碱度,其中铜元素浓度为75-80g/L,氯离子浓度为160-185g/L,Ph值为6-8;步骤2:将步骤1得到的溶液导入到电解槽中电解分离出固体铜粉,电解电流为40-42A温度35-40℃、时间11-13h,电解结束时,溶液中铜元素浓度为25-30g/L,氯离子浓度为160-185g/L,Ph值为6-8;步骤3:调节步骤2中电解后溶液中的各离子浓度和Ph值,得到可回收再用的蚀刻液,其中,铜元素浓

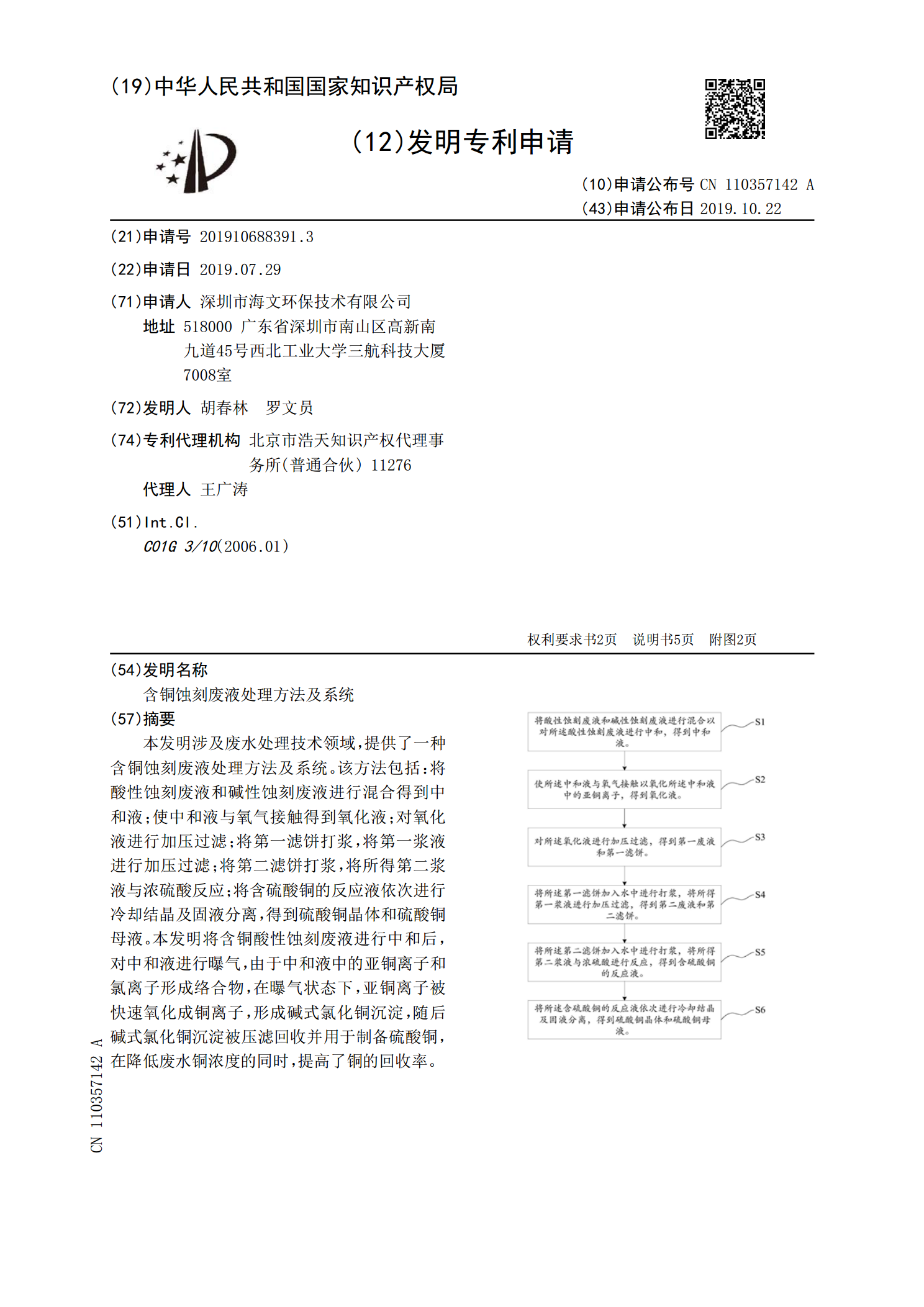

含铜蚀刻废液处理方法及系统.pdf

本发明涉及废水处理技术领域,提供了一种含铜蚀刻废液处理方法及系统。该方法包括:将酸性蚀刻废液和碱性蚀刻废液进行混合得到中和液;使中和液与氧气接触得到氧化液;对氧化液进行加压过滤;将第一滤饼打浆,将第一浆液进行加压过滤;将第二滤饼打浆,将所得第二浆液与浓硫酸反应;将含硫酸铜的反应液依次进行冷却结晶及固液分离,得到硫酸铜晶体和硫酸铜母液。本发明将含铜酸性蚀刻废液进行中和后,对中和液进行曝气,由于中和液中的亚铜离子和氯离子形成络合物,在曝气状态下,亚铜离子被快速氧化成铜离子,形成碱式氯化铜沉淀,随后碱式氯化铜沉

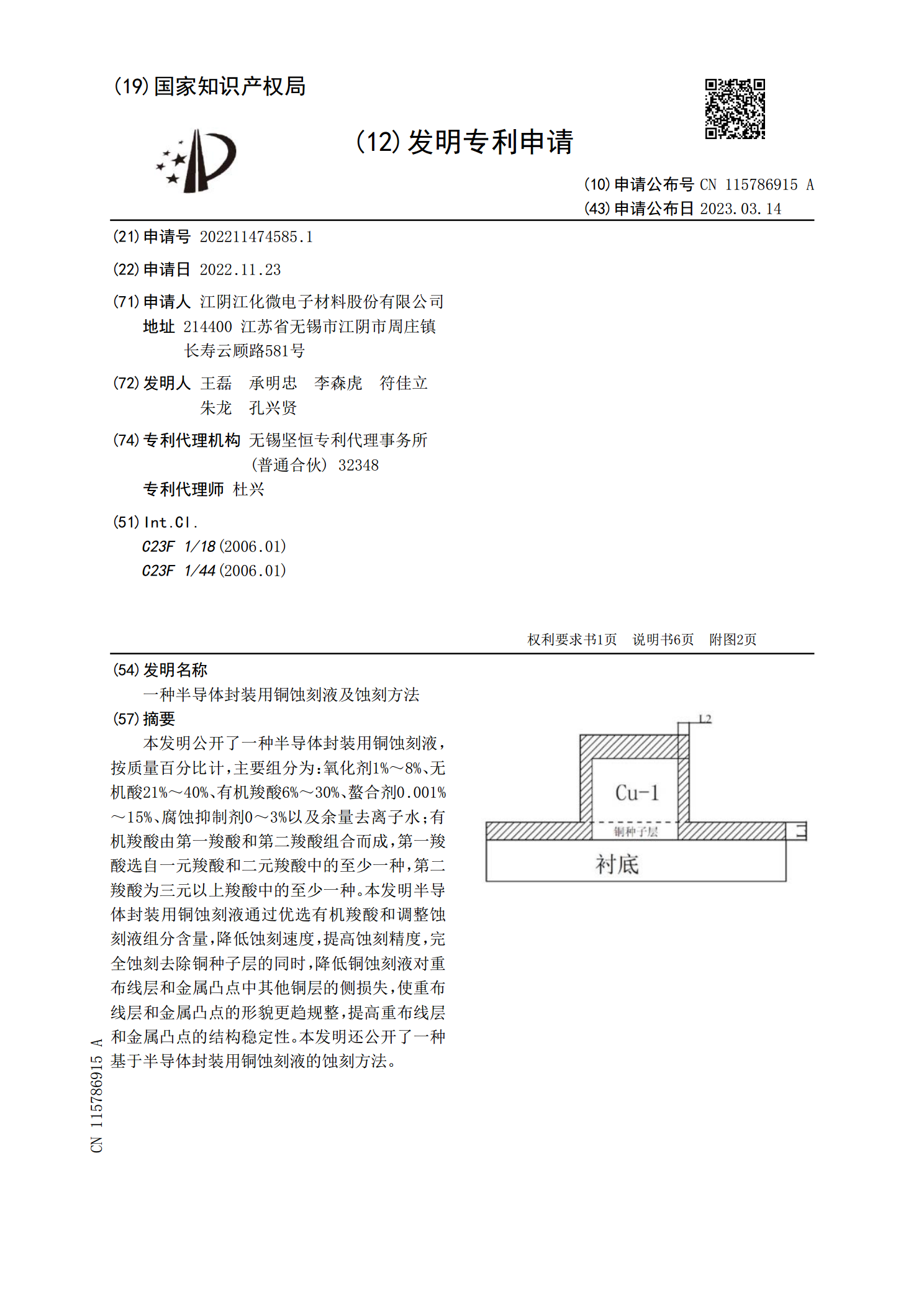

一种半导体封装用铜蚀刻液及蚀刻方法.pdf

本发明公开了一种半导体封装用铜蚀刻液,按质量百分比计,主要组分为:氧化剂1%~8%、无机酸21%~40%、有机羧酸6%~30%、螯合剂0.001%~15%、腐蚀抑制剂0~3%以及余量去离子水;有机羧酸由第一羧酸和第二羧酸组合而成,第一羧酸选自一元羧酸和二元羧酸中的至少一种,第二羧酸为三元以上羧酸中的至少一种。本发明半导体封装用铜蚀刻液通过优选有机羧酸和调整蚀刻液组分含量,降低蚀刻速度,提高蚀刻精度,完全蚀刻去除铜种子层的同时,降低铜蚀刻液对重布线层和金属凸点中其他铜层的侧损失,使重布线层和金属凸点的形貌更

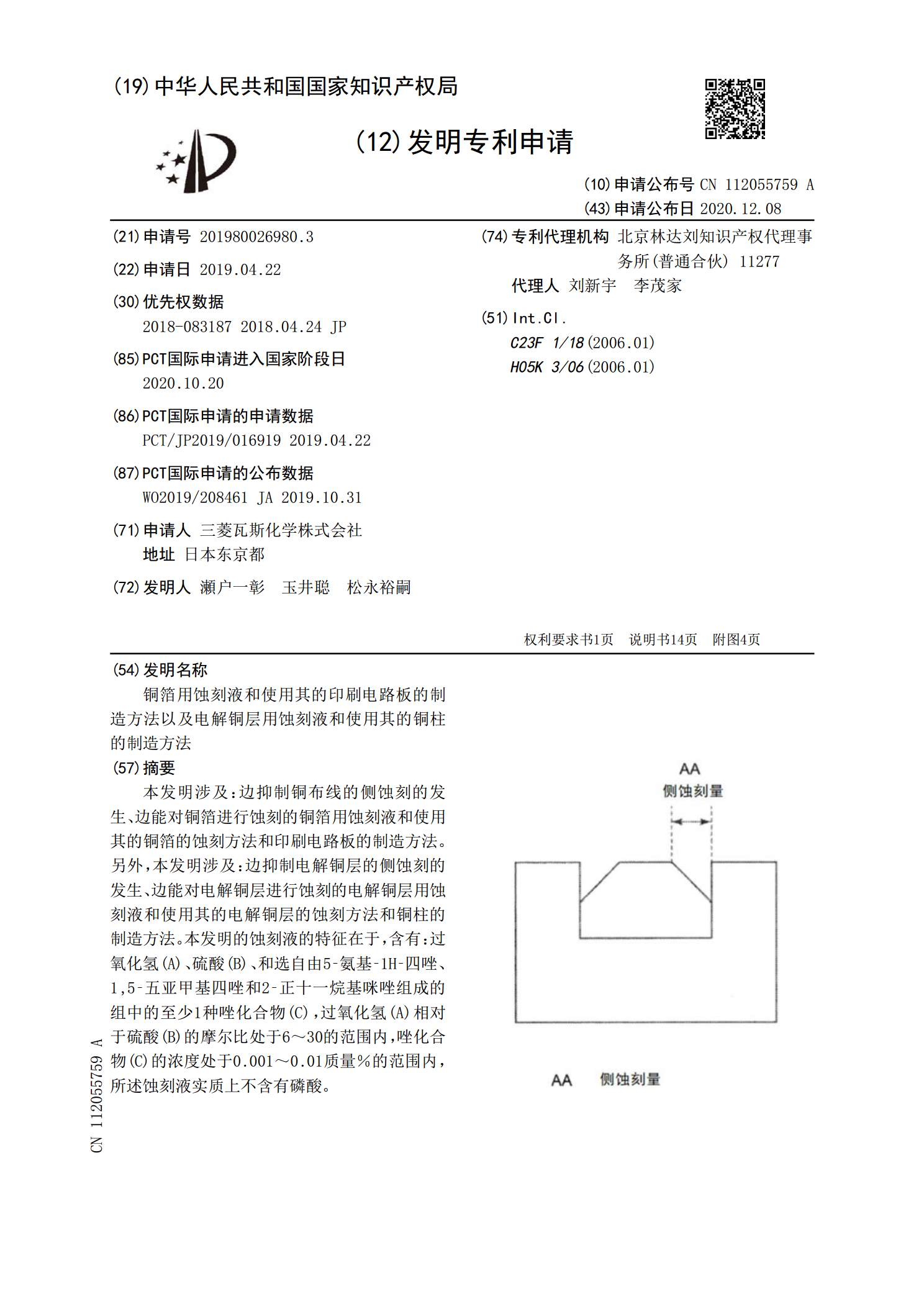

铜箔用蚀刻液和使用其的印刷电路板的制造方法以及电解铜层用蚀刻液和使用其的铜柱的制造方法.pdf

本发明涉及:边抑制铜布线的侧蚀刻的发生、边能对铜箔进行蚀刻的铜箔用蚀刻液和使用其的铜箔的蚀刻方法和印刷电路板的制造方法。另外,本发明涉及:边抑制电解铜层的侧蚀刻的发生、边能对电解铜层进行蚀刻的电解铜层用蚀刻液和使用其的电解铜层的蚀刻方法和铜柱的制造方法。本发明的蚀刻液的特征在于,含有:过氧化氢(A)、硫酸(B)、和选自由5‑氨基‑1H‑四唑、1,5‑五亚甲基四唑和2‑正十一烷基咪唑组成的组中的至少1种唑化合物(C),过氧化氢(A)相对于硫酸(B)的摩尔比处于6~30的范围内,唑化合物(C)的浓度处于0.0