一种减小米勒电容的MOSFET制造方法.pdf

灵波****ng

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种减小米勒电容的MOSFET制造方法.pdf

本发明公开了一种减小米勒电容的MOSFET制造方法,采用本方法制造的MOSFET,第二多晶硅(多晶硅栅)下方与外延层(漏端)之间的介质层包括第一氧化层、氮化硅和第三氧化层,而传统方法中多晶硅栅下方与漏端之间的介质层为单一的栅氧化层,显而易见,本方法制造的MOSFET的介质层厚度大于现有技术中的栅氧化层,介质层厚度越大对应的电容值越小,因此本发明的MOSFET的多晶硅栅底部与漏端之间的寄生电容比传统方法较小,降低了作为开关电路时的开关损耗,可适用于高频领域,具有更广的适用范围。

一种降低米勒电容的MOSFET制造方法.pdf

本发明公开了一种降低米勒电容的MOSFET制造方法,采用本方法制造的MOSFET,第二多晶硅(多晶硅栅)下方与外延层(漏端)之间的介质层包括第一氧化层、氮化硅和第二氧化层,而传统方法中多晶硅栅下方与漏端之间的介质层为单一的栅氧化层,显而易见,本方法制造的MOSFET的介质层厚度大于现有技术中的栅氧化层,介质层厚度越大对应的电容值越小,因此本发明的MOSFET的多晶硅栅底部与漏端之间的寄生电容比传统方法较小,降低了作为开关电路时的开关损耗,可适用于高频领域,具有更广的适用范围。

一种减小米勒电容的新型RC-IGBT结构.pdf

本发明提供了一种减小米勒电容的新型RC‑IGBT结构,该结构在常规RC‑IGBT结构的基础上,在沟槽栅下方对应的P型集电区与集电极金属之间增添SiO

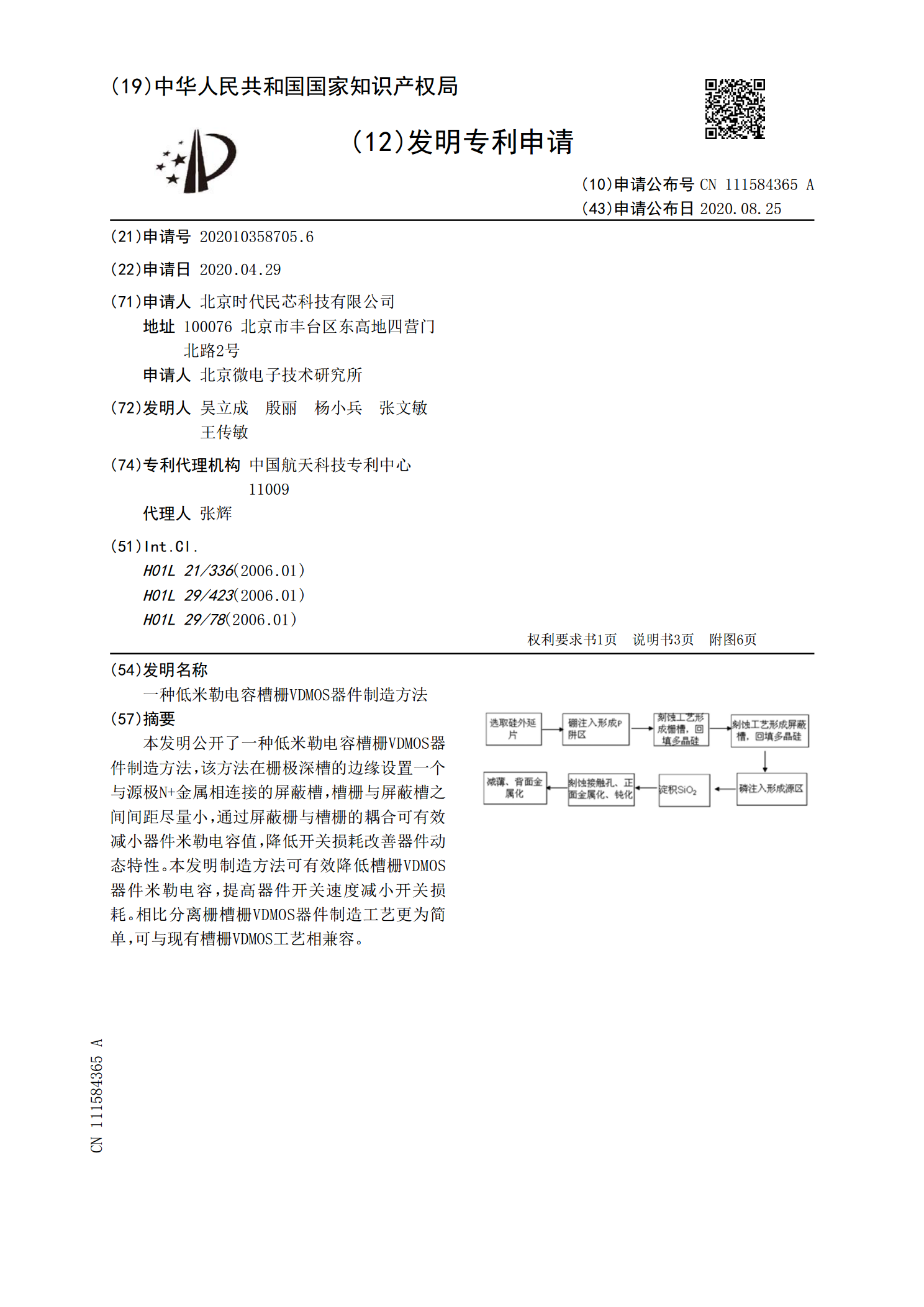

一种低米勒电容槽栅VDMOS器件制造方法.pdf

本发明公开了一种低米勒电容槽栅VDMOS器件制造方法,该方法在栅极深槽的边缘设置一个与源极N+金属相连接的屏蔽槽,槽栅与屏蔽槽之间间距尽量小,通过屏蔽栅与槽栅的耦合可有效减小器件米勒电容值,降低开关损耗改善器件动态特性。本发明制造方法可有效降低槽栅VDMOS器件米勒电容,提高器件开关速度减小开关损耗。相比分离栅槽栅VDMOS器件制造工艺更为简单,可与现有槽栅VDMOS工艺相兼容。

一种MOSFET及其制造方法.pdf

本发明涉及半导体器件技术领域,公开了一种MOSFET及其制造方法,通过将MOSFET的栅极多晶硅层从中间区域引至边缘,然后通过第四电极与栅极金属电连接,而且由于第二栅极多晶硅层的底部设有第三氧化层、第二栅极多晶硅层的周围设有氧化层,能够使第二栅极多晶硅层承受漏极电压,不用开设相应的接口沟槽以及在接口沟槽中设置提供保护作用的氧化层,这样MOSFET在刻蚀时由于第一沟槽至第M沟槽的整体宽度差异小于0.1um.不用担心有颗粒残留在沟槽中。