低输入电容的沟槽型IGBT器件及制备方法.pdf

努力****恨风

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

低输入电容的沟槽型IGBT器件及制备方法.pdf

本发明涉及一种低输入电容的沟槽型IGBT器件及制备方法。其对任一元胞,均包括两个呈长条状的元胞沟槽,在沿元胞沟槽的长度方向上,在元胞沟槽内设置若干槽内发射极导电多晶硅,所述槽内发射极导电多晶硅从元胞沟槽的槽口向元胞沟槽的底部方向延伸,且槽内发射极导电多晶硅通过多晶硅间介质层所在区域的栅极导电多晶硅绝缘隔离;在元胞沟槽间相互邻近的外侧壁上设置第一导电类型源区,所述第一导电类型源区沿元胞沟槽的长度方向分布,槽内发射极导电多晶硅在元胞沟槽内的底部位于第一导电类型源区的底部的下方。本发明在不影响米勒电容下,降低了

沟槽型IGBT器件的制作方法、沟槽型IGBT器件.pdf

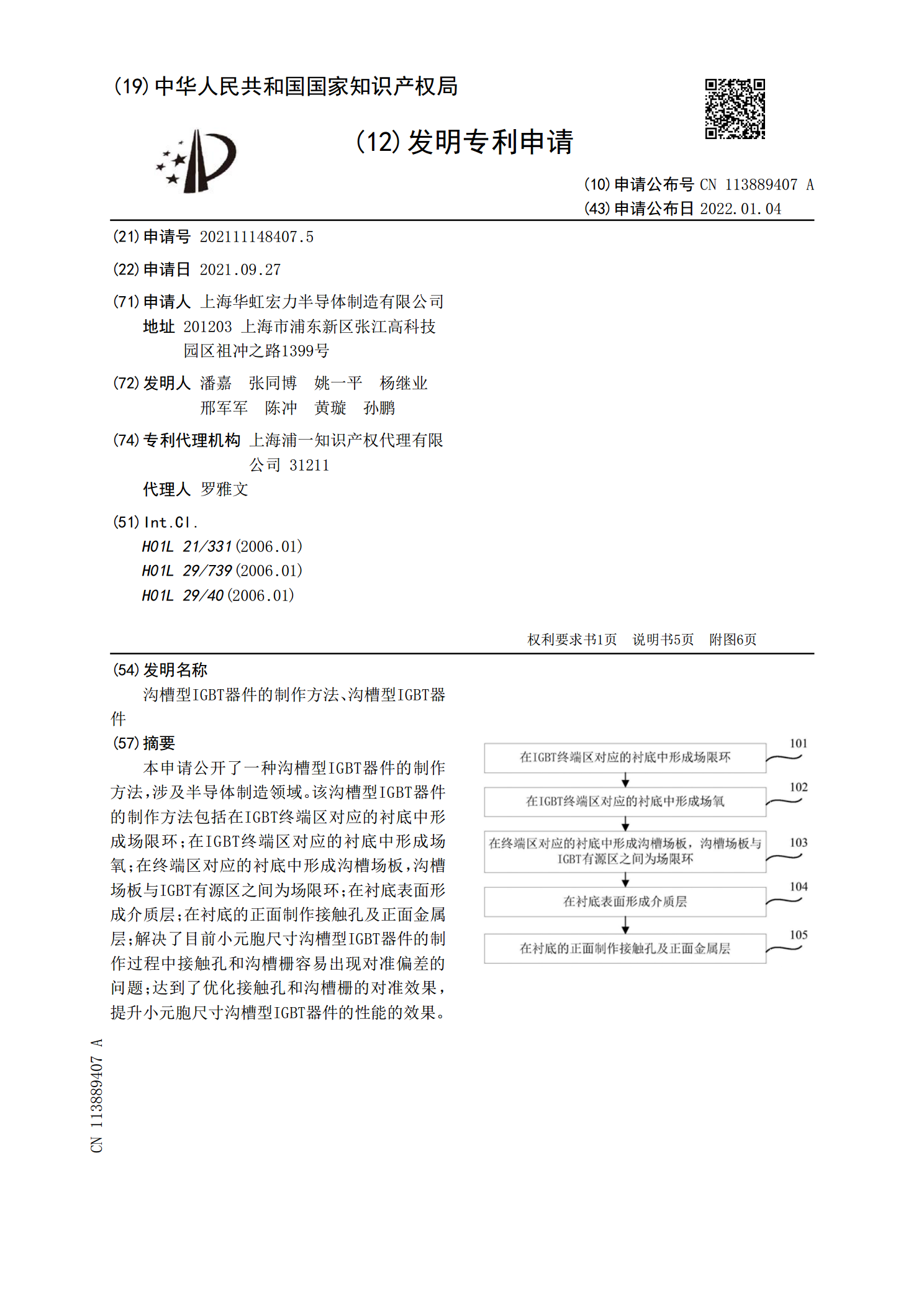

本申请公开了一种沟槽型IGBT器件的制作方法,涉及半导体制造领域。该沟槽型IGBT器件的制作方法包括在IGBT终端区对应的衬底中形成场限环;在IGBT终端区对应的衬底中形成场氧;在终端区对应的衬底中形成沟槽场板,沟槽场板与IGBT有源区之间为场限环;在衬底表面形成介质层;在衬底的正面制作接触孔及正面金属层;解决了目前小元胞尺寸沟槽型IGBT器件的制作过程中接触孔和沟槽栅容易出现对准偏差的问题;达到了优化接触孔和沟槽栅的对准效果,提升小元胞尺寸沟槽型IGBT器件的性能的效果。

能降低米勒电容的沟槽型IGBT器件.pdf

本发明涉及一种能降低米勒电容的沟槽型IGBT器件,其通过浮空第二导电类型区能提高IGBT发射极侧的载流子浓度,浮空第二导电类型区结深大于元胞沟槽的深度,浮空第二导电类型区还包覆元胞沟槽的部分底部,降低元胞沟槽角落处的电场,从而提高IGBT器件的耐压。在浮空第二导电类型区内设置一个或多个浮空区沟槽,浮空区沟槽的深度小于所述浮空第二导电类型区的结深,浮空区沟槽的宽度不小于元胞沟槽的宽度,浮空区沟槽内的浮空沟槽多晶硅与发射极金属欧姆接触,从而屏蔽元胞栅极多晶硅的电压变化,有效地降低了米勒电容Cgc,从而达到提高

新型沟槽IGBT半导体器件及其制备方法.pdf

本发明提供了一种新型沟槽IGBT半导体器件及其制备方法,包括衬底,以及在所述衬底上依次外延形成的基区、阱区、源区,并且在所述基区和所述阱区中还设有多个真沟槽栅单元,以及设置于相邻所述真沟槽栅单元之间的假沟槽栅单元,其中,每个所述真沟槽栅单元两侧分别设有源区,并且在每个所述真沟槽栅单元和每个所述假沟槽栅单元底部还设有底部掺杂区。本发明能够实现局部超结结构以提高击穿电压,并能够实现结构厚度的降低以减小压降,从而能够减小电容面积和密勒电容,保证器件的性能。

沟槽型功率器件的制备方法.pdf

本发明提供了一种沟槽型功率器件的制备方法,包括:提供基底,所述基底包括器件单元区、电极连接区及终端区,所述器件单元区及所述电极连接区中分别形成有若干第一沟槽及若干第二沟槽,所述第一沟槽及所述第二沟槽的内壁上形成有第一氧化层;在所述基底的电极连接区及所述基底的终端区上形成图形化的光刻胶层,对所述第一多晶硅层进行刻蚀以使所述第一多晶硅层的顶部低于所述第一沟槽的顶部;对所述第一沟槽中的第一氧化层进行湿法刻蚀以使所述第一沟槽中的第一氧化层的顶部低于所述第一多晶硅层的顶部;本发明避免了多晶硅残留导致器件短路,提高器