一种铜互连结构及其制造方法.pdf

如灵****姐姐

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种铜互连结构及其制造方法.pdf

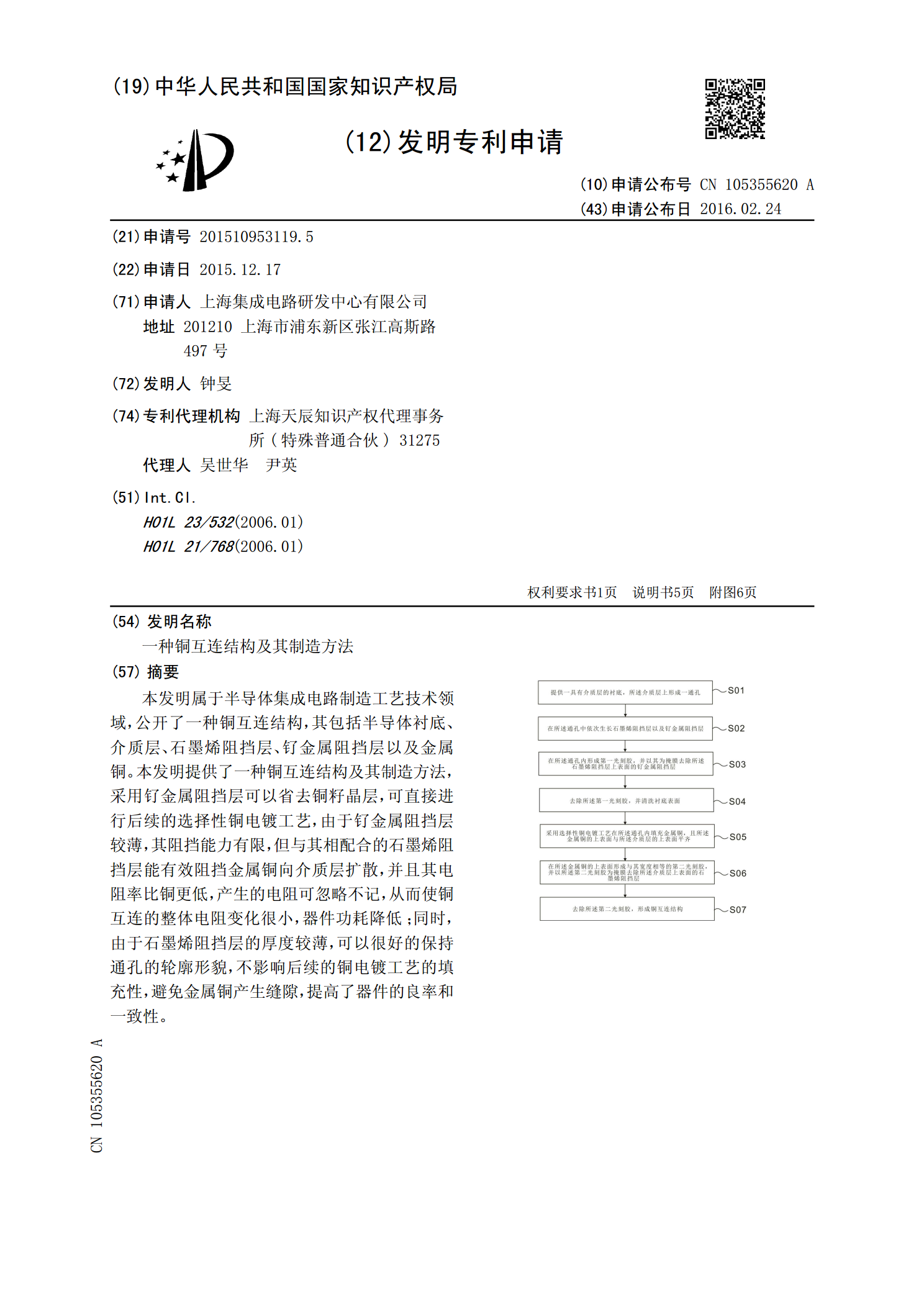

本发明属于半导体集成电路制造工艺技术领域,公开了一种铜互连结构,其包括半导体衬底、介质层、石墨烯阻挡层、钌金属阻挡层以及金属铜。本发明提供了一种铜互连结构及其制造方法,采用钌金属阻挡层可以省去铜籽晶层,可直接进行后续的选择性铜电镀工艺,由于钌金属阻挡层较薄,其阻挡能力有限,但与其相配合的石墨烯阻挡层能有效阻挡金属铜向介质层扩散,并且其电阻率比铜更低,产生的电阻可忽略不记,从而使铜互连的整体电阻变化很小,器件功耗降低;同时,由于石墨烯阻挡层的厚度较薄,可以很好的保持通孔的轮廓形貌,不影响后续的铜电镀工艺的填

一种空气隙/铜互连结构的制造方法.pdf

一种空气隙/铜互连结构的制造方法,其包括提供一半导体衬底,先在半导体衬底上完成CMOS器件前道工艺,接着在半导体衬底上形成常规的第一介质/铜互连结构;对常规第一介质/铜互连结构在含氮的氛围中进行表面处理,在铜互连线表面形成一层铜的含氮化合物;采用刻蚀设备刻蚀铜互连线中间的第一介质;其中,在刻蚀第一介质过程中采用氟基气体和氧基气体进行刻蚀,铜的含氮化合物层保护铜互连线没有暴露在刻蚀气体氛围中;采用湿法药液去除残留光刻胶并清洗;淀积第二介质以形成空气隙/铜互连结构。

一种铜互连层的制造方法.pdf

本发明提供一种铜互连层的制造方法,在衬底上形成介质层以及介质层中镶嵌的铜互连层,而后进行铜清洁工艺,在氮气和氢气的气氛中进行清洁,以利用氮气的轰击力,清除介质层表面的铜残留。该方法在氮气和氢气的气氛中,利用氢气的还原作用,将介质层表面残留的铜离子还原为铜,而后利用氮气的轰击力去除介质层表面的铜残留,实现介质层上的铜清洁,避免介质层上的铜残留对器件性能的影响。

一种微米级单晶铜互连结构及其制备方法.pdf

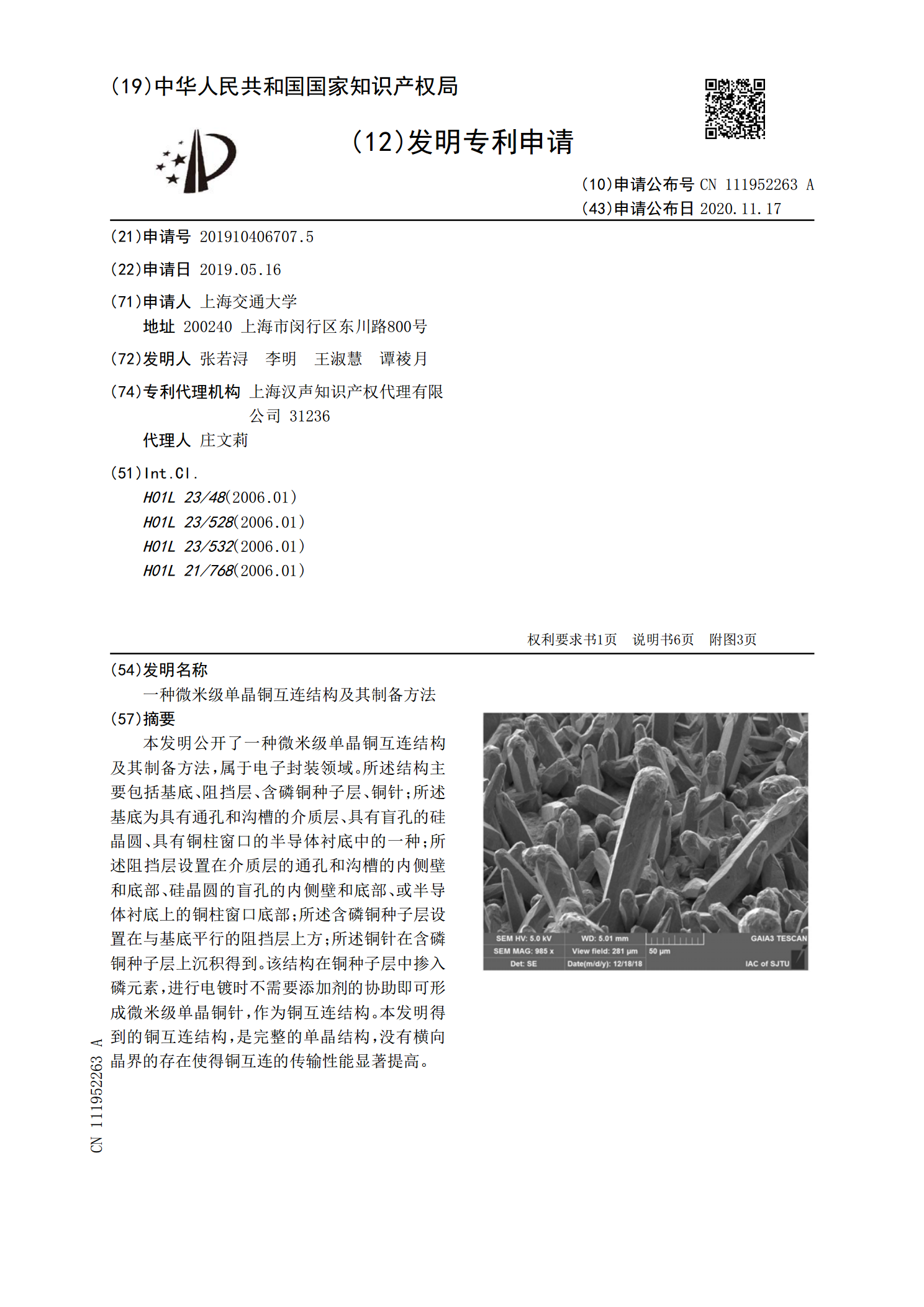

本发明公开了一种微米级单晶铜互连结构及其制备方法,属于电子封装领域。所述结构主要包括基底、阻挡层、含磷铜种子层、铜针;所述基底为具有通孔和沟槽的介质层、具有盲孔的硅晶圆、具有铜柱窗口的半导体衬底中的一种;所述阻挡层设置在介质层的通孔和沟槽的内侧壁和底部、硅晶圆的盲孔的内侧壁和底部、或半导体衬底上的铜柱窗口底部;所述含磷铜种子层设置在与基底平行的阻挡层上方;所述铜针在含磷铜种子层上沉积得到。该结构在铜种子层中掺入磷元素,进行电镀时不需要添加剂的协助即可形成微米级单晶铜针,作为铜互连结构。本发明得到的铜互连结

一种无引线的全铜互连封装结构及其制备方法.pdf

本发明涉及一种无引线的全铜互连封装结构及其制备方法;制备步骤为:在基板的特定位置上覆设含微纳米金属颗粒的膏体,形成贴片层;在贴片层上贴装芯片,采用烧结工艺,实现芯片与基板互连;在基板上制备围设芯片和贴片层外围的绝缘层;在芯片和绝缘层上端面、绝缘层的外围以及与绝缘层相邻的基板特定区域连续覆设含微纳米金属颗粒的膏体,采用烧结工艺对覆设的含微纳米金属颗粒的膏体进行烧结,形成与芯片和基板互连的互连层;通过无引线的全铜互连封装结构制备方法的提出以解决现有采用引线为铜线,铜线的线材硬度较大,键合时所需的键合压力较大导