一种空气隙/铜互连结构的制造方法.pdf

猫巷****提格

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种空气隙/铜互连结构的制造方法.pdf

一种空气隙/铜互连结构的制造方法,其包括提供一半导体衬底,先在半导体衬底上完成CMOS器件前道工艺,接着在半导体衬底上形成常规的第一介质/铜互连结构;对常规第一介质/铜互连结构在含氮的氛围中进行表面处理,在铜互连线表面形成一层铜的含氮化合物;采用刻蚀设备刻蚀铜互连线中间的第一介质;其中,在刻蚀第一介质过程中采用氟基气体和氧基气体进行刻蚀,铜的含氮化合物层保护铜互连线没有暴露在刻蚀气体氛围中;采用湿法药液去除残留光刻胶并清洗;淀积第二介质以形成空气隙/铜互连结构。

一种形成空气隙/铜互连的方法.pdf

一种形成空气隙/铜互连的方法,其包括提供一半导体衬底,先在半导体衬底上完成CMOS器件前道工艺,接着在半导体衬底上形成常规的第一介质/铜互连结构;对常规第一介质/铜互连结构在含氧的氛围中进行表面处理,在铜互连线表面形成一层铜的氧化物;采用刻蚀设备刻蚀铜互连线中间的第一介质;其中,在刻蚀第一介质过程中采用氟基气体和氧基气体进行刻蚀,铜的氧化物保护所述铜互连线没有暴露在刻蚀气体氛围中;还原铜互连线表面的铜氧化物,即使铜互连线表面的铜氧化物重新转化为金属铜;采用湿法药液去除残留光刻胶并清洗;淀积第二介质以形成空

一种形成空气隙/铜互连的工艺方法.pdf

一种形成空气隙/铜互连的工艺方法,其包括提供一半导体衬底,先在半导体衬底上完成CMOS器件前道工艺,接着在半导体衬底上形成常规的第一介质/铜互连结构;采用刻蚀设备刻蚀铜互连线中间的第一介质;其中,在刻蚀第一介质过程中采用氟基气体和氧基气体进行刻蚀,铜互连线暴露在刻蚀气体氛围中,铜互连线铜表面会产生具有一定厚度的铜氧化物副产品;还原铜互连线表面的铜氧化物副产品,即使铜互连线表面的铜氧化物副产品重新转化为金属铜;采用湿法药液去除残留光刻胶并清洗;淀积第二介质以形成空气隙/铜互连结构。

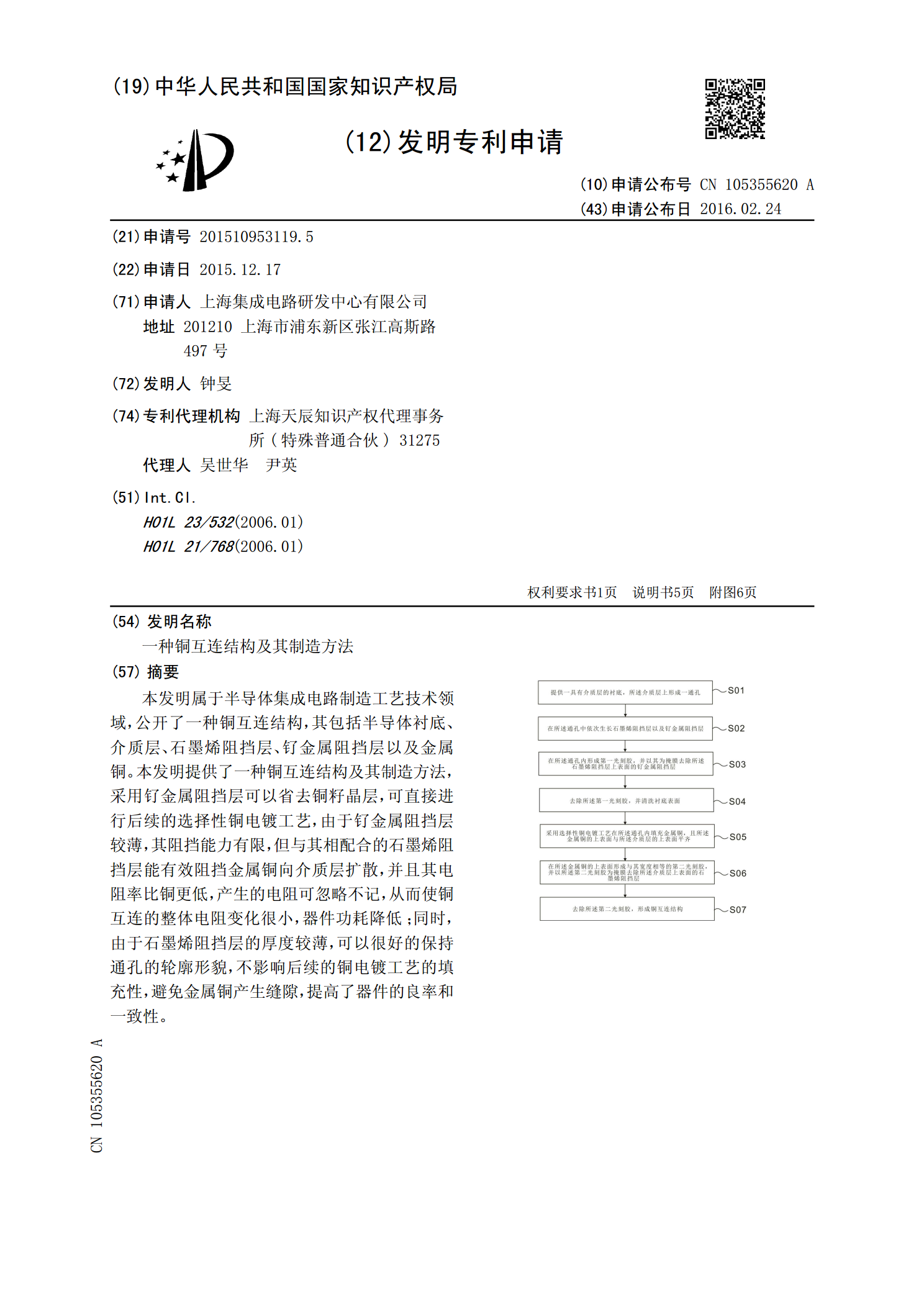

一种铜互连结构及其制造方法.pdf

本发明属于半导体集成电路制造工艺技术领域,公开了一种铜互连结构,其包括半导体衬底、介质层、石墨烯阻挡层、钌金属阻挡层以及金属铜。本发明提供了一种铜互连结构及其制造方法,采用钌金属阻挡层可以省去铜籽晶层,可直接进行后续的选择性铜电镀工艺,由于钌金属阻挡层较薄,其阻挡能力有限,但与其相配合的石墨烯阻挡层能有效阻挡金属铜向介质层扩散,并且其电阻率比铜更低,产生的电阻可忽略不记,从而使铜互连的整体电阻变化很小,器件功耗降低;同时,由于石墨烯阻挡层的厚度较薄,可以很好的保持通孔的轮廓形貌,不影响后续的铜电镀工艺的填

一种铜互连层的制造方法.pdf

本发明提供一种铜互连层的制造方法,在衬底上形成介质层以及介质层中镶嵌的铜互连层,而后进行铜清洁工艺,在氮气和氢气的气氛中进行清洁,以利用氮气的轰击力,清除介质层表面的铜残留。该方法在氮气和氢气的气氛中,利用氢气的还原作用,将介质层表面残留的铜离子还原为铜,而后利用氮气的轰击力去除介质层表面的铜残留,实现介质层上的铜清洁,避免介质层上的铜残留对器件性能的影响。