半导体器件物理ppt课件.ppt

天马****23

亲,该文档总共34页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体器件物理ppt课件.ppt

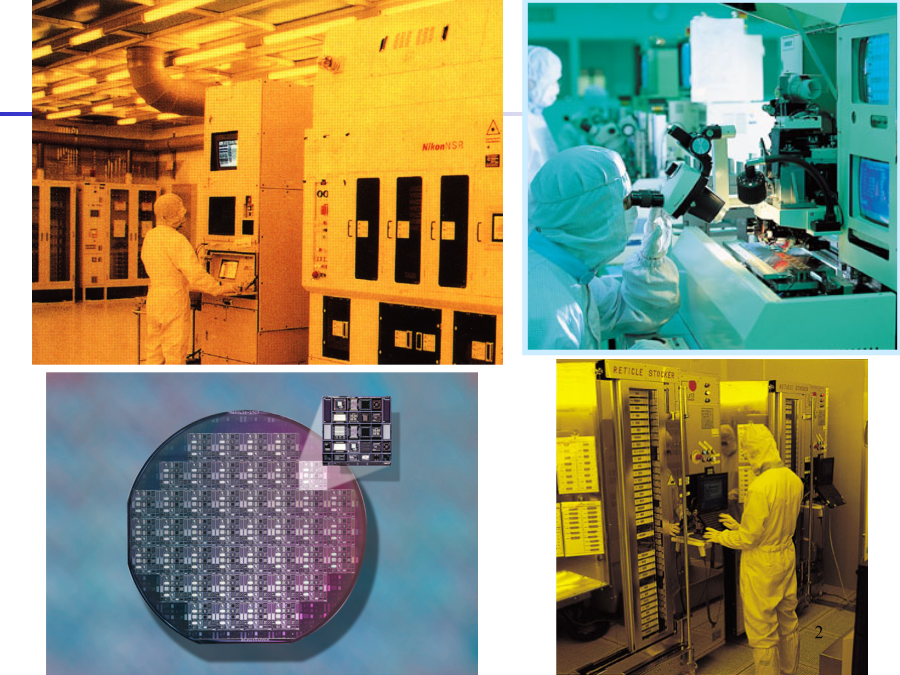

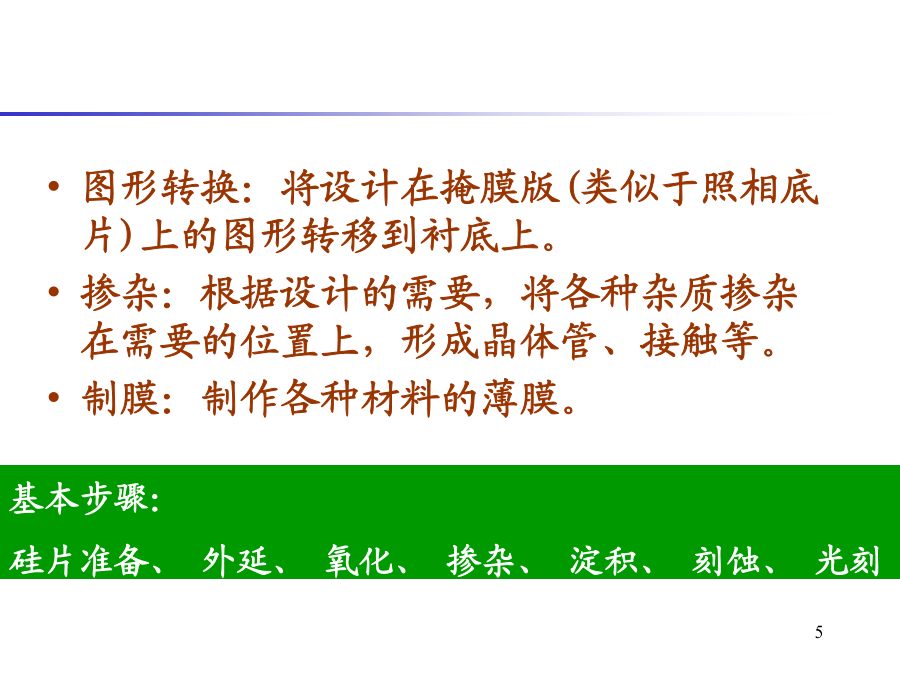

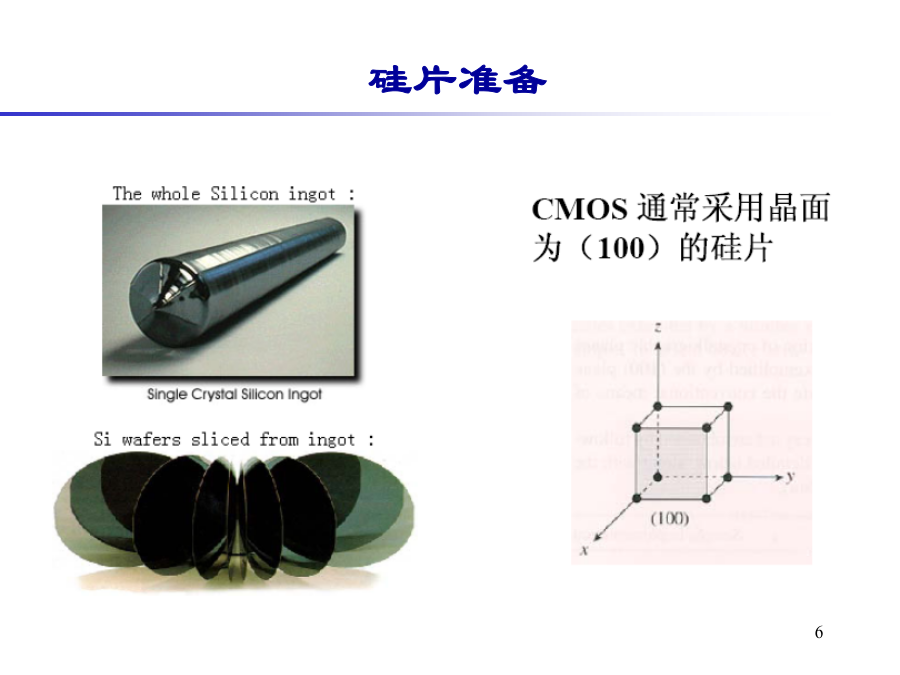

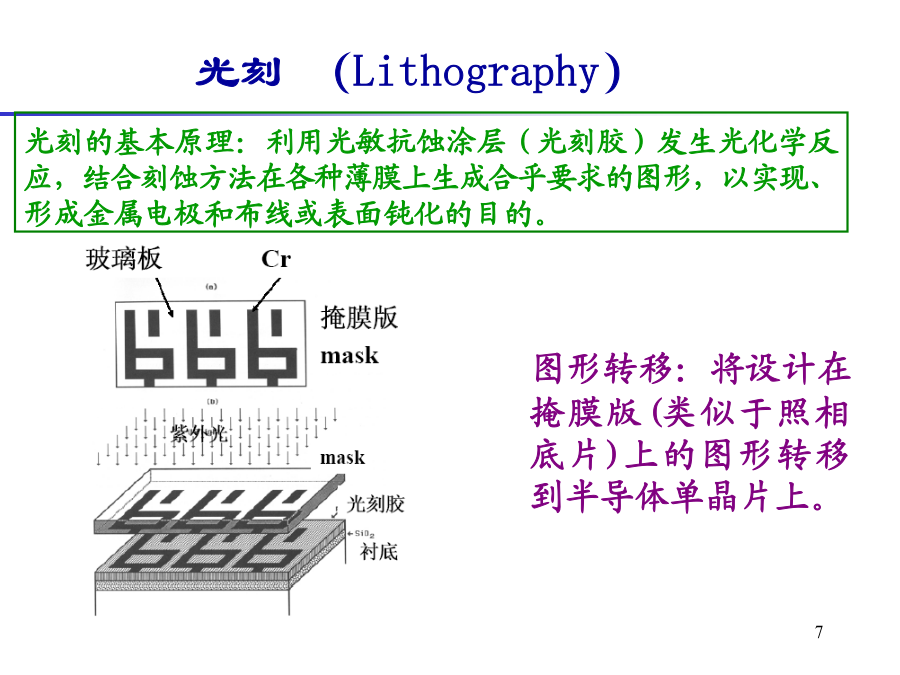

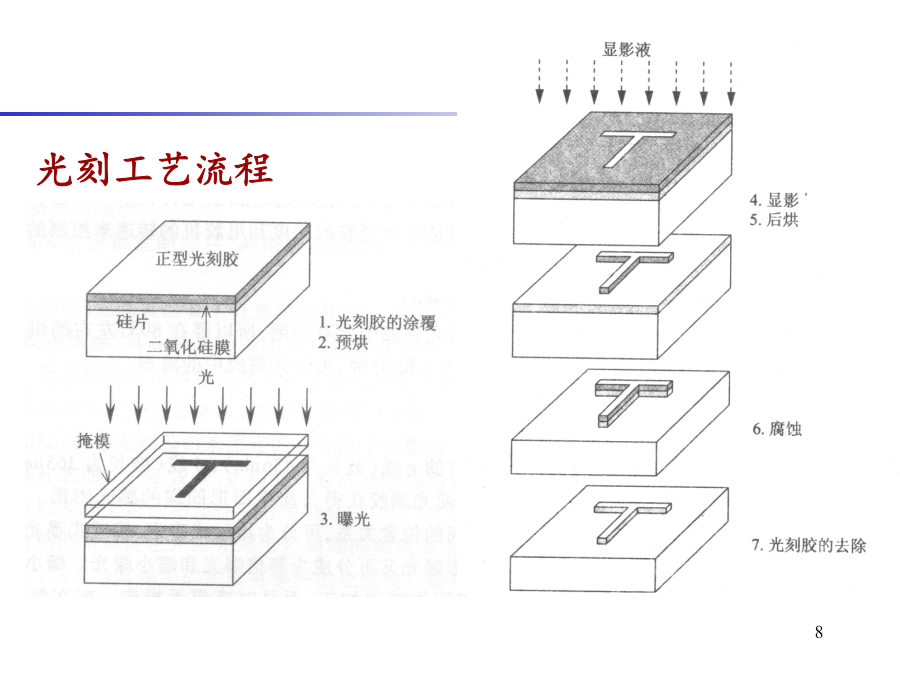

第四章集成电路制造工艺2芯片制造过程图形转换:将设计在掩膜版(类似于照相底片)上的图形转移到衬底上。掺杂:根据设计的需要,将各种杂质掺杂在需要的位置上,形成晶体管、接触等。制膜:制作各种材料的薄膜。硅片准备光刻(Lithography)光刻工艺流程光刻三要素:光刻胶、掩膜版和光刻机–光刻胶又叫光致抗蚀剂,它是由光敏化合物、基体树脂和有机溶剂等混合而成的胶状液体。–光刻胶受到特定波长光线的作用后,导致其化学结构发生变化,使光刻胶在某种特定溶液中的溶解特性改变。正胶(曝光后可溶):分辨率高,在超大规模集成电路

半导体物理与器件ppt课件.pdf

课程主要内容固体晶格结构:第一章量子力学:第二章~第三章半导体物理:第四章~第六章半导体器件:第七章~第十三章1绪论什么是半导体按固体的导电能力区分,可以区分为导体、半导体和绝缘体表1.1导体、半导体和绝缘体的电阻率范围材料导体半导体绝缘体电阻率ρ(Ωcm)<10-310-3~109>1092绪论半导体具有一些重要特性,主要包括:温度升高使半导体导电能力增强,电阻率下降如室温附近的纯硅(Si),温度每增加8℃,电阻率相应地降低50%左右微量杂质含量可以显著改变半导体的导电能力以纯硅中每100

半导体器件物理专题ppt课件.ppt

HEMTHEMT简介一.HEMT简介一.HEMT简介二.两种体系的HEMT制作工序:1.在半绝缘GaAs衬底上生长GaAs缓冲层(约0.5μm)2.高纯GaAs层(约60nm)3.n型AlGaAs(铝镓砷)层(约60nm)4.n型GaAs层(厚约50nm)5.台面腐蚀隔离有源区6.制作Au/Ge合金的源、漏欧姆接触电极7.干法选择腐蚀去除栅极位置n型GaAs层8.淀积Ti/Pt/Au栅电极。7图2GaAsHEMT中2-DEG在低温下HEMT的特性将发生退化,主要是由于n-AlGaAs层存在一种所谓DX中心

现代半导体器件物理与工艺ppt课件.ppt

图形曝光与光刻图形曝光与刻蚀光学图形曝光-洁净室光刻机掩模版抗蚀剂图案转移分辨率增加技术新一代图形曝光技术电子束图形曝光SCALPEL电子束抗蚀剂邻近效应极远紫外光图形曝光(EUV)X射线图形曝光(XRL)离子束图形曝光不同图形曝光方法的比较湿法化学腐蚀(WCE)硅的腐蚀二氧化硅的腐蚀氮化硅与多晶硅的腐蚀铝腐蚀砷化镓的腐蚀干法刻蚀干法刻蚀基本等离子体理论刻蚀机制、等离子体探测与终点的控制等离子体探测终点控制反应等离子体刻蚀技术与设备反应离子刻蚀(RIE)电子回旋共振(ECR)等离子体刻蚀机其他高密度等离子

半导体器件基础ppt课件.ppt

第一章半导体器件基础1.1半导体的基本知识本征半导体的共价键结构这一现象称为本征激发,也称热激发。可见本征激发同时产生电子空穴对。外加能量越高(温度越高),产生的电子空穴对越多。自由电子带负电荷电子流二.杂质半导体N型半导体在本征半导体中掺入三价杂质元素,如硼、镓等。杂质半导体的示意图内电场E动画演示2.PN结的单向导电性(2)加反向电压——电源正极接N区,负极接P区PN结加正向电压时,具有较大的正向扩散电流,呈现低电阻,PN结导通;PN结加反向电压时,具有很小的反向漂移电流,呈现高电阻,PN结截止。由此