电平异步时序逻辑电路分析课件.pptx

快乐****蜜蜂

亲,该文档总共18页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

电平异步时序逻辑电路分析课件.pptx

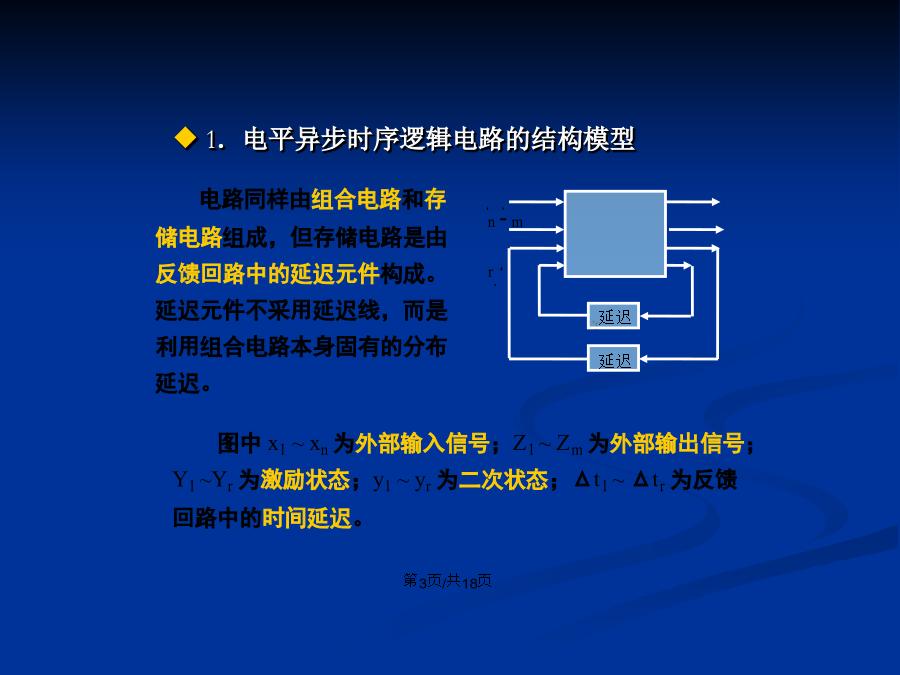

会计学异步时序逻辑的分类:(1)电平型异步时序逻辑电路:触发器的翻转受触发信号的电平高低控制,接收作用的时间长;(2)脉冲型异步逻辑时序电路:触发器的翻转仅在触发信号的有关跳变沿发生,接收作用的时间短,较易把握。信号在短时间内发生两次变化称为脉冲,若高电平持续时间较长称为电平,因此,电平是脉冲的一种特定形式。5.3.1电平异步时序逻辑电路的特点1.电平异步时序逻辑电路的结构模型电平异步时序逻辑电路结构模型特点:⑴电路输出状态的改变是由输入电位x的变化直接引起。⑵二次状态y是激励状态Y经Δt延迟后的“重现”

53 异步时序逻辑电路的分析.docx

异步时序逻辑电路的分析一.分析的目的:得出时序电路的逻辑功能。二.分析的方法(步骤):1、写方程式:(1)时钟方程;(2)输出方程;(3)驱动方程;(4)状态方程。2、列状态表;3、画状态转换图;4、画时序图;5、逻辑功能说明;6、检查电路能否自启动。注意:异步时序电路的状态改变时,电路中要更新状态的触发器,有的先翻转,有的后翻转,是异步进行的。因为在这种时序电路中,有的触发器的信号就是输入时钟脉冲,有的触发器则不是,而是其他触发器的输出。异步时序电路的分析举例例1试分析图示的时序电路的逻辑功能。解:(1

异步时序逻辑电路分析方法的研究.docx

异步时序逻辑电路分析方法的研究异步时序逻辑电路分析方法的研究随着半导体技术的发展,集成电路的功能越来越强大,数据交换和信息处理速度也在不断提高。异步时序逻辑电路是其中一种重要的电路结构,它能够在电路稳定性和可靠性方面具有优势。本文将对异步时序逻辑电路的基础原理和分析方法进行探讨。一、异步时序逻辑电路基础原理异步时序逻辑电路是利用信号的时序关系来实现函数计算的电路结构,同时不依靠时钟信号来保证数据的同步。异步时序逻辑电路中,相邻的逻辑模块之间存在数据传输和状态交换的关系,这种关系是由控制信号实现的。异步时序

异步时序逻辑电路.ppt

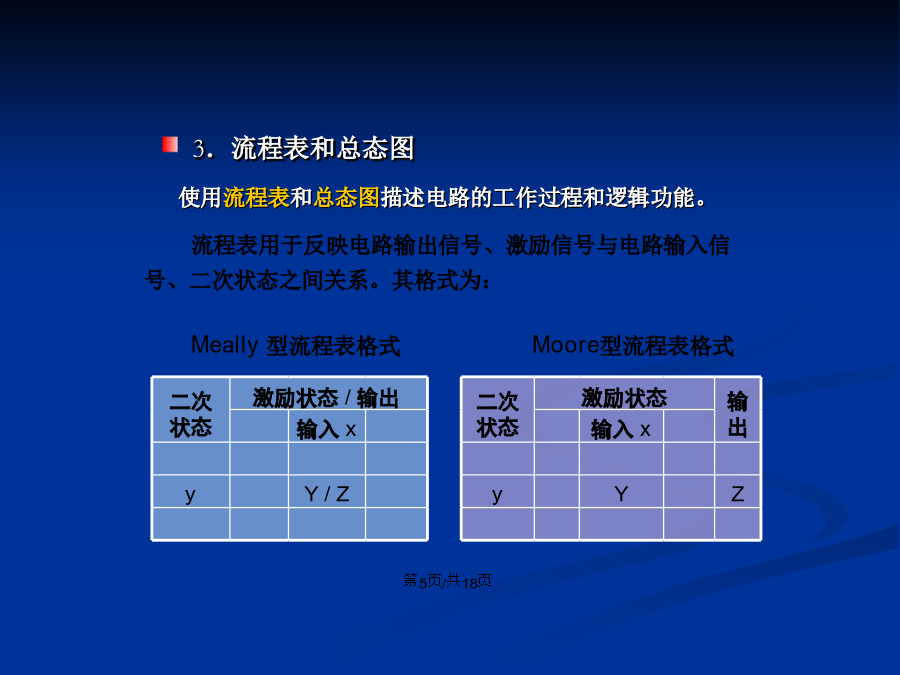

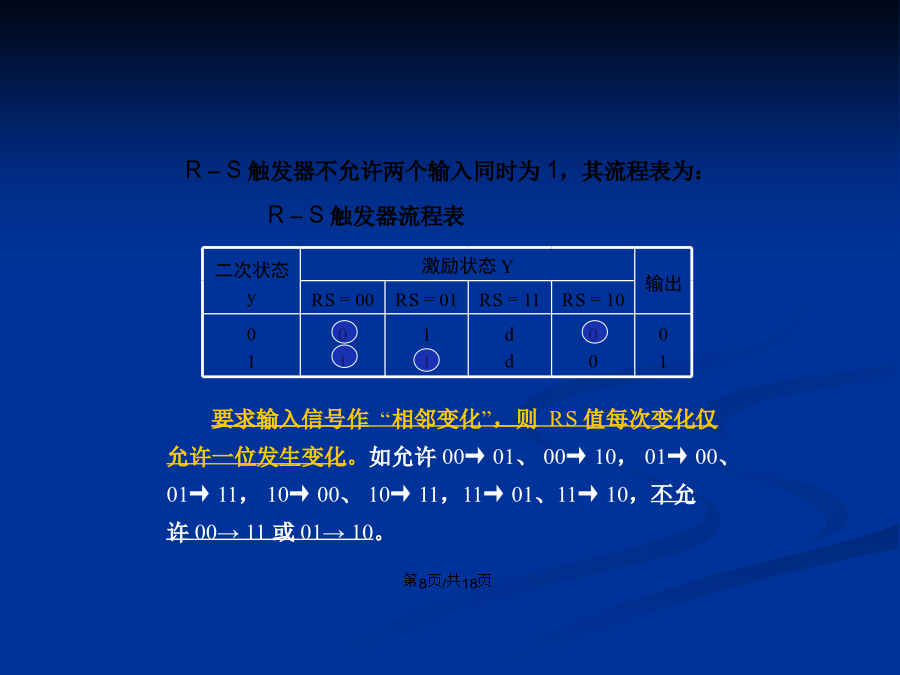

异步时序逻辑电路脉冲异步时序逻辑电路脉冲异步时序逻辑电路的分析例分析图所示脉冲异步时序逻辑电路,指出电路功能。脉冲异步时序逻辑电路的设计D触发器激励表J-K触发器激励表T触发器R-S触发器激励表电平异步时序逻辑电路输入信号的约束电平异步时序电路的分析电平异步时序逻辑电路的竞争

异步时序逻辑电路.ppt

第五章异步时序逻辑电路5.1异步时序逻辑电路的特点及模型2.异步时序逻辑电路的特点组合逻辑5.2脉冲异步时序逻辑电路5.2.1脉冲异步时序逻辑电路的分析分析步骤如下:例:分析下图所示的脉冲异步时序逻辑电路解:现态y2y1作状态表和状态图:根据转移真值表可作出状态图.例:分析下图所示的脉冲异步时序逻辑电路作状态转移真值表现态y作状态表和状态图根据转移真值表可作出下列状态表和状态图画时间图和说明电路功能例:分析下图所示的脉冲异步时序电路解:该式表明当CP为逻辑1时,触发器的状态才能发生变化,而只有当时钟出现有