一种FinFET器件及制备方法、电子装置.pdf

是你****枝呀

亲,该文档总共18页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种FinFET器件及制备方法、电子装置.pdf

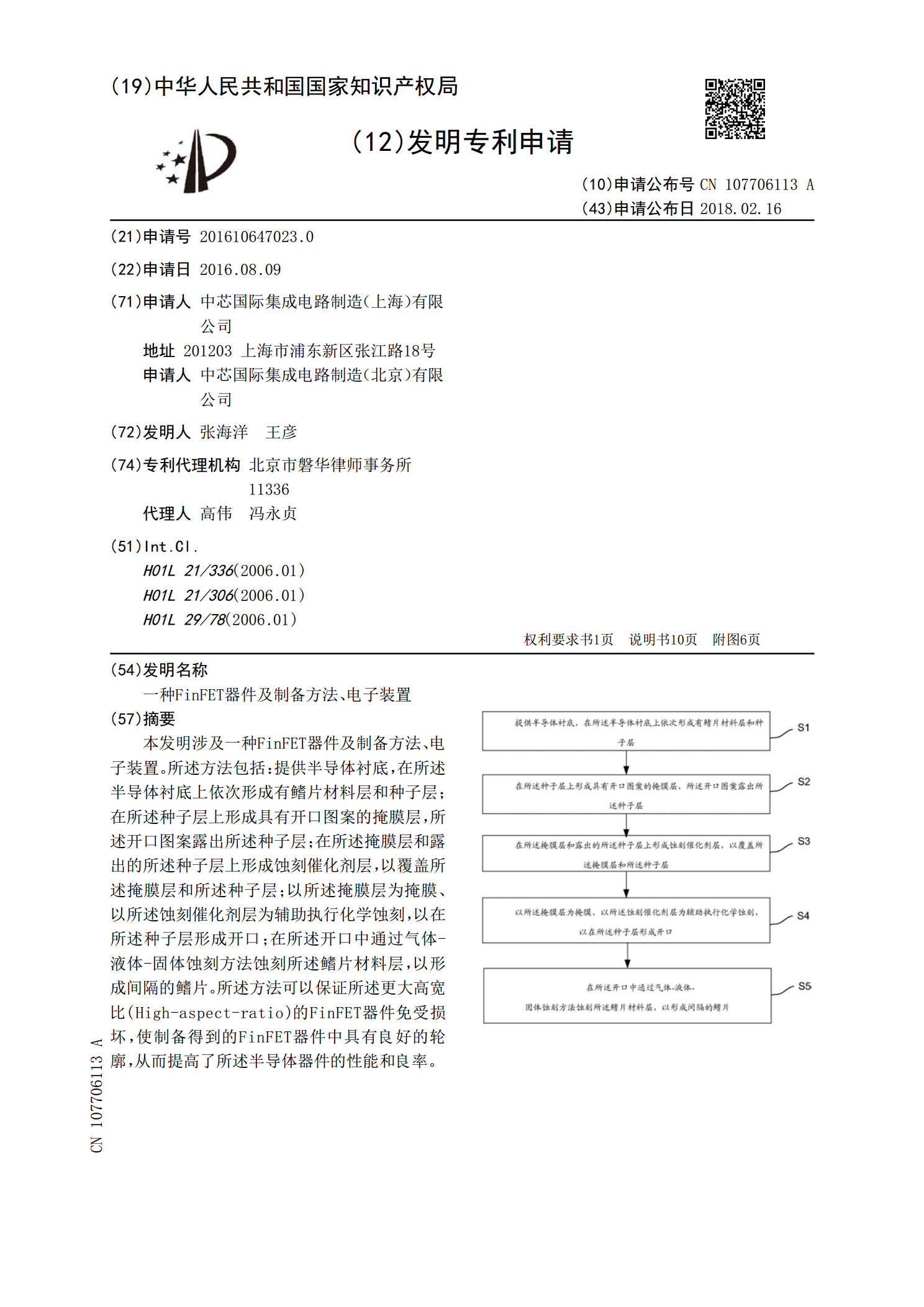

本发明涉及一种FinFET器件及制备方法、电子装置。所述方法包括:提供半导体衬底,在所述半导体衬底上依次形成有鳍片材料层和种子层;在所述种子层上形成具有开口图案的掩膜层,所述开口图案露出所述种子层;在所述掩膜层和露出的所述种子层上形成蚀刻催化剂层,以覆盖所述掩膜层和所述种子层;以所述掩膜层为掩膜、以所述蚀刻催化剂层为辅助执行化学蚀刻,以在所述种子层形成开口;在所述开口中通过气体‑液体‑固体蚀刻方法蚀刻所述鳍片材料层,以形成间隔的鳍片。所述方法可以保证所述更大高宽比(High‑aspect‑ratio)的F

一种FinFET器件及制备方法、电子装置.pdf

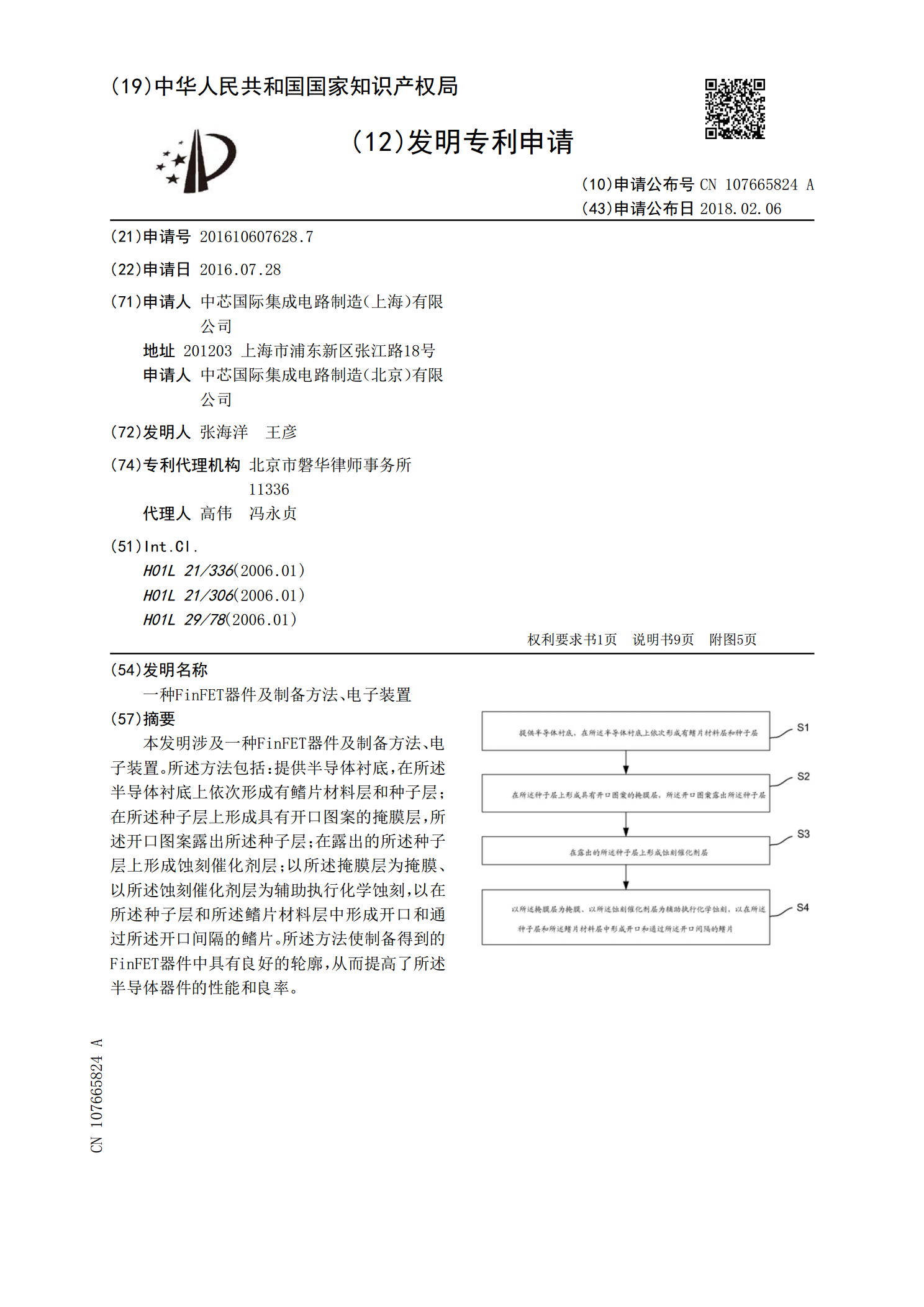

本发明涉及一种FinFET器件及制备方法、电子装置。所述方法包括:提供半导体衬底,在所述半导体衬底上依次形成有鳍片材料层和种子层;在所述种子层上形成具有开口图案的掩膜层,所述开口图案露出所述种子层;在露出的所述种子层上形成蚀刻催化剂层;以所述掩膜层为掩膜、以所述蚀刻催化剂层为辅助执行化学蚀刻,以在所述种子层和所述鳍片材料层中形成开口和通过所述开口间隔的鳍片。所述方法使制备得到的FinFET器件中具有良好的轮廓,从而提高了所述半导体器件的性能和良率。

一种FinFET器件及制备方法、电子装置.pdf

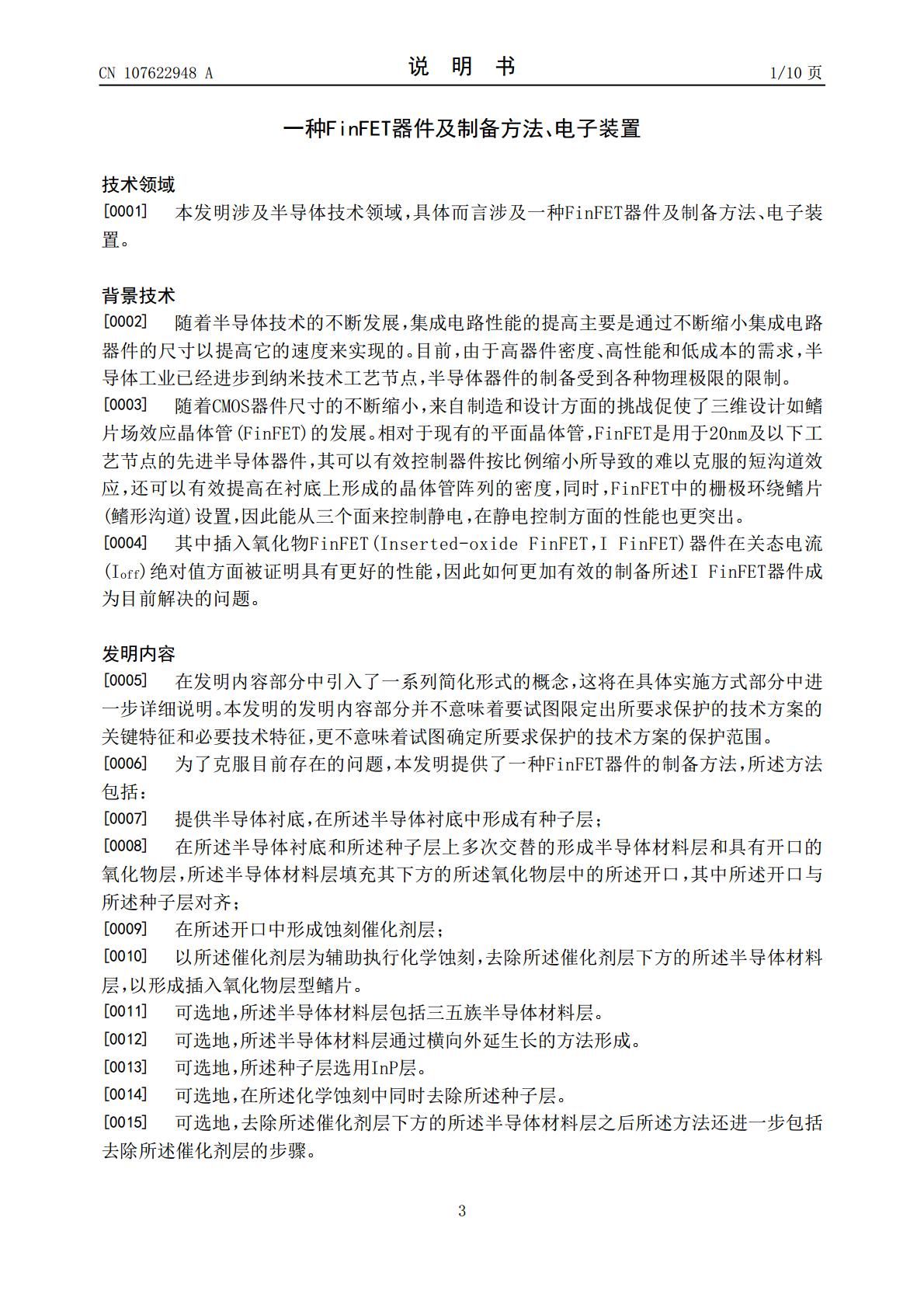

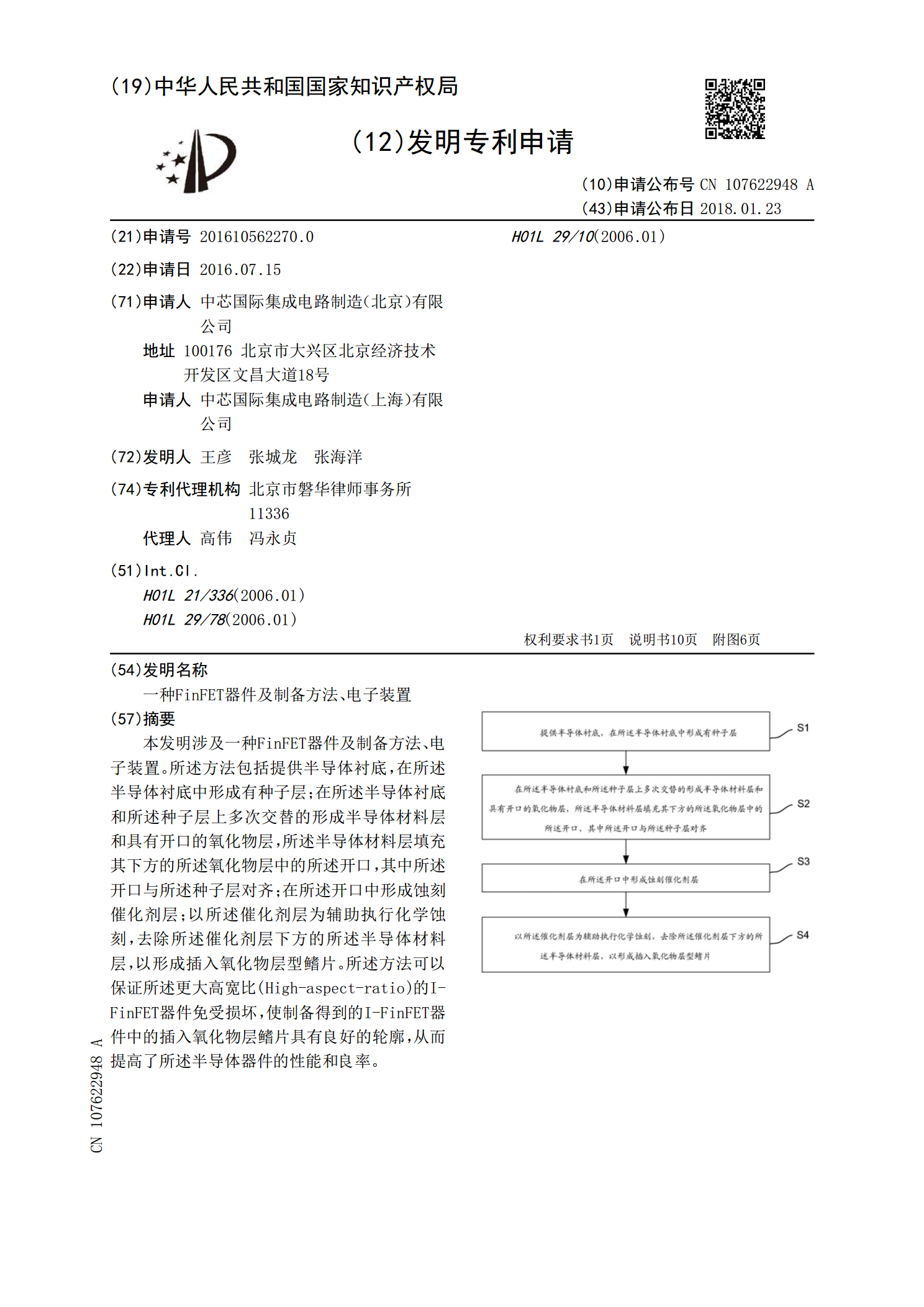

本发明涉及一种FinFET器件及制备方法、电子装置。所述方法包括提供半导体衬底,在所述半导体衬底中形成有种子层;在所述半导体衬底和所述种子层上多次交替的形成半导体材料层和具有开口的氧化物层,所述半导体材料层填充其下方的所述氧化物层中的所述开口,其中所述开口与所述种子层对齐;在所述开口中形成蚀刻催化剂层;以所述催化剂层为辅助执行化学蚀刻,去除所述催化剂层下方的所述半导体材料层,以形成插入氧化物层型鳍片。所述方法可以保证所述更大高宽比(High‑aspect‑ratio)的I‑FinFET器件免受损坏,使制备

一种量子阱FinFET器件及其制备方法、电子装置.pdf

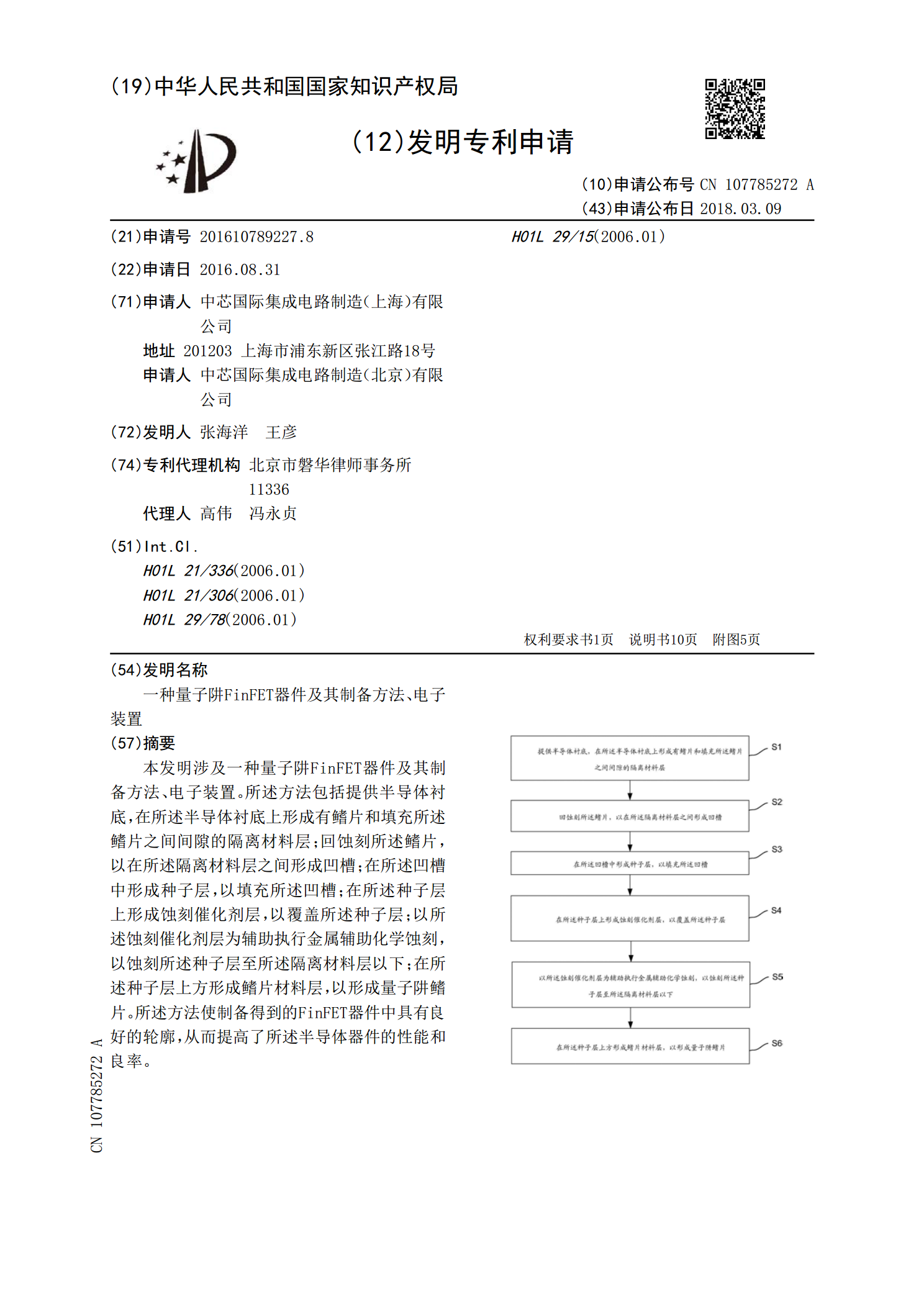

本发明涉及一种量子阱FinFET器件及其制备方法、电子装置。所述方法包括提供半导体衬底,在所述半导体衬底上形成有鳍片和填充所述鳍片之间间隙的隔离材料层;回蚀刻所述鳍片,以在所述隔离材料层之间形成凹槽;在所述凹槽中形成种子层,以填充所述凹槽;在所述种子层上形成蚀刻催化剂层,以覆盖所述种子层;以所述蚀刻催化剂层为辅助执行金属辅助化学蚀刻,以蚀刻所述种子层至所述隔离材料层以下;在所述种子层上方形成鳍片材料层,以形成量子阱鳍片。所述方法使制备得到的FinFET器件中具有良好的轮廓,从而提高了所述半导体器件的性能和

一种FinFET器件及其形成方法和电子装置.pdf

本发明提供一种FinFET器件及其形成方法。该形成方法在进行蚀刻之前,利用保护膜覆盖鳍状物,然后对鳍状物进行光刻以在第一组鳍状物上形成第一蚀刻图案,第一组鳍状物包含待去除的第一鳍结构;之后利用第一蚀刻图案蚀刻第一组鳍状物和对应的保护膜,去除第一鳍结构并形成第一组预设鳍状物;之后通过各向同性蚀刻去除残留的第一鳍结构,在对应第一组鳍状物的基板上形成凹结构。因而避免了现有技术中蚀刻后留下的圆角问题;同时形成的凹结构有利于维持水平线,不会造成器件的弯曲。