半导体结构及其制作方法.pdf

猫巷****雪凝

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体结构及其制作方法.pdf

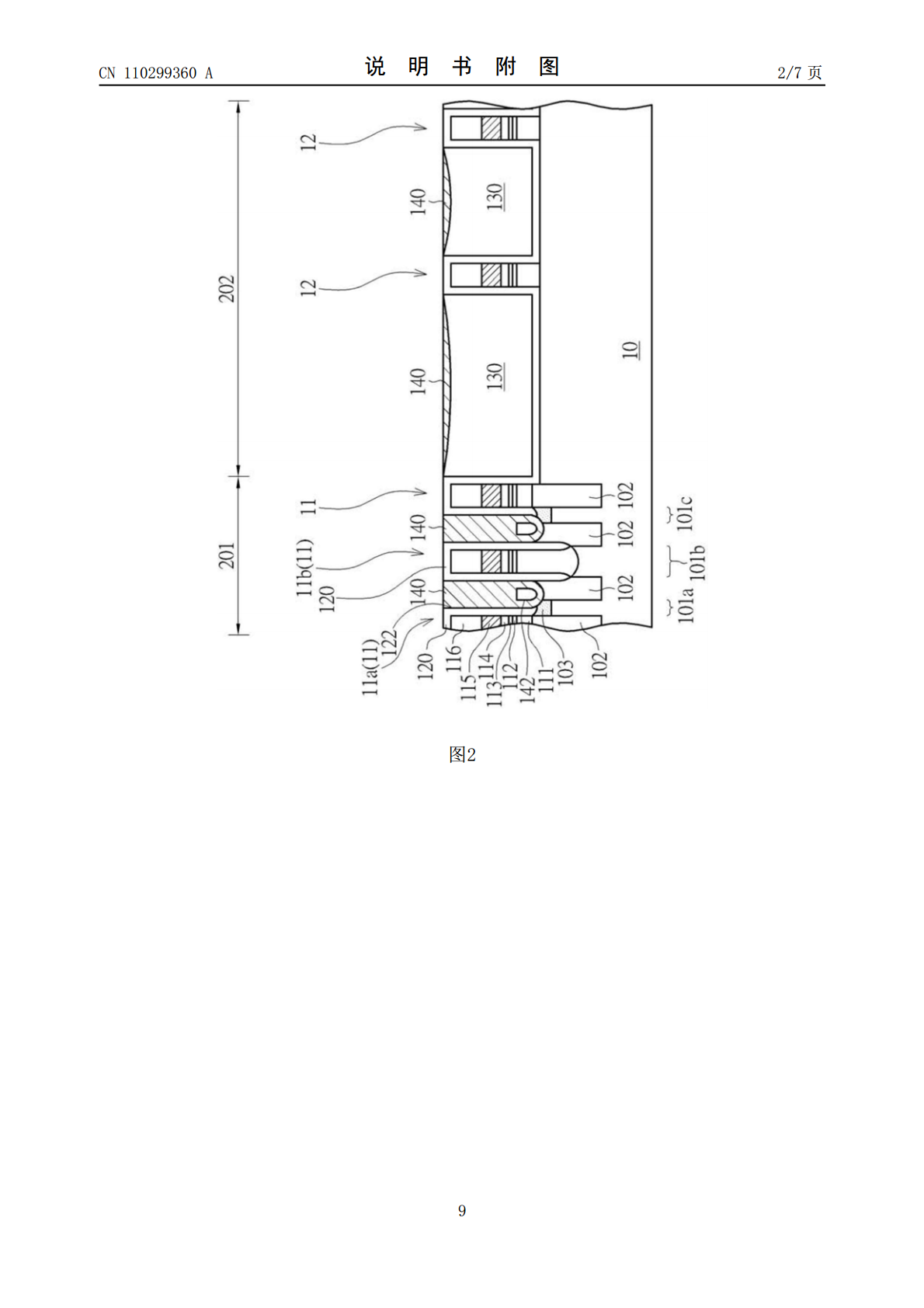

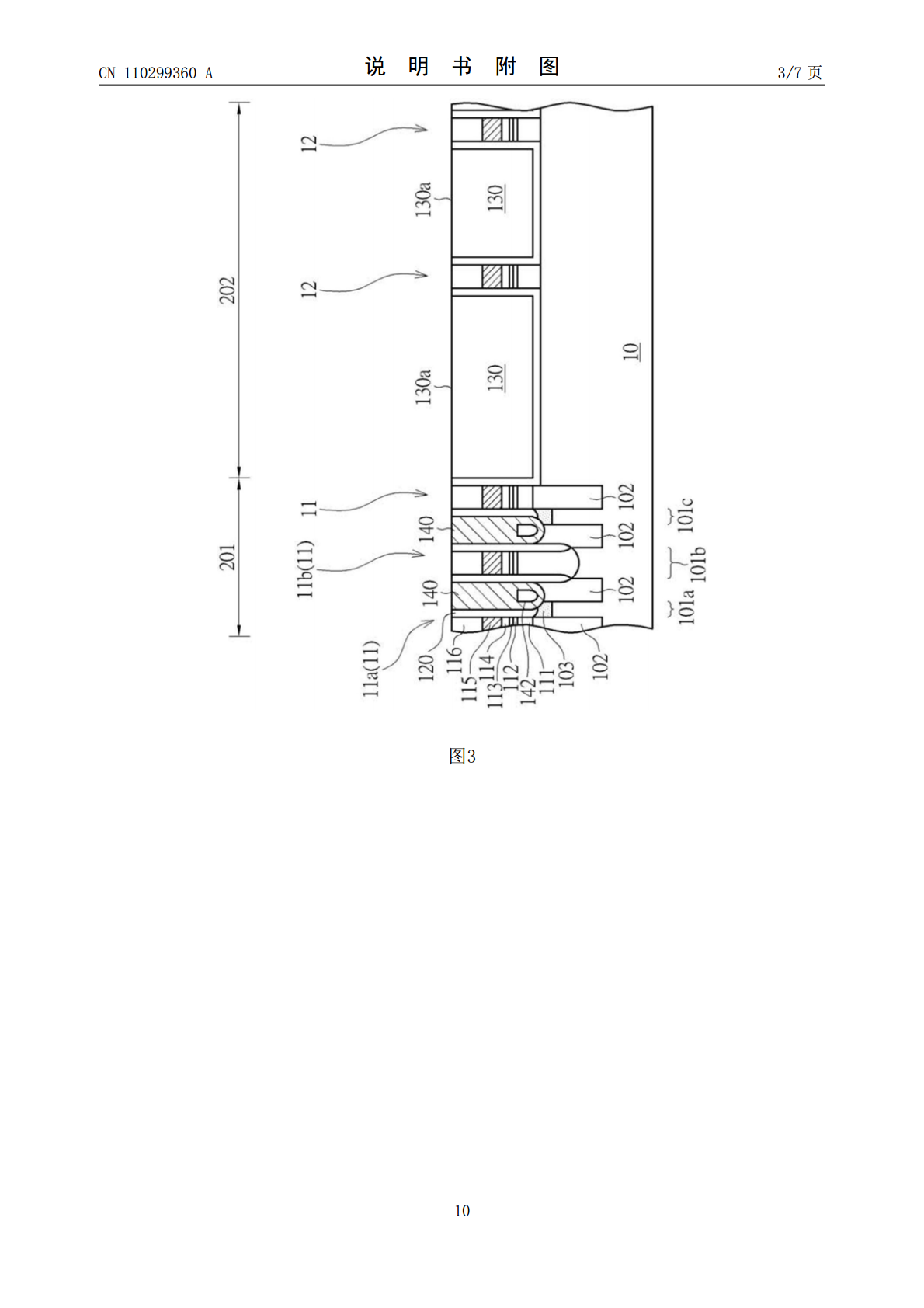

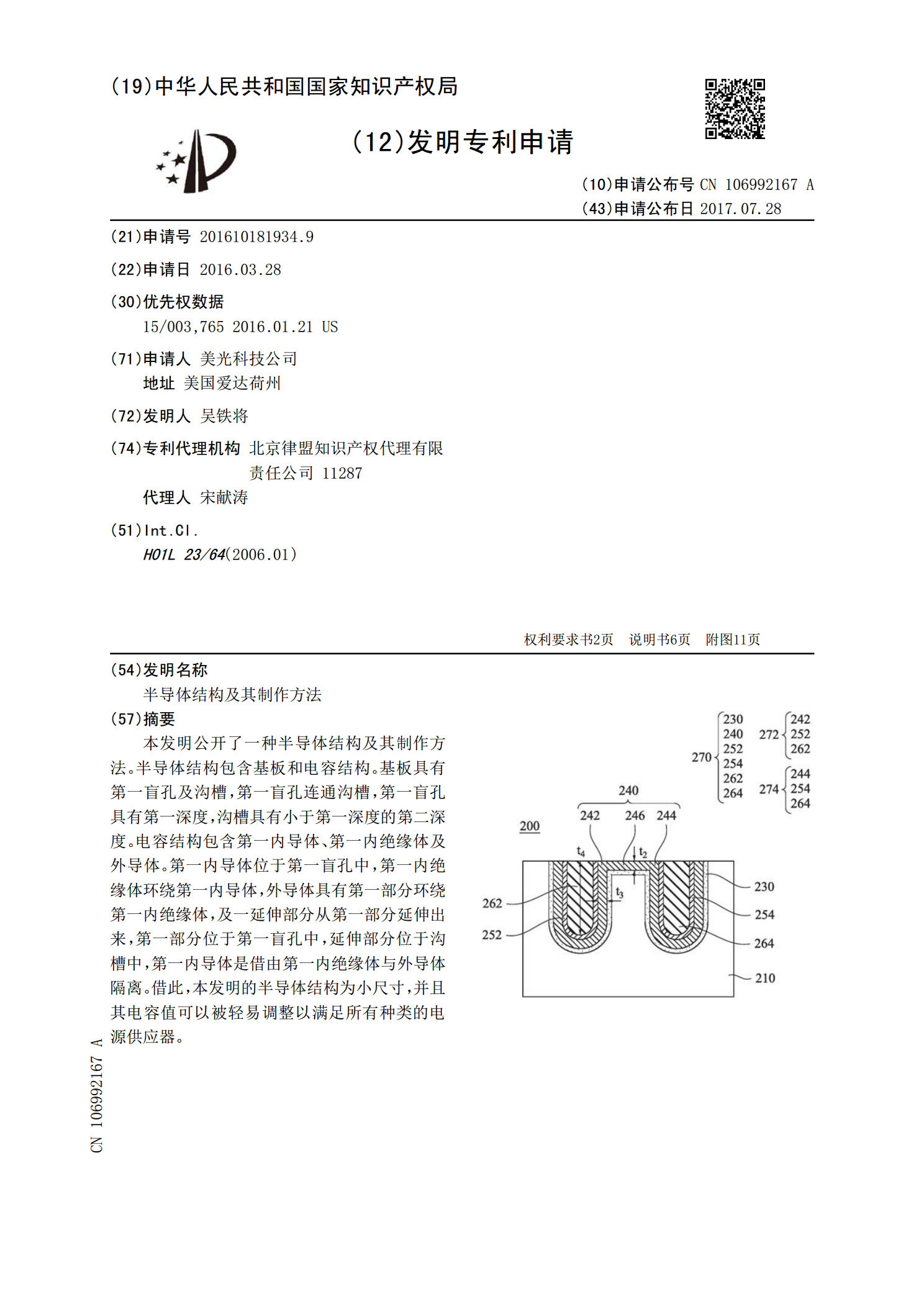

本发明公开了一种半导体结构及其制作方法。半导体结构包含基板和电容结构。基板具有第一盲孔及沟槽,第一盲孔连通沟槽,第一盲孔具有第一深度,沟槽具有小于第一深度的第二深度。电容结构包含第一内导体、第一内绝缘体及外导体。第一内导体位于第一盲孔中,第一内绝缘体环绕第一内导体,外导体具有第一部分环绕第一内绝缘体,及一延伸部分从第一部分延伸出来,第一部分位于第一盲孔中,延伸部分位于沟槽中,第一内导体是借由第一内绝缘体与外导体隔离。借此,本发明的半导体结构为小尺寸,并且其电容值可以被轻易调整以满足所有种类的电源供应器。

半导体结构及其制作方法.pdf

本公开提供了一种半导体结构及其制作方法,涉及半导体技术领域,半导体结构的制作方法包括:将目标结构置于反应腔中,向反应腔中通入第一反应气体和第二反应气体;将反应腔内的工艺条件调节为第一工艺条件,第一反应气体和第二反应气体在目标结构上形成低介电材料层;将第一工艺条件调节为第二工艺条件,第一反应气体和第二反应气体在低介电材料层上形成保护层。本公开在制作过程中无需转移目标结构,在同一反应腔中形成低介电材料层和保护层,不仅节省了一个沉积腔室,还减少了沉积步骤,提高了制程效率、减少了制程时间,降低了生产成本;保护层能

半导体结构及其制作方法.pdf

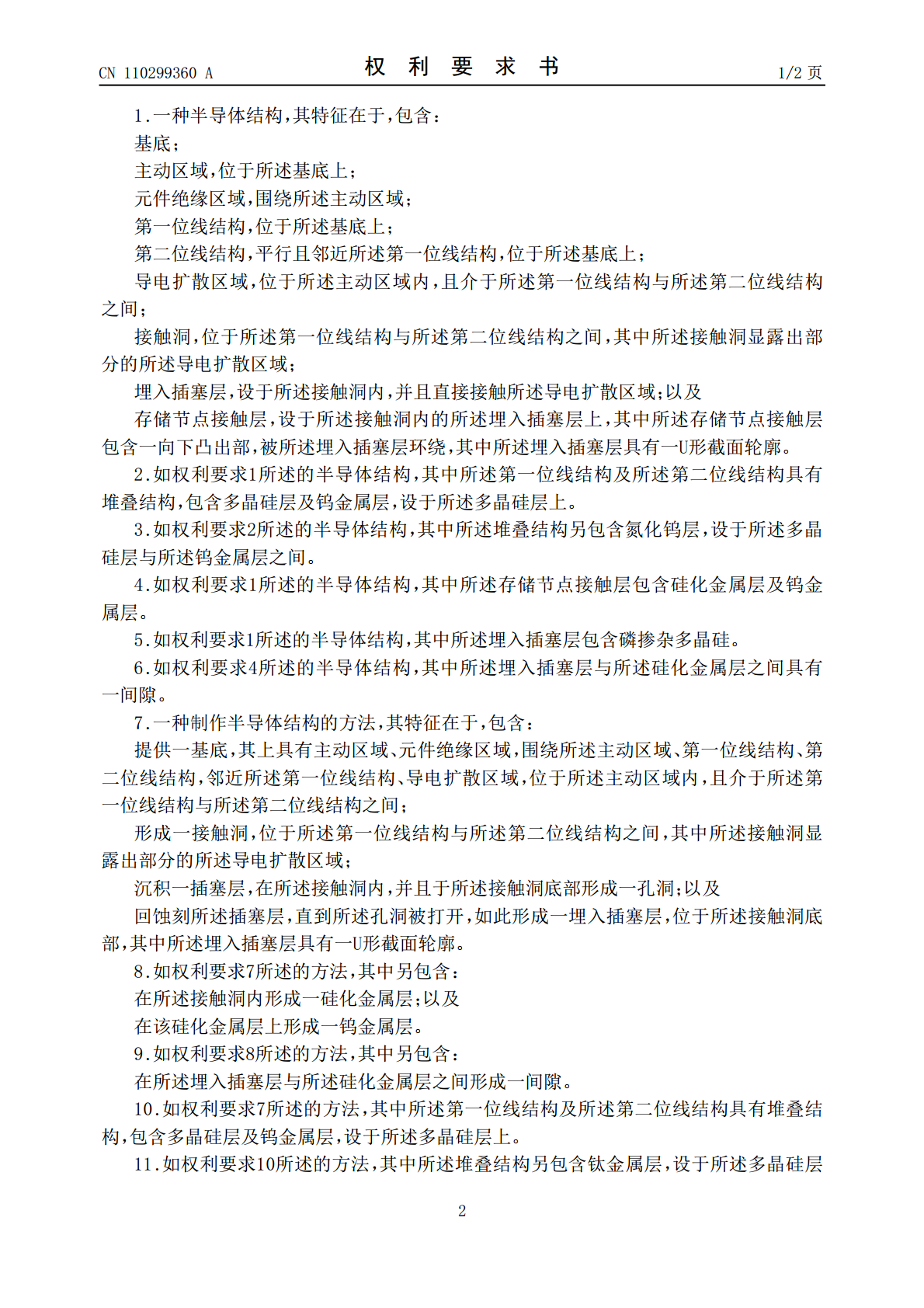

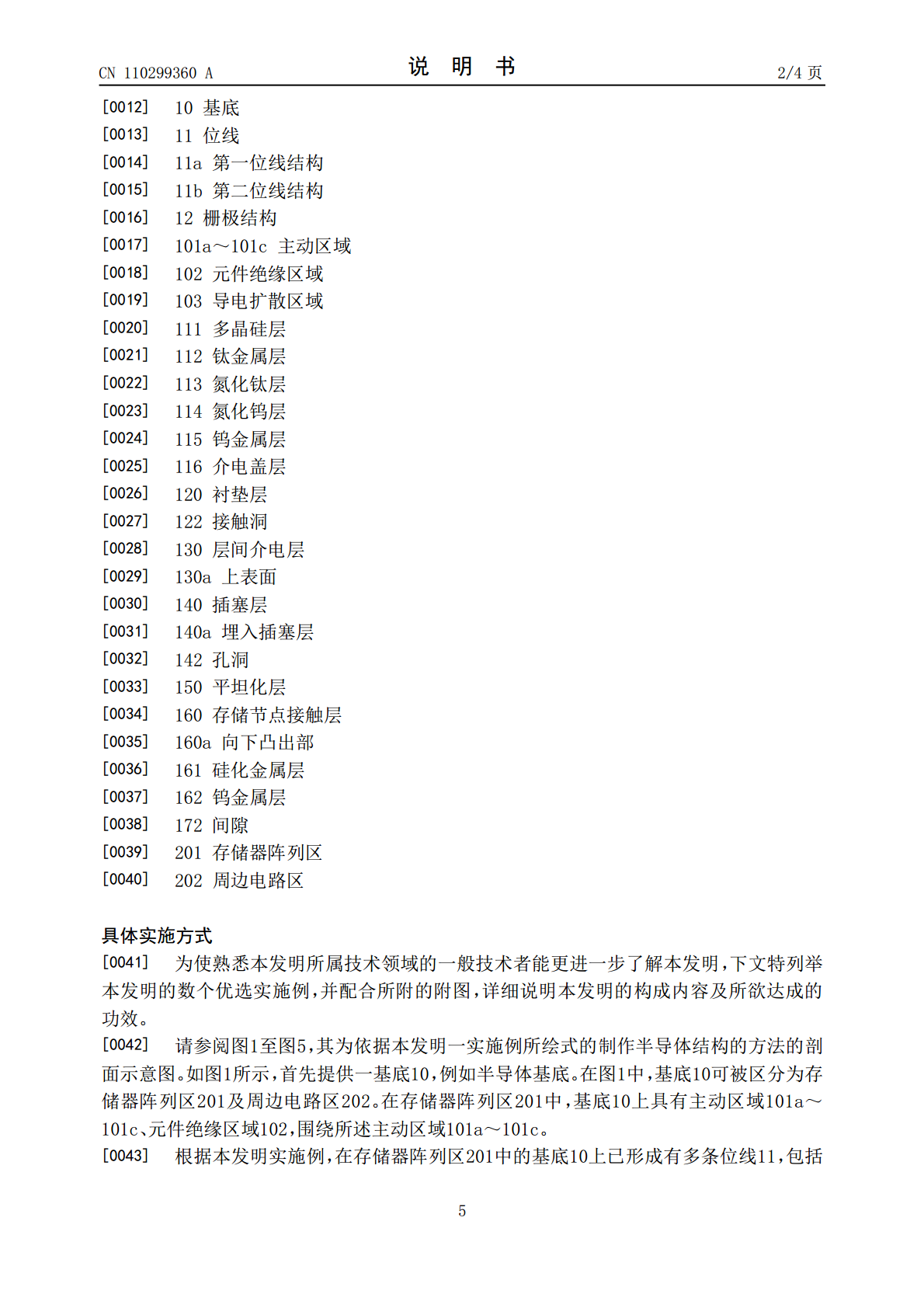

本发明公开一种半导体结构及其制作方法,其中该半导体结构包含基底;主动区域;元件绝缘区域,围绕主动区域;第一、第二位线结构,位于基底上;导电扩散区域,位于主动区域内,且介于第一、第二位线结构间;接触洞,位于第一、第二位线结构间,显露出部分导电扩散区域;埋入插塞层,设于接触洞内,直接接触导电扩散区域;及存储节点接触层,设于接触洞内的埋入插塞层上,其中存储节点接触层包含一向下凸出部,被埋入插塞层环绕,其中埋入插塞层具有一U形截面轮廓。

半导体结构及其制作方法.pdf

本申请提供一种半导体结构及其制作方法,涉及半导体技术领域,用于解决半导体结构的性能较差技术问题,该半导体结构的制作方法包括:提供衬底;在衬底上形成多个间隔设置的叠层结构,叠层结构包括依次层叠设置的第一导电层、绝缘层和第二导电层,第一导电层和第二导电层中的至少一个为半金属层;形成覆盖叠层结构的沟道层,以及覆盖沟道层的介质层;形成沿第一方向延伸的字线,字线包括多个接触部和连接相邻的接触部的连接部,接触部环绕且接触介质层的侧表面,接触部与至少部分绝缘层相对。通过设置半金属层,可以降低叠层结构与其他结构的接触电阻

半导体结构及其制作方法.pdf

本申请提出一种半导体结构及其制作方法,半导体结构包含第一导电层、第一阻挡层以及绝缘层;第一导电层包含至少两条走线,相邻两条走线之间形成有凹槽;第一阻挡层设置于凹槽的侧壁;绝缘层填充于凹槽,位于凹槽的绝缘层中形成有气隙。本申请通过在凹槽的侧壁设置第一阻挡层,能够有效隔绝外界水汽由绝缘层侵入第一导电层和其他结构,同时能够利用第一阻挡层有效防止第一导电层的相邻走线之间的电迁移现象。