计算机组成原理-第2章 存储系统.ppt

qw****27

亲,该文档总共238页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

计算机组成原理-第2章 存储系统.ppt

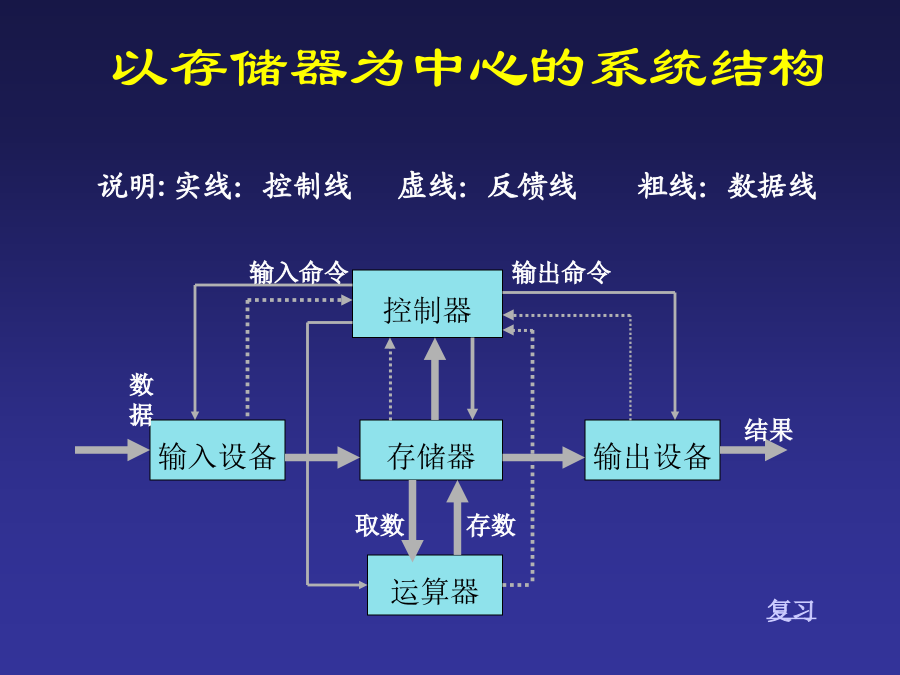

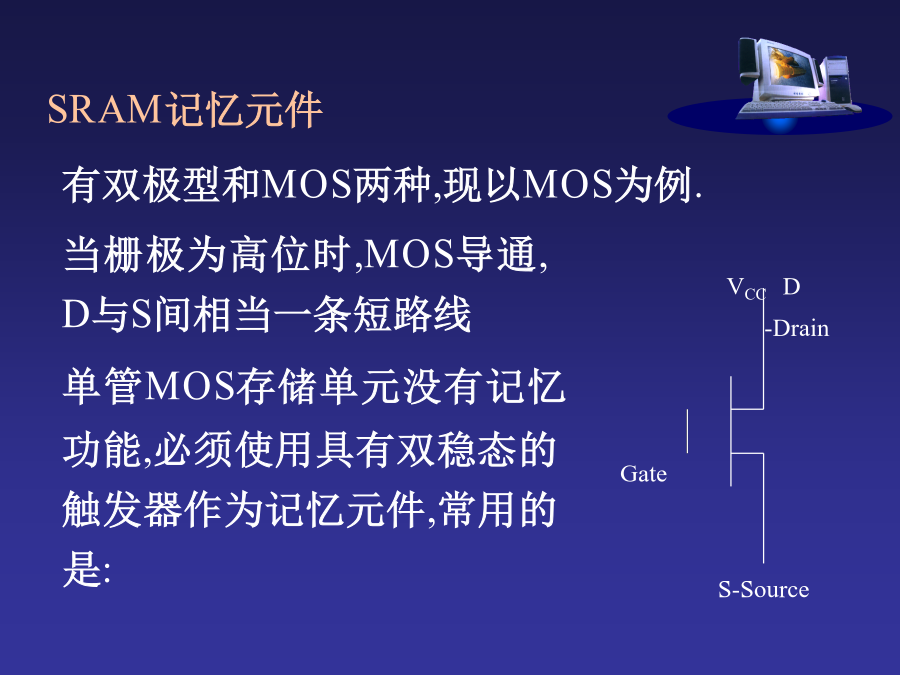

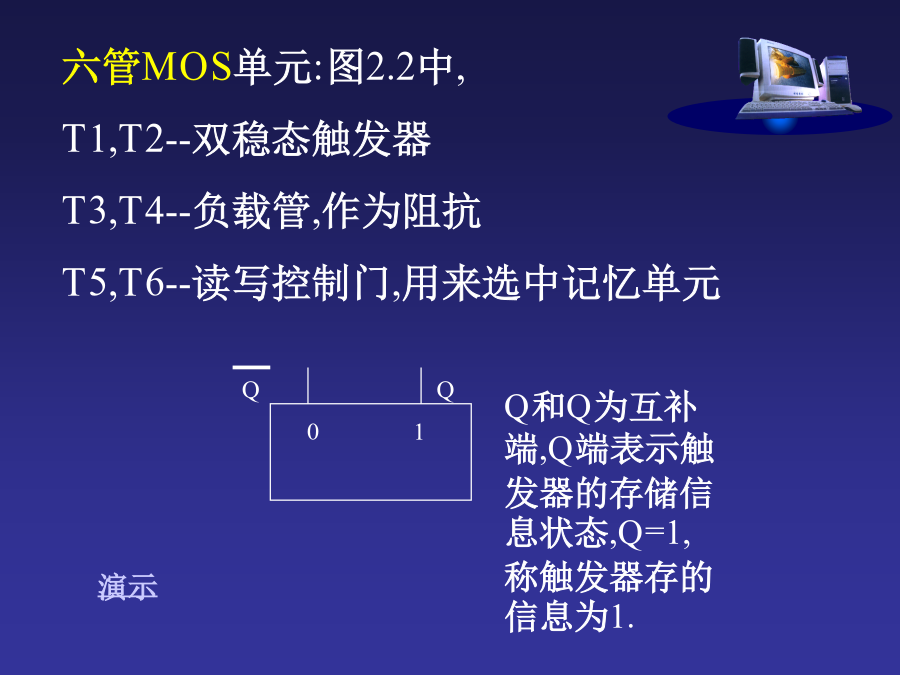

存储系统以存储器为中心的系统结构现代计算机中,主存储器处于全机中心地位,其主要原因:2.1.1●RAM记忆元件从原理上分,可分为双极(bipolar)型和MOS(MetalOxideSemiconductor).又可按工作原理分为静态和动态两种:SRAM(StaticRAM):即静态RAM,利用开关特性记忆,只要电源有电,就能稳定保存信息.DRAM(DynamicRAM):即动态RAM,除需电源外,还要定期对它充电(刷新).SRAM记忆元件六管MOS单元:图2.2中,T1,T2--双稳态触发器T3,T4-

计算机组成原理--第6章存储系统.ppt

第6章存储系统6.1.1存储器的分类6.1.2存储系统的层次结构6.2.1主存储器的分类6.2.2动态RAM基本单元电路WE6.2.2动态RAM基本单元电路6.2.2动态RAM基本单元电路6.2.3存储容量的扩展CS716M×1位×32片500ns500ns6.2.5主存储器的技术指标6.3.1Cache的工作原理6.3.1Cache的工作原理6.3.2Cache-主存地址映像6.3.2Cache-主存地址映像6.3.2Cache-主存地址映像6.3.3Cache替换算法6.4.1磁表面存储器的读写原理6

计算机组成原理(白中英)第3章存储系统.ppt

计算机组成原理第一章计算机系统概论第二章运算方法和运算器第三章存储系统第四章指令系统第五章中央处理器第六章总线系统第七章外围设备第八章输入输出系统第九章并行组织教材白中英,计算机组成原理·网络版,科学出版社,2002参考书石磊,计算机组成原理·第2版,清华大学出版社,2006钱晓捷,微型计算机原理及应用,清华大学出版社,2006王爱英,计算机组成与结构·第3版,清华大学出版社,2001白中英邝坚,计算机组织与结构·网络版,科学出版社,20033.1存储器概述3.2随机读写存储器3.3只读存储器和闪速存储器

大学计算机组成原理 第3章 存储系统2.ppt

第3章存储系统3.5并行存储器双端口存储器:是指同一个存储器具有两组相互独立的读写控制线路,是一种高速工作的存储器。它提供了两个相互独立的端口,即左端口和右端口。两个端口分别具有各自的地址线、数据线和控制线,可以对存储器中任何位置上的数据进行独立的存取操作。双端口存储器IDT7133的介绍当两个端口的地址不相同时,在两个端口上进行读写操作,一定不会发生冲突。当任一端口被选中驱动时,就可对整个存储器进行存取,每一个端口都有自己的片选控制(CE)和输出驱动控制(OE)。读操作时,端口的OE(低电平有效)打开输

考研必备计算机组成原理第4章 存储系统.ppt

第4章存储系统第4章存储系统本章要点:存储器分类及其工作原理芯片扩展方法存储空间管理方法4.1计算机存储系统组织方式基于以上原因,计算机中配置存储器时,需要考虑两方面的问题:(1)如何利用有限的存储空间尽可能多地存储数据、方便快捷地读出数据。(2)如何将慢速的磁盘存储器和快速的处理器匹配起来。第1个问题的解决方法,我们将在4.5节中详细介绍。下面简单介绍第2个问题的解决方法。为了同时满足用户对容量和速度的要求,计算机系统往往会采用以下的存储器配置方法,如图4-1所示。大容量磁盘存储器处于存储系统的最底层,