多波长VCSEL阵列和制造方法.pdf

努力****梓颖

亲,该文档总共27页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

多波长VCSEL阵列和制造方法.pdf

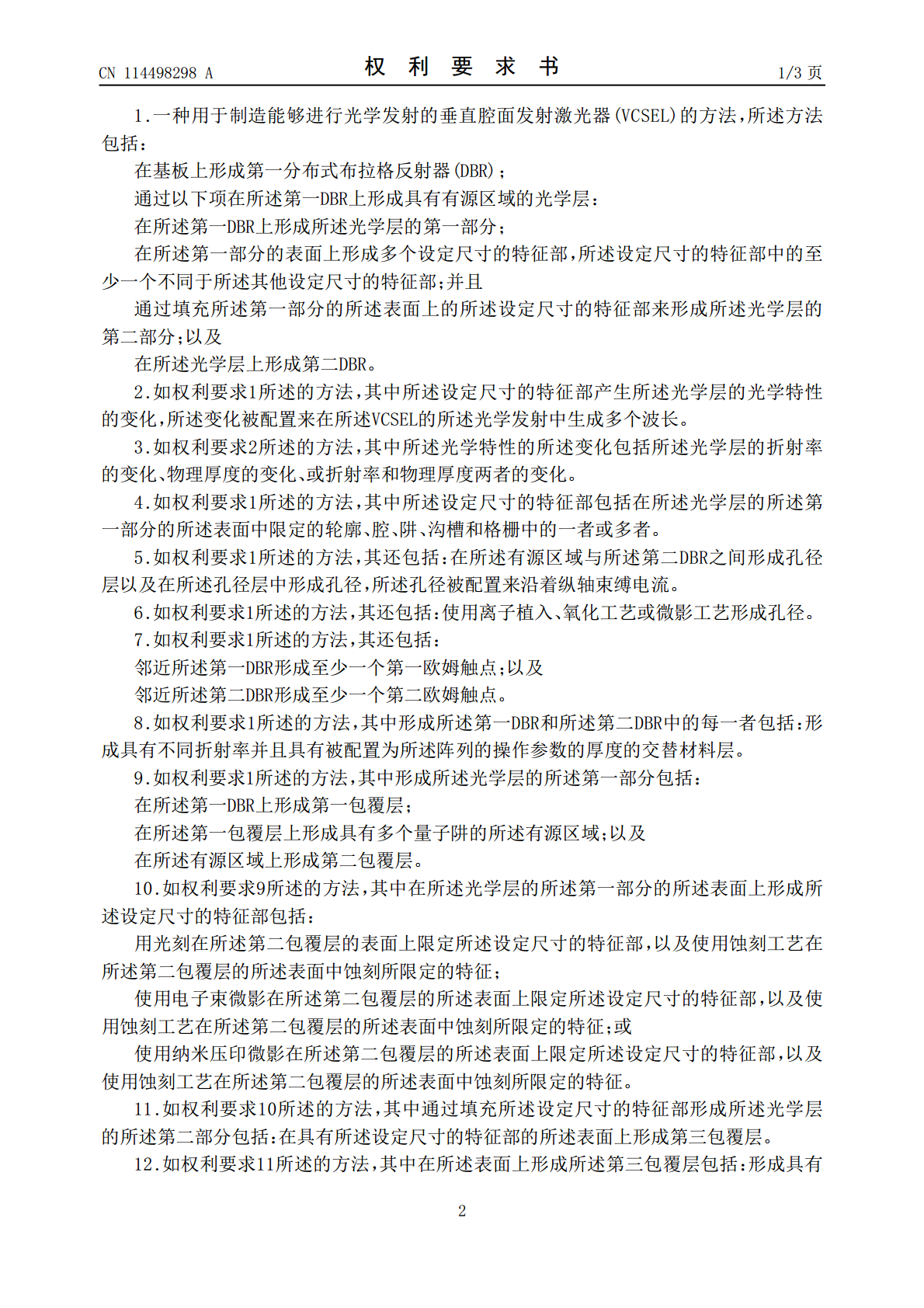

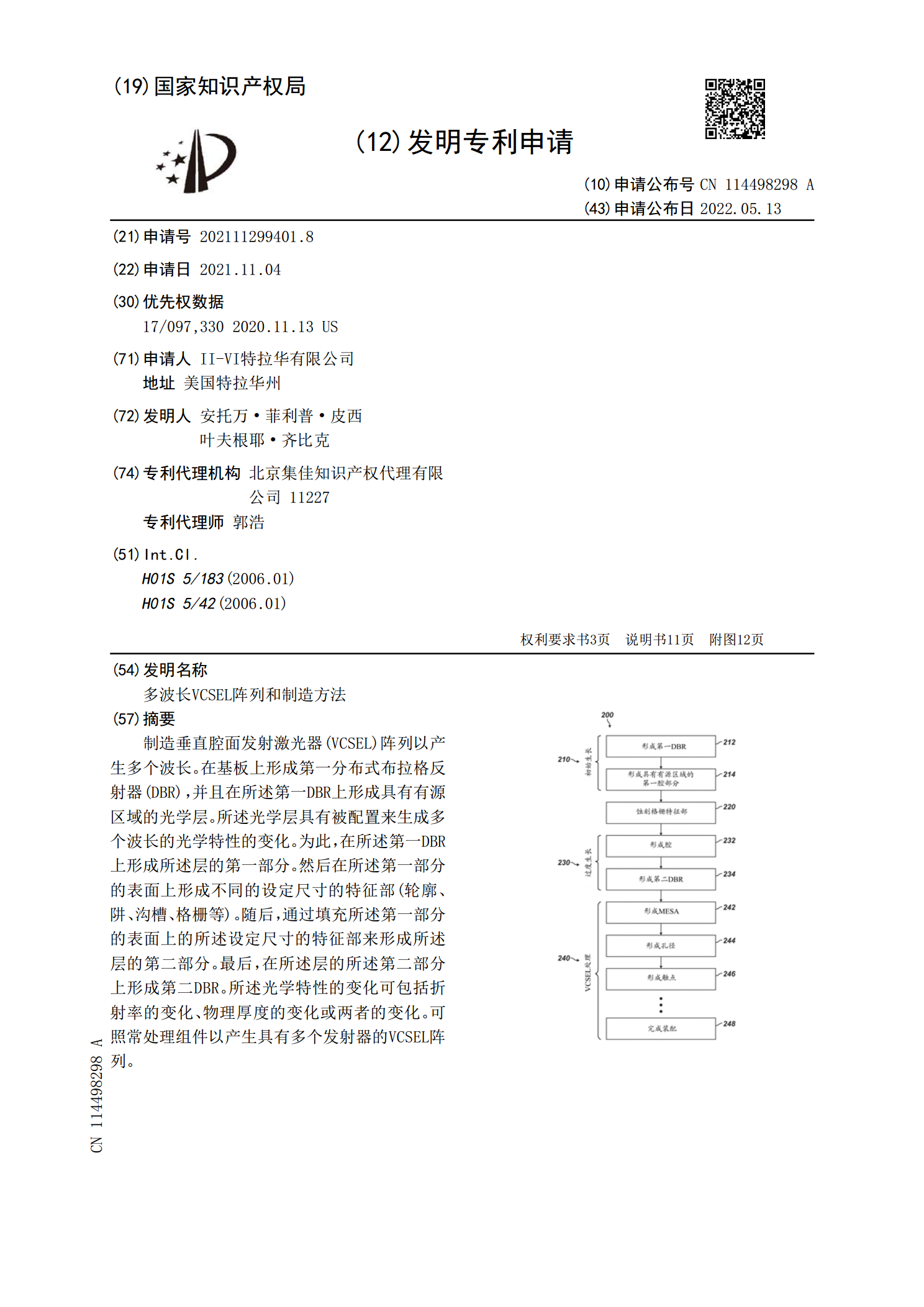

制造垂直腔面发射激光器(VCSEL)阵列以产生多个波长。在基板上形成第一分布式布拉格反射器(DBR),并且在所述第一DBR上形成具有有源区域的光学层。所述光学层具有被配置来生成多个波长的光学特性的变化。为此,在所述第一DBR上形成所述层的第一部分。然后在所述第一部分的表面上形成不同的设定尺寸的特征部(轮廓、阱、沟槽、格栅等)。随后,通过填充所述第一部分的表面上的所述设定尺寸的特征部来形成所述层的第二部分。最后,在所述层的所述第二部分上形成第二DBR。所述光学特性的变化可包括折射率的变化、物理厚度的变化或两

VCSEL芯片制造方法及VCSEL阵列.pdf

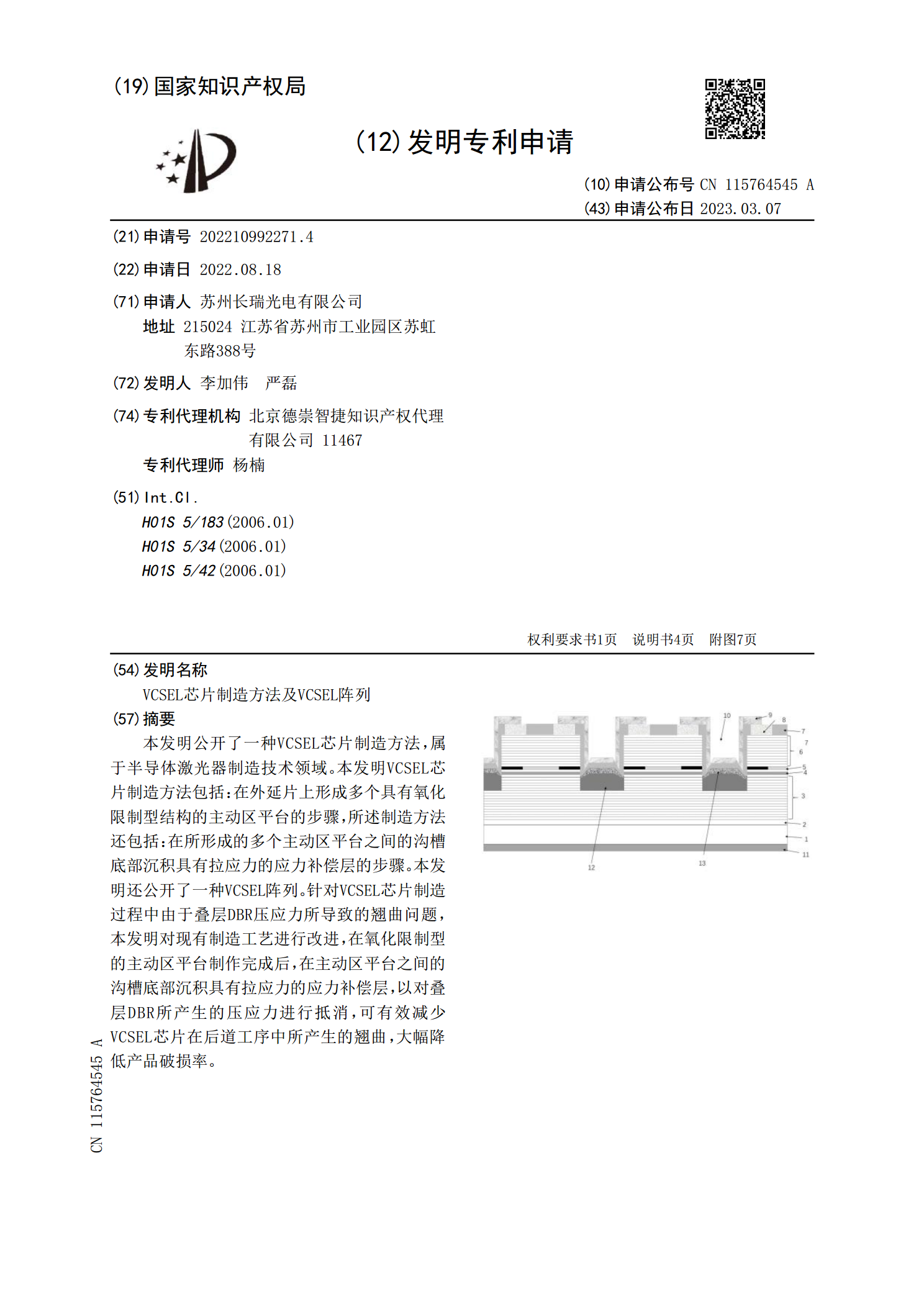

本发明公开了一种VCSEL芯片制造方法,属于半导体激光器制造技术领域。本发明VCSEL芯片制造方法包括:在外延片上形成多个具有氧化限制型结构的主动区平台的步骤,所述制造方法还包括:在所形成的多个主动区平台之间的沟槽底部沉积具有拉应力的应力补偿层的步骤。本发明还公开了一种VCSEL阵列。针对VCSEL芯片制造过程中由于叠层DBR压应力所导致的翘曲问题,本发明对现有制造工艺进行改进,在氧化限制型的主动区平台制作完成后,在主动区平台之间的沟槽底部沉积具有拉应力的应力补偿层,以对叠层DBR所产生的压应力进行抵消,

单颗可变色阵列型VCSEL芯片及其制造方法.pdf

本发明公开了单颗可变色阵列型VCSEL芯片及其制造方法,VCSEL芯片包括量子阱、第一过渡层和第二过渡层;第一过渡层上设置有第一GaAs柱,第一GaAs柱上独立生长有ODR层,ODR层被蚀刻形成第一台柱,第一台柱蒸镀有镜面层,三个第一台柱的镜面层上覆盖有同一外延片键合层,且外延片键合层覆盖镜面层外侧直至第一过渡层,外延片键合层上设置有Si片、P‑contact;第二过渡层上设置有三个独立的第二GaAs柱,第二GaAs柱上生长有DBR层,DBR层被蚀刻形成第二台柱,第二台柱蒸镀有N‑contact,N‑co

具有光学限制控制的低成本长波长VCSEL的设计和制造.pdf

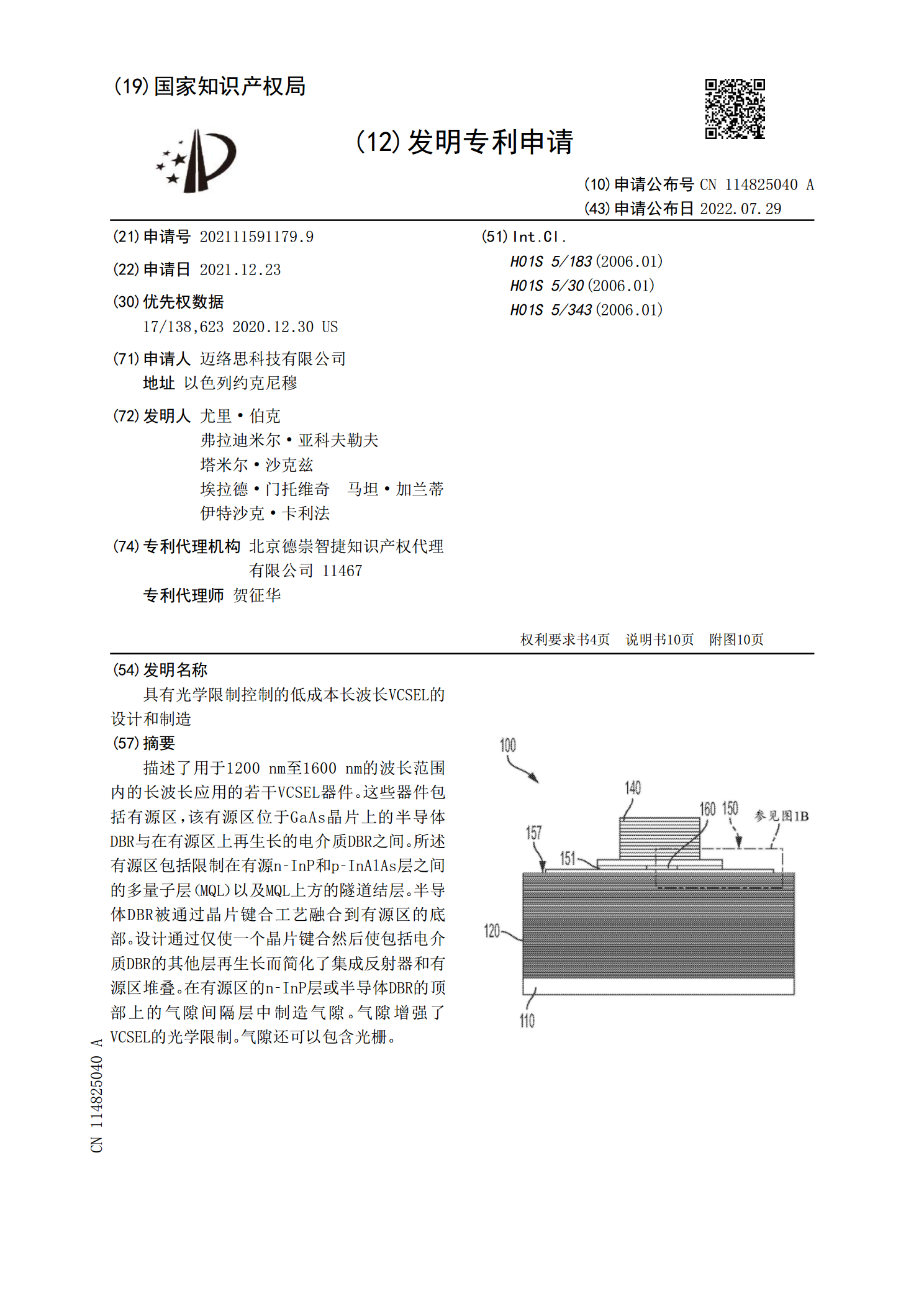

描述了用于1200nm至1600nm的波长范围内的长波长应用的若干VCSEL器件。这些器件包括有源区,该有源区位于GaAs晶片上的半导体DBR与在有源区上再生长的电介质DBR之间。所述有源区包括限制在有源n‑InP和p‑InAlAs层之间的多量子层(MQL)以及MQL上方的隧道结层。半导体DBR被通过晶片键合工艺融合到有源区的底部。设计通过仅使一个晶片键合然后使包括电介质DBR的其他层再生长而简化了集成反射器和有源区堆叠。在有源区的n‑InP层或半导体DBR的顶部上的气隙间隔层中制造气隙。气隙增强了V

阵列基板的制造方法和阵列基板.pdf

本申请实施例公开一种阵列基板的制造方法包括:提供一基板,在基板上形成遮光层;在遮光层上设置不同段差的光阻,并对遮光层进行刻蚀;刻蚀完成后,对光阻进行灰化处理,并保留遮光层预设位置上的光阻作为垫底层;在遮光层上依次沉积缓冲层、半导体层、绝缘层、栅极层以及介电层;在介电层上形成第一通孔、第二通孔和第三通孔,第三通孔的位置与预设位置相对应,用于暴露部分遮光层,第一通孔和第二通孔用于暴露部分半导体层;通过第一通孔、第二通孔和第三通孔形成源极和漏极,源极分别通过第二通孔和第三通孔与遮光层和半导体层相连接,漏极通过第