时序逻辑电路讲解.ppt

as****16

亲,该文档总共80页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

时序逻辑电路讲解.ppt

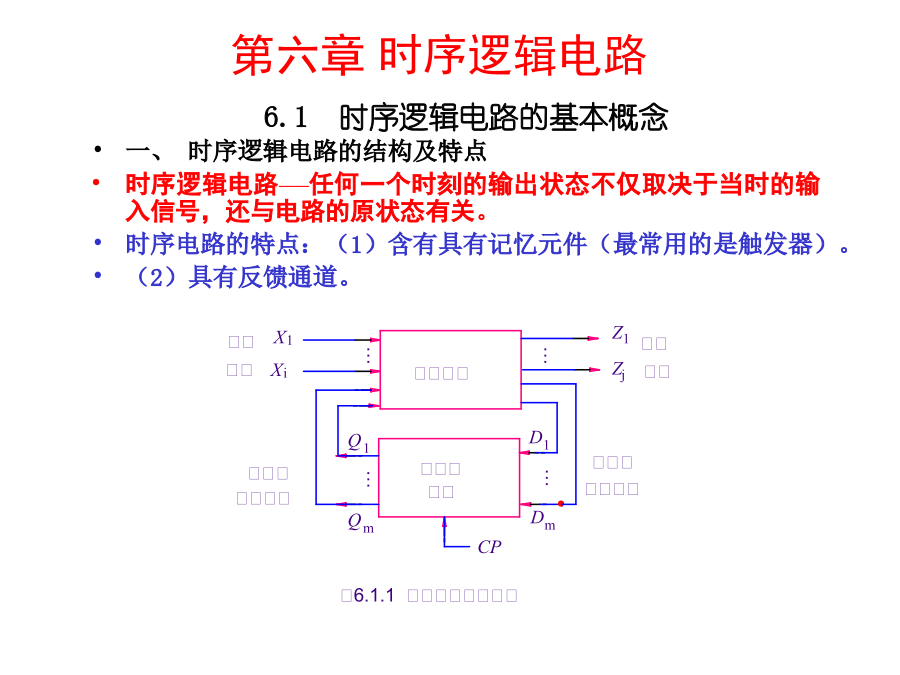

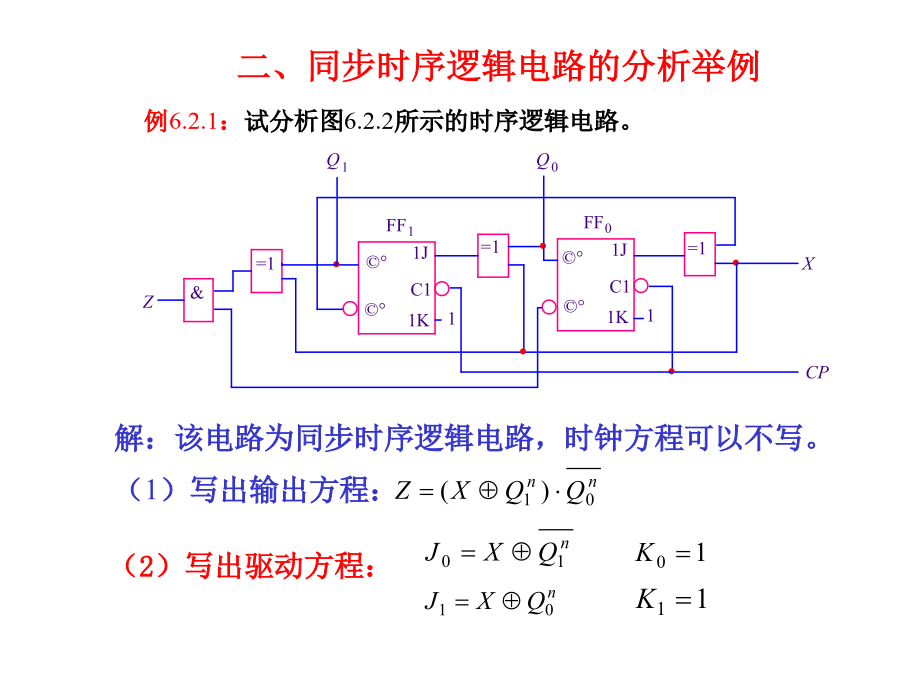

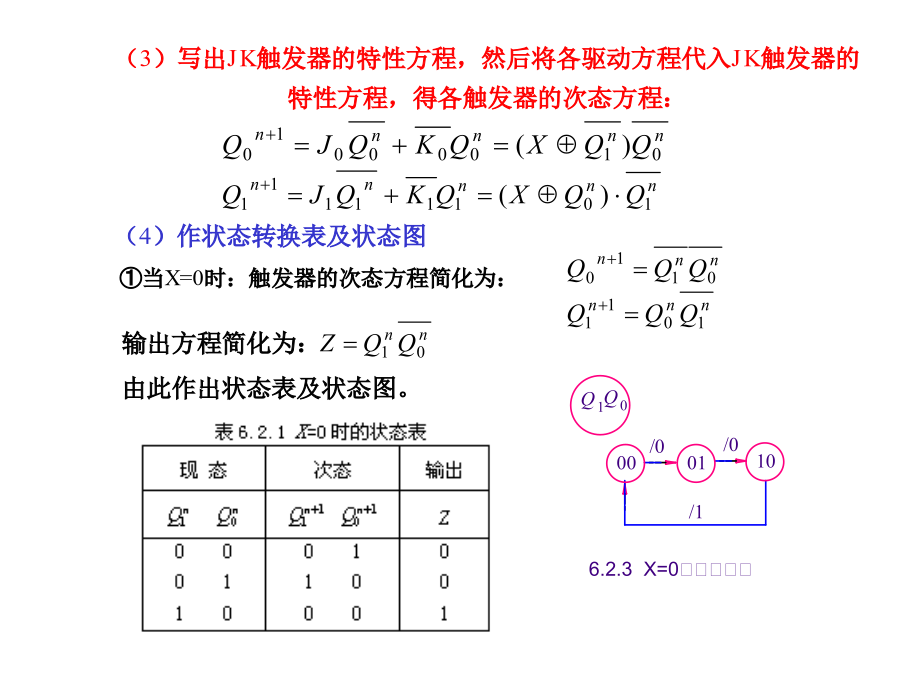

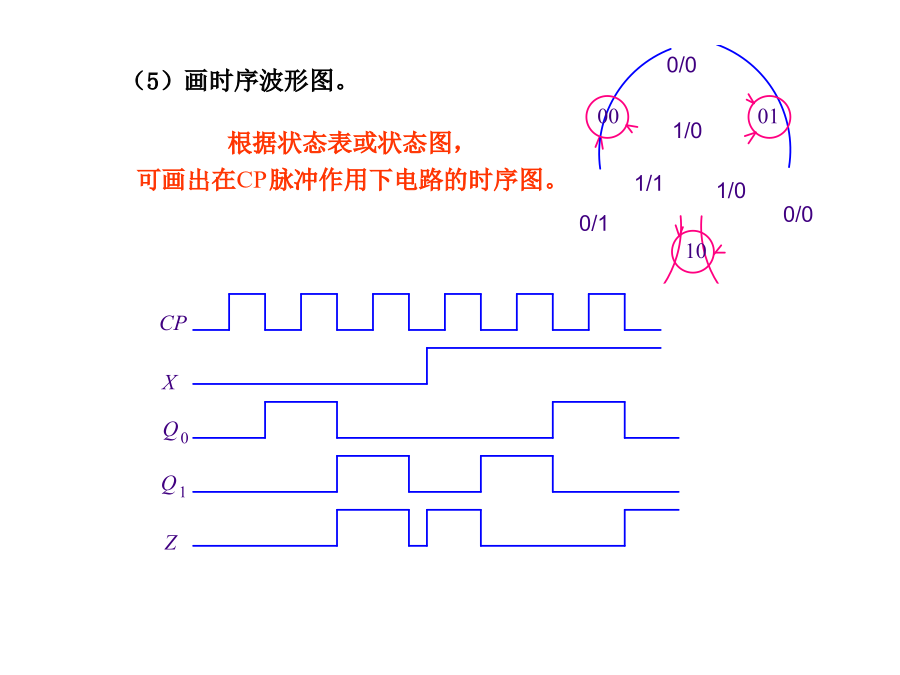

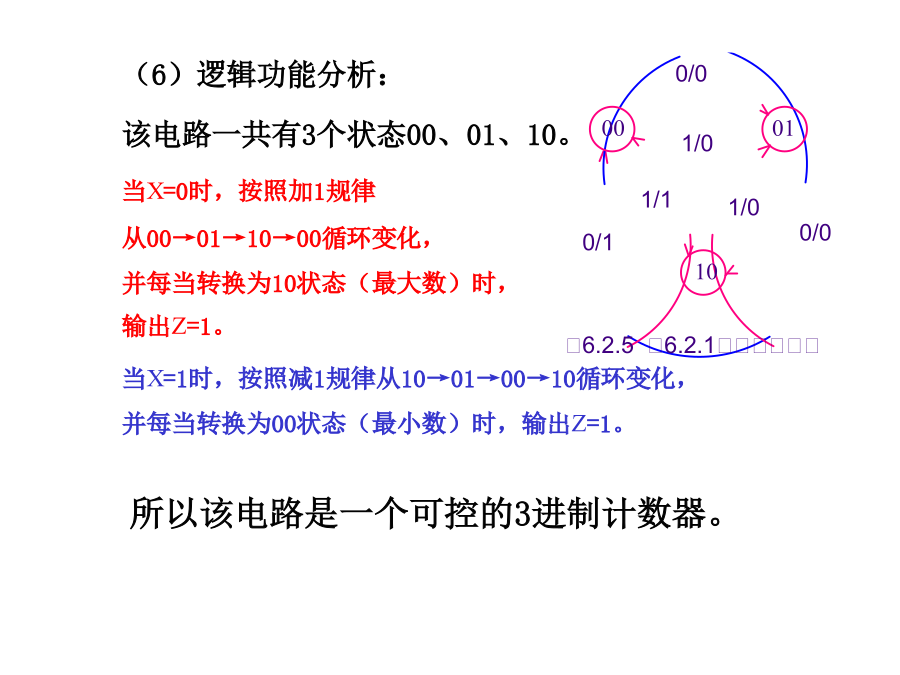

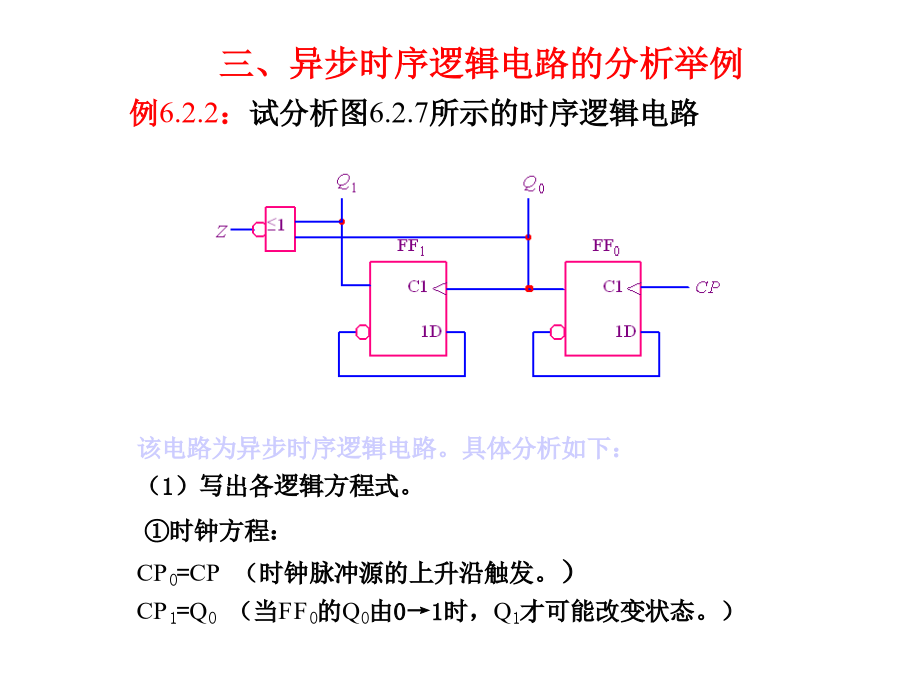

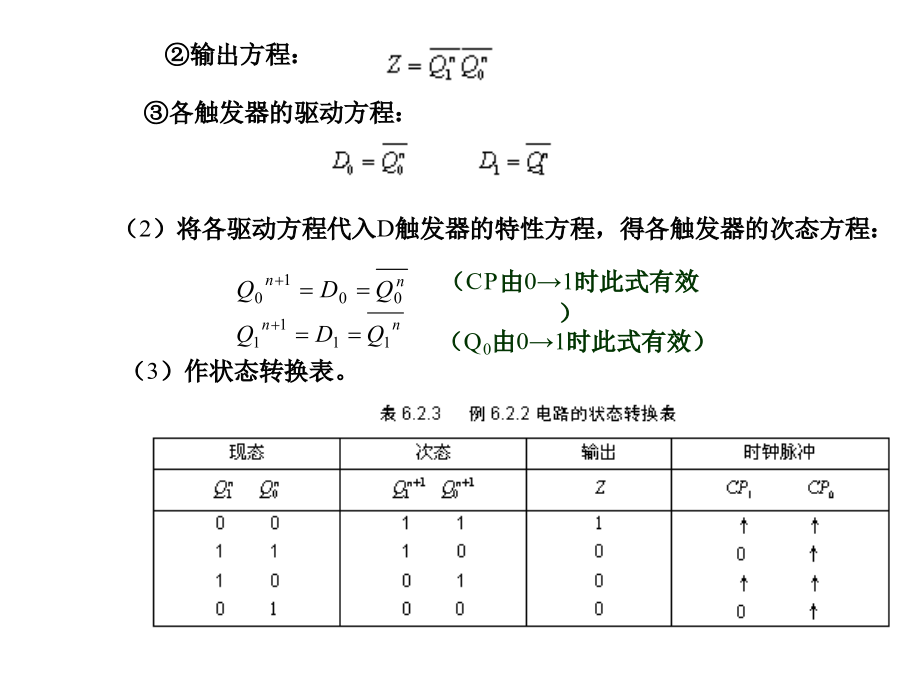

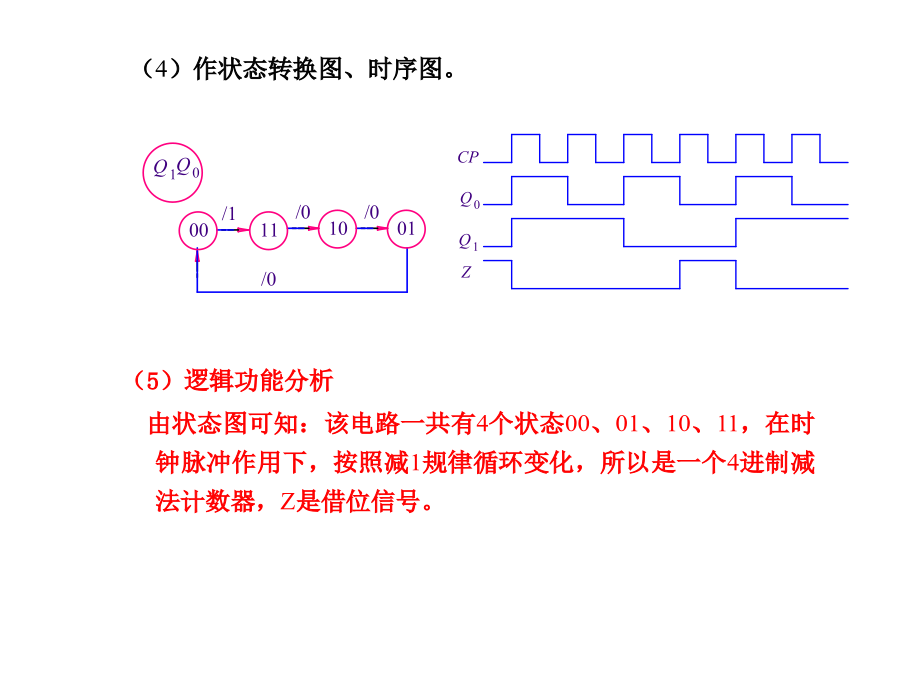

第六章时序逻辑电路一、分析时序逻辑电路的一般步骤1.由逻辑图写出下列各逻辑方程式:(1)各触发器的时钟方程。(2)时序电路的输出方程。(3)各触发器的驱动方程。2.将驱动方程代入相应触发器的特性方程,求得时序逻辑电路的状态方程。3.根据状态方程和输出方程,列出该时序电路的状态表,画出状态图或时序图。4.根据电路的状态表或状态图说明给定时序逻辑电路的逻辑功能。二、同步时序逻辑电路的分析举例(3)写出JK触发器的特性方程,然后将各驱动方程代入JK触发器的特性方程,得各触发器的次态方程:①当X=1时:触发器的次

时序逻辑电路讲解ppt.pptx

时序逻辑电路讲解例置位二、同步RS触发器同步RS触发器的图形符号三、主从RS、JK触发器t110四、边沿JK、D触发器(1)SD–直接置位端,RD–直接清零端,通常用来设置触发器开始工作时得初始状态。不论J、K、C三端状态如何,只要SD=0、RD=1,就可使输出Q=1(置位);只要SD=1、RD=0,就可使输出Q=0(清零)。SD与RD均为低电平有效,在逻辑符号图中加‘o’表示。正常工作时SD=RD=1。由(1)与(2)得下降沿触发得JK触发器状态表如下。(1)JK触发器得特性方程D触发器状态表CPCP例

时序逻辑电路.ppt

上讲回顾常用的时序逻辑电路组成寄存器的触发器一般使用D触发器。一个D触发器组成1位的数码寄存器。寄存器CRDCPS1S0Q0Q1Q2Q30100101110111清零保持右移左移并行输入用双向移位寄存器74LS194组成节日彩灯控制电路计数器的主要功能:构成计数器的触发器一般有T、D和JK触发器。①驱动方程1二进制计数器(1)异步二进制加法计数器(一)Q0②状态表Q3Q2Q1Q0Q3n+1Q2n+1Q1n+1Q0n+1③状态图Q1二进制计数器同步计数器既可用T触发器构成,也可以用T`触发器构成。当计数器用

时序逻辑电路.ppt

时序逻辑电路4.3时序逻辑电路概述输出方程:三、典型的时序逻辑电路——串行加法器四、时序逻辑电路的分类2.计数器和状态机3.摩尔型状态机和米里型状态机4.4同步时序电路分析例:请分析以下同步时序电路:(2)写出状态方程(4)根据状态方程列出状态。(6)时序图(设Q2Q1Q0初态为000)时序逻辑电路设计的几种方法设计步骤例:试用JK触发器设计一个同步七进制计数器。(2)列出状态表(3)求出状态方程(根据状态表画卡诺图)(3)求出电路的驱动方程(4)根据得到的驱动方程画出逻辑图。(5)检查电路能否自启动。

时序逻辑电路.ppt

第六章时序逻辑电路6.1概述二、时序电路的一般结构形式与功能描述方法时序逻辑电路可以用三个方程组来描述:三、时序电路的分类6.2时序电路的分析方法例1:6.2.2时序电路的状态转换表、状态转换图、状态机流程图和时序图二、状态转换图三、状态机流程图(StateMachineChart)四、时序图例2:(4)列状态转换表:*6.2.3异步时序逻辑电路的分析方法6.3若干常用的时序逻辑电路例:用维-阻触发器结构的74HC175二、移位寄存器(代码在寄存器中可以左/右移动)器件实例:74LS194A,可实现左/右