超薄多层封装体及其制作方法与相关技术.pdf

13****80

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

超薄多层封装体及其制作方法与相关技术.pdf

图片简介:本技术介绍了一种超薄多层封装体及其制作方法,在基底层的上表面设有芯片层,在芯片层的外部填充有包封体,在包封体与芯片层的上表面设有正面钝化层,在硅基底层的下表面设有介质层,在介质层的下表面设有背面钝化层,在正面钝化层内嵌有正面布线,在背面钝化层内嵌有背面布线,背面布线与正面布线之间通过穿透硅基底层和包封体的金属柱相连。芯片层位于金属柱区域外,在金属柱的外壁上设有介质层、阻挡层和种子层。本技术采用背面硅体刻蚀工艺和芯片叠加工艺,实现了从硅基底层上表面到下表面堆叠芯片的直接互连,实现了超薄多层封装体的

封装壳体、封装体及其制作方法、电路以及装置.pdf

本发明涉及一种封装壳体、封装体及其制作方法、电路以及装置,本发明的封装壳体包括基板、侧壁以及盖板;基板包括用于实现与外部电路电连接的导电线路,侧壁上设有第一导电体,侧壁上的第一导电体对应于基板的导电线路且用于与导电线路直接接触连接;封装壳体还包括第二导电体,第二导电体设于侧壁和/或盖板上,第二导电体对应于侧壁上的第一导电体且用于与第一导电体直接接触连接;第二导电体延伸的部分还用于与发光芯片的第一电连接区域直接接触连接。不必为了焊线工艺留出额外的操作空间,有利于缩小封装产品的体积。

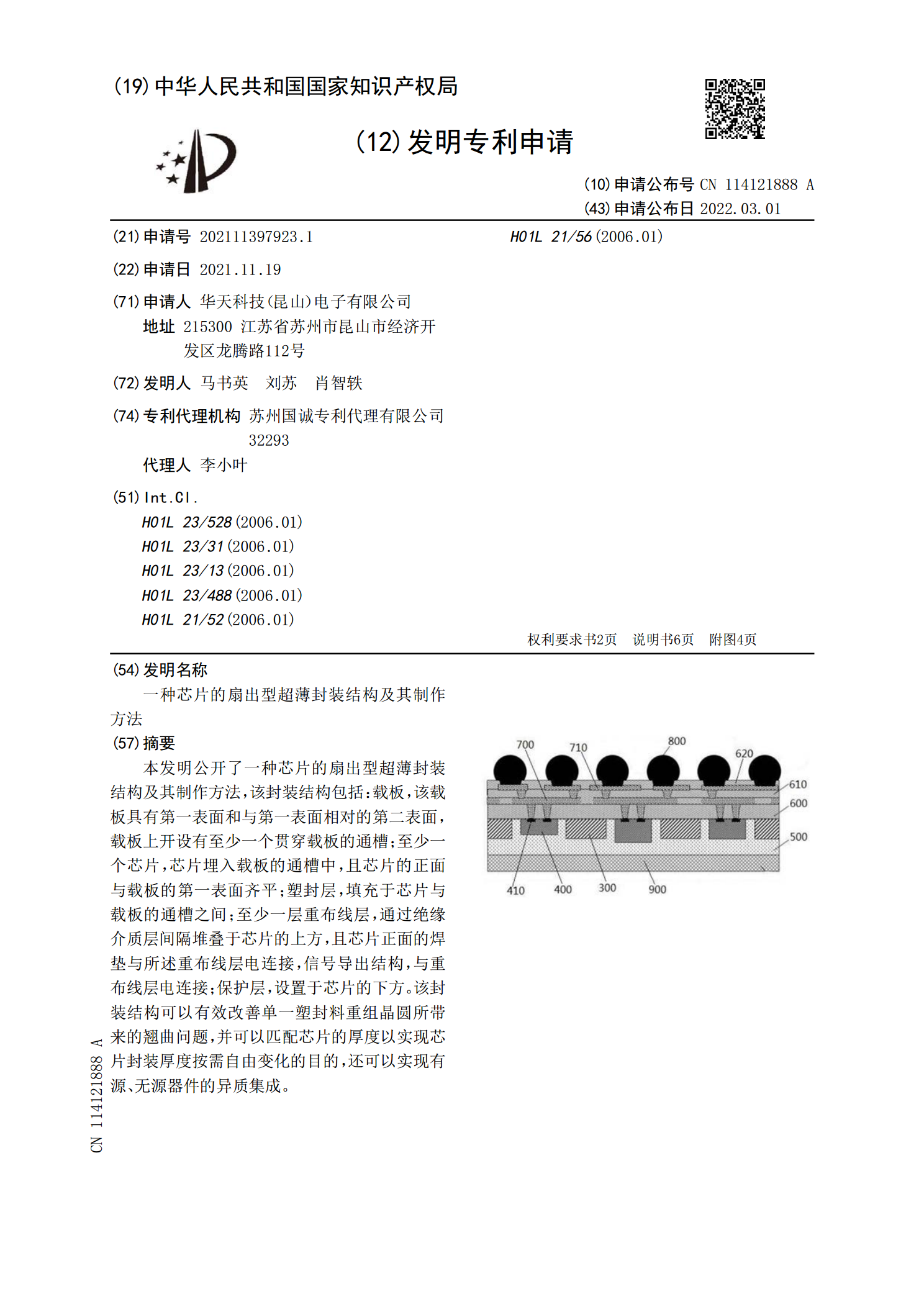

一种芯片的扇出型超薄封装结构及其制作方法.pdf

本发明公开了一种芯片的扇出型超薄封装结构及其制作方法,该封装结构包括:载板,该载板具有第一表面和与第一表面相对的第二表面,载板上开设有至少一个贯穿载板的通槽;至少一个芯片,芯片埋入载板的通槽中,且芯片的正面与载板的第一表面齐平;塑封层,填充于芯片与载板的通槽之间;至少一层重布线层,通过绝缘介质层间隔堆叠于芯片的上方,且芯片正面的焊垫与所述重布线层电连接,信号导出结构,与重布线层电连接;保护层,设置于芯片的下方。该封装结构可以有效改善单一塑封料重组晶圆所带来的翘曲问题,并可以匹配芯片的厚度以实现芯片封装厚度

一种散热型堆叠封装体及其制作方法.pdf

本发明涉及一种散热型堆叠封装体及其制作方法,在本发明的散热型堆叠封装体的制作过程中,通过在所述半导体管芯的上表面的四周边缘处形成一环形沟槽,并在所述半导体管芯的上表面的中间区域形成多个第一盲孔和多个第二盲孔,进而在上述环形沟槽和第一、第二盲孔中填充金属纳米颗粒,即为半导体管芯提供了多条散热路径,便于半导体管芯的快速散热。且通过设置所述第一盲孔的孔径小于所述第二盲孔的孔径,且所述第一盲孔的深度小于所述环形沟槽的深度,相邻所述第一盲孔之间的距离大于所述第一盲孔的直径,相邻所述第二盲孔之间的距离大于所述第二盲孔

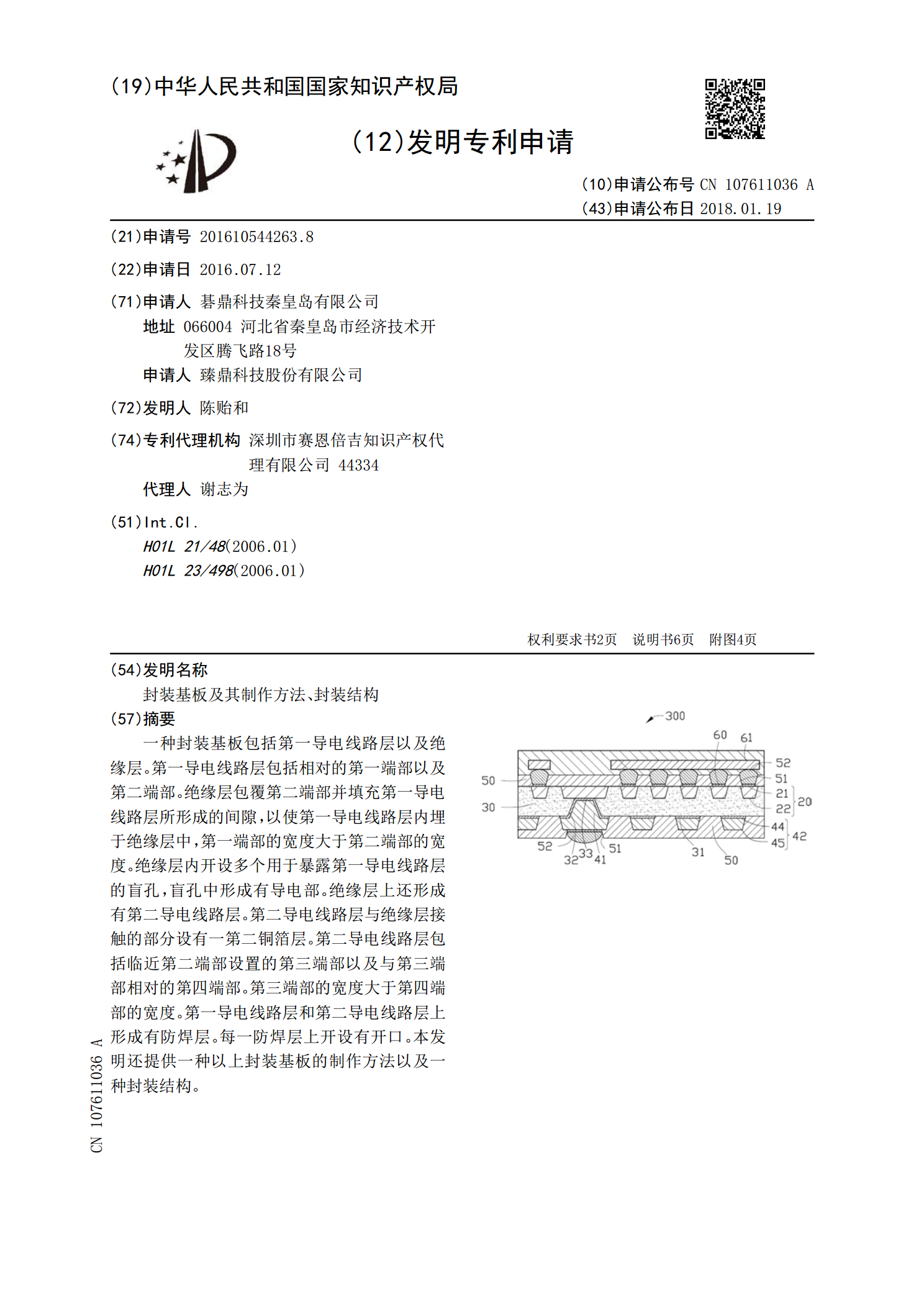

封装基板及其制作方法、封装结构.pdf

一种封装基板包括第一导电线路层以及绝缘层。第一导电线路层包括相对的第一端部以及第二端部。绝缘层包覆第二端部并填充第一导电线路层所形成的间隙,以使第一导电线路层内埋于绝缘层中,第一端部的宽度大于第二端部的宽度。绝缘层内开设多个用于暴露第一导电线路层的盲孔,盲孔中形成有导电部。绝缘层上还形成有第二导电线路层。第二导电线路层与绝缘层接触的部分设有一第二铜箔层。第二导电线路层包括临近第二端部设置的第三端部以及与第三端部相对的第四端部。第三端部的宽度大于第四端部的宽度。第一导电线路层和第二导电线路层上形成有防焊层。