一种雷达信号处理仿真平台及仿真方法.pdf

阳炎****找我

亲,该文档总共23页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种雷达信号处理仿真平台及仿真方法.pdf

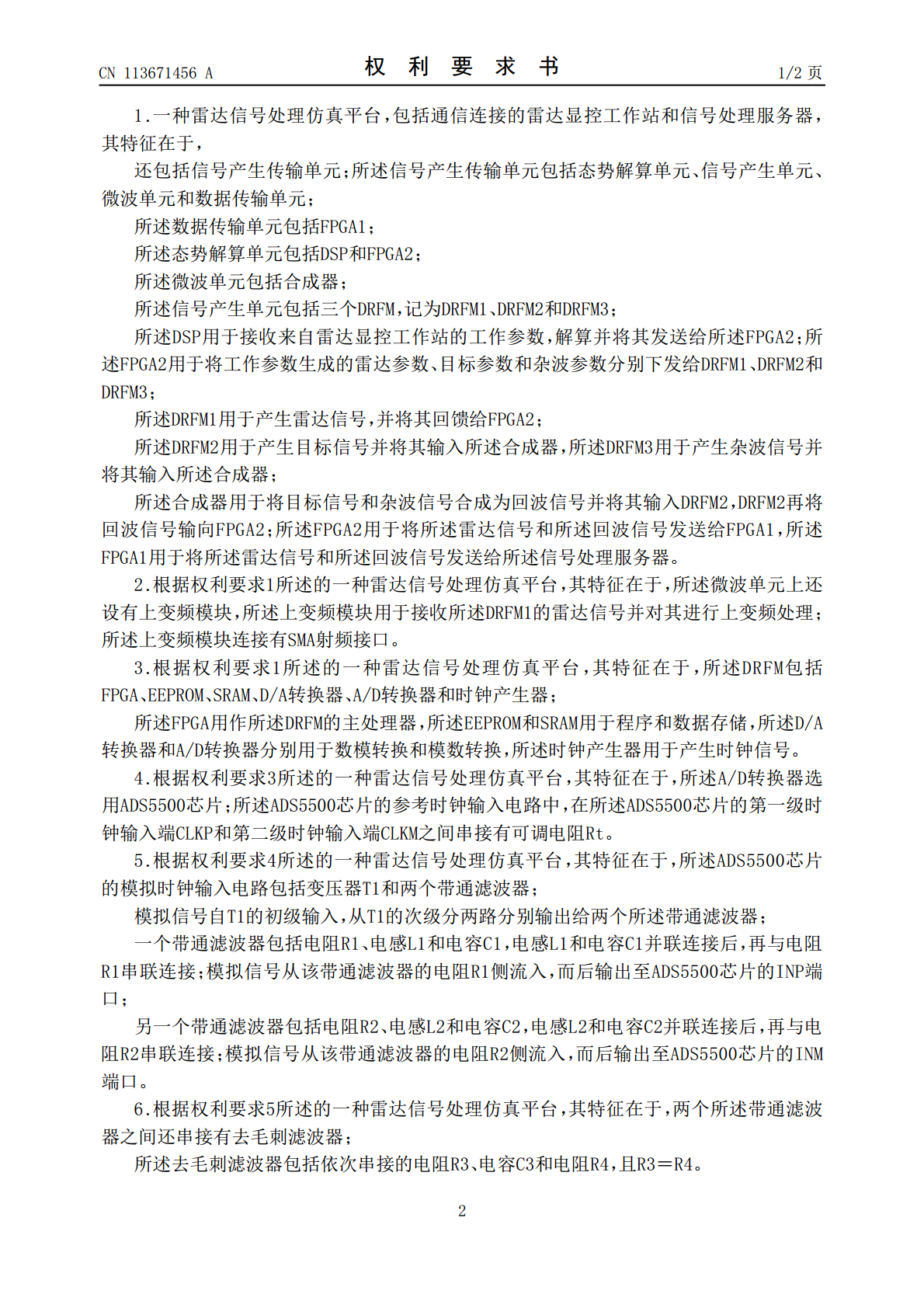

一种雷达信号处理仿真平台及仿真方法。提供了一种能够降低信号干扰、增强通信稳定性的雷达信号处理仿真平台及仿真方法。包括通信连接的雷达显控工作站和信号处理服务器,还包括信号产生传输单元;所述信号产生传输单元包括态势解算单元、信号产生单元、微波单元和数据传输单元;所述数据传输单元包括FPGA1;所述态势解算单元包括DSP和FPGA2;所述信号产生单元包括三个DRFM,记为DRFM1、DRFM2和DRFM3;所述合成器用于将目标信号和杂波信号合成为回波信号并将其输入DRFM2,DRFM2再将回波信号输向FPGA2

使用Matlab仿真雷达信号处理系统.doc

毕业设计(论文)报告纸61摘要运用数字信号处理理论和Matlab软件研究的脉冲压缩多普勒雷达的信号处理仿真问题,提出了一个仿真模型,该模型能够仿真雷达信号、系统噪声与杂波的产生和脉冲压缩多普勒雷达系统中信号的动态处理过程,最后结合MIMO雷达信号特点,显示了使用Matlab仿真雷达信号处理系统方便快捷的特点。关键词:MIMO模糊图脉冲压缩AbstractTheuseofdigitalsignalprocessingtheoryandMatlabsoftwareresearchDopplerradarpul

使用Matlab仿真雷达信号处理系统 精品资料.doc

毕业设计(论文)报告纸84摘要运用数字信号处理理论和Matlab软件研究的脉冲压缩多普勒雷达的信号处理仿真问题,提出了一个仿真模型,该模型能够仿真雷达信号、系统噪声与杂波的产生和脉冲压缩多普勒雷达系统中信号的动态处理过程,最后结合MIMO雷达信号特点,显示了使用Matlab仿真雷达信号处理系统方便快捷的特点。关键词:MIMO模糊图脉冲压缩AbstractTheuseofdigitalsignalprocessingtheoryandMatlabsoftwareresearchDopplerradarpul

雷达信号处理装置、雷达装置及雷达信号处理方法.pdf

碰撞判定部(404)在车辆(1000)与物体(1001)之间的多普勒速度分量变化了第1基准值为止时、或车辆(1000)移动至与第1基准值对应的距离(R)时,判定车辆(1000)是否相对于物体(1001)发生碰撞。

雷达信号处理方法和雷达信号处理装置.pdf

一种雷达信号处理方法和装置,方法包括:获取多路RX信号,对多路RX信号中的每一路RX信号进行距离维谱分析和多普勒维谱分析,得到RD图(S310);根据目标跟踪先验信息,对每一路RX信号的RD图进行相干处理,对多路RX信号的相干处理后的RD图进行相干叠加(S320);根据多路RX信号相干叠加后的RD图,进行目标检测(S330);方法基于目标跟踪先验信息对多路RX信号的RDmap进行相干处理进而进行相干叠加,可以提高RX信号的合并增益,即相干处理和相干叠加能够使得叠加的接收信号相位尽可能符合相干条件,使得叠