使用硬掩模的半导体器件及其制造方法.pdf

一只****呀盟

亲,该文档总共43页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

使用硬掩模的半导体器件及其制造方法.pdf

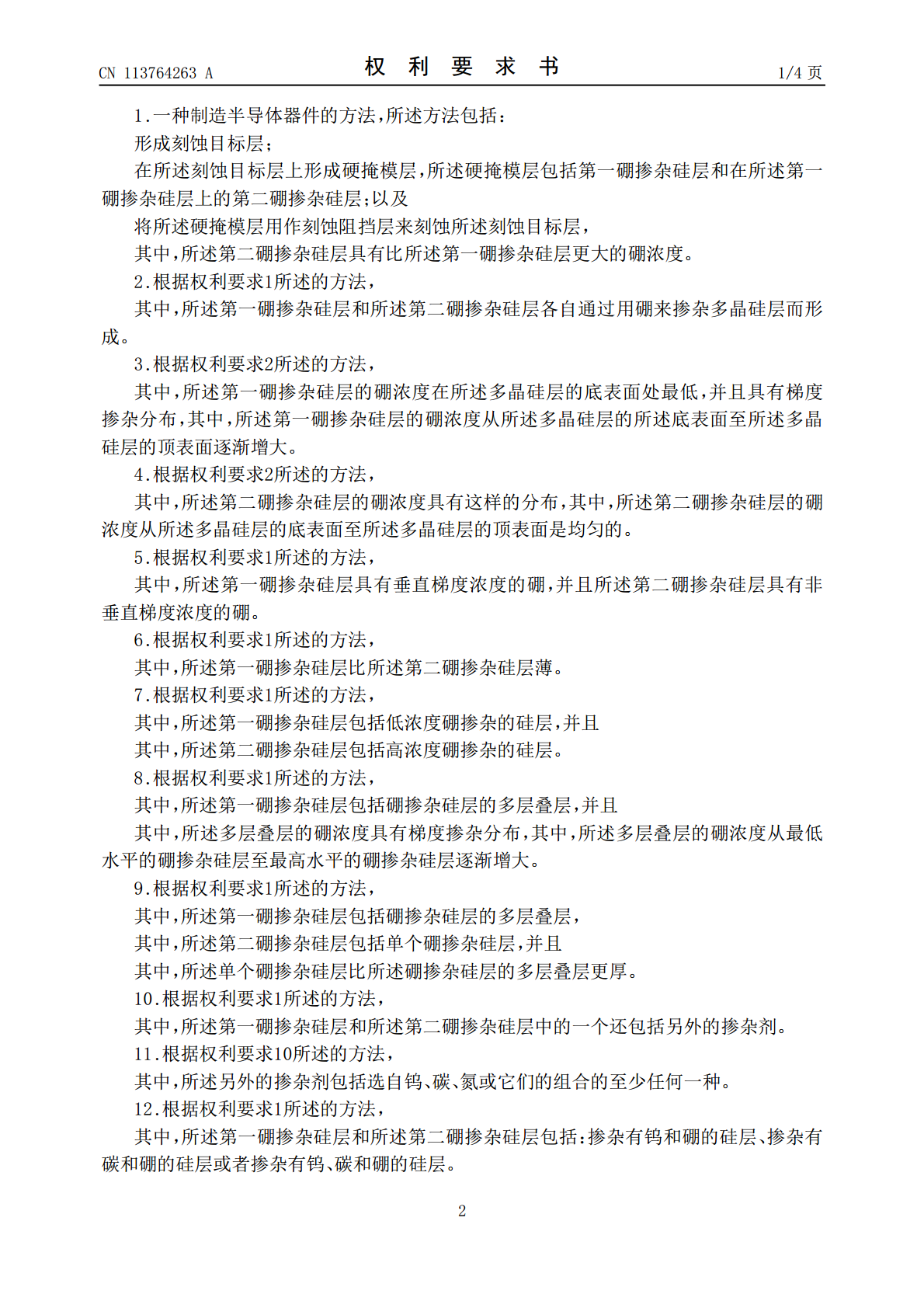

该技术涉及一种使用硬掩模的半导体器件及其制造方法,该半导体器件包括易于剥离并且能够以高的刻蚀选择性实现精细图案的硬掩模。根据本公开的实施例,一种制造半导体器件的方法包括:形成刻蚀目标层;在刻蚀目标层上形成硬掩模层,该硬掩模层包括第一硼掺杂硅层和在第一硼掺杂硅层上的第二硼掺杂硅层;并且将硬掩模层用作刻蚀阻挡层而对刻蚀目标层进行刻蚀,其中第二硼掺杂硅层具有比第一硼掺杂硅层更大的硼浓度。

掩模坯料、转印用掩模的制造方法及半导体器件的制造方法.pdf

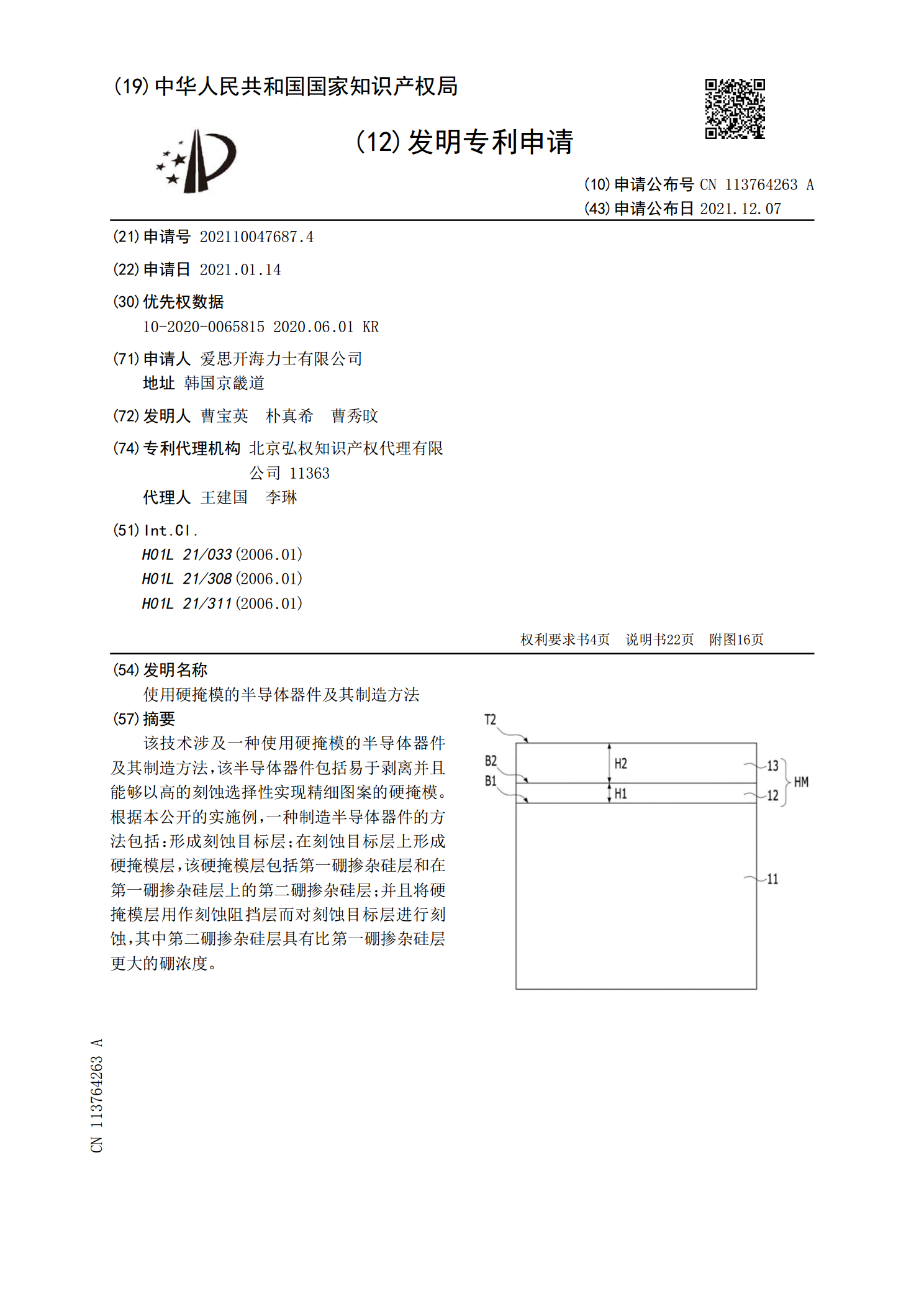

本发明的目的在于,提供一种能够以良好的精度制作具有20nm左右这样的微小尺寸的辅助图案的转印用掩模的掩模坯料。上述掩模坯料具有以下结构:在基板(1)的主表面上依次层叠有图案形成用薄膜(2)、第1硬掩模膜(3)、第2硬掩模膜(4),其中,图案形成用薄膜含有过渡金属,第1硬掩模膜含有氧和选自硅及钽中的一种以上元素,第2硬掩模膜含有过渡金属,第2硬掩模膜的过渡金属的含量比上述图案形成用薄膜的过渡金属的含量少,主表面上的形成有第1硬掩模膜的区域比形成有图案形成用薄膜的区域小,第2硬掩模膜与图案形成用薄膜至少部分地

包括硬掩模结构的半导体器件.pdf

提供了一种半导体器件。所述半导体器件包括:晶片;蚀刻停止层,位于所述晶片上;下模制层,位于所述蚀刻停止层上;中间支撑物层,位于所述下模制层上;上模制层,位于所述中间支撑物层上;上支撑物层,位于所述上模制层上;以及硬掩模结构,位于所述上支撑物层上,其中,所述硬掩模结构包括位于所述上支撑物层上的第一硬掩模层和位于所述第一硬掩模层上的第二硬掩模层,所述第一硬掩模层和所述第二硬掩模层中的一者包括第一有机层,所述第一有机层包括包含C、H、O和N的SOH,并且所述第一硬掩模层和所述第二硬掩模层中的另一者包括第二有机层

掩模坯料、转印用掩模及半导体器件的制造方法.pdf

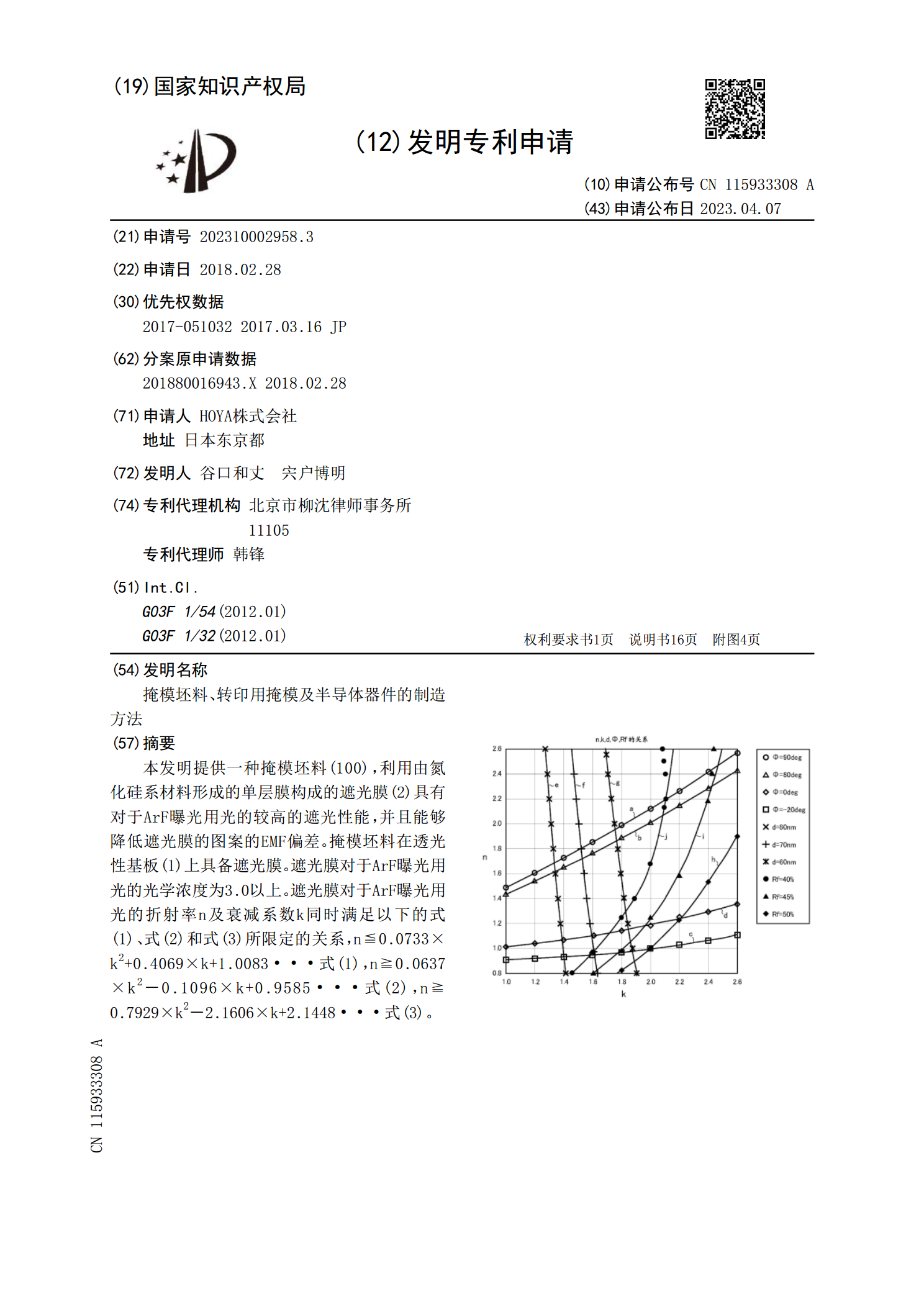

本发明提供一种掩模坯料(100),利用由氮化硅系材料形成的单层膜构成的遮光膜(2)具有对于ArF曝光用光的较高的遮光性能,并且能够降低遮光膜的图案的EMF偏差。掩模坯料在透光性基板(1)上具备遮光膜。遮光膜对于ArF曝光用光的光学浓度为3.0以上。遮光膜对于ArF曝光用光的折射率n及衰减系数k同时满足以下的式(1)、式(2)和式(3)所限定的关系,n≦0.0733×k

掩模坯料、转印用掩模及半导体器件的制造方法.pdf

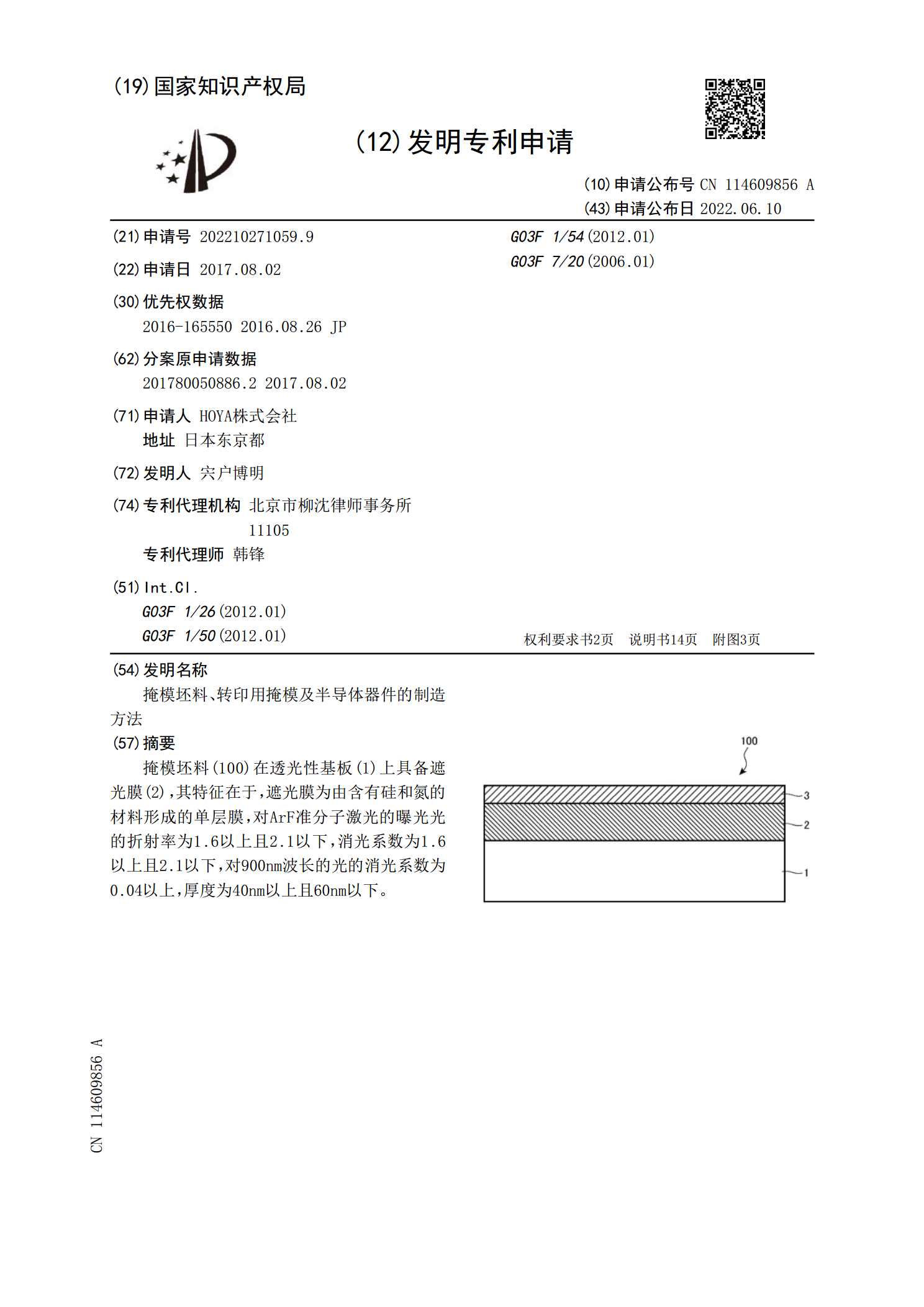

掩模坯料(100)在透光性基板(1)上具备遮光膜(2),其特征在于,遮光膜为由含有硅和氮的材料形成的单层膜,对ArF准分子激光的曝光光的折射率为1.6以上且2.1以下,消光系数为1.6以上且2.1以下,对900nm波长的光的消光系数为0.04以上,厚度为40nm以上且60nm以下。