片上系统芯片、测试方法及测试系统.pdf

小寄****淑k

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

片上系统芯片、测试方法及测试系统.pdf

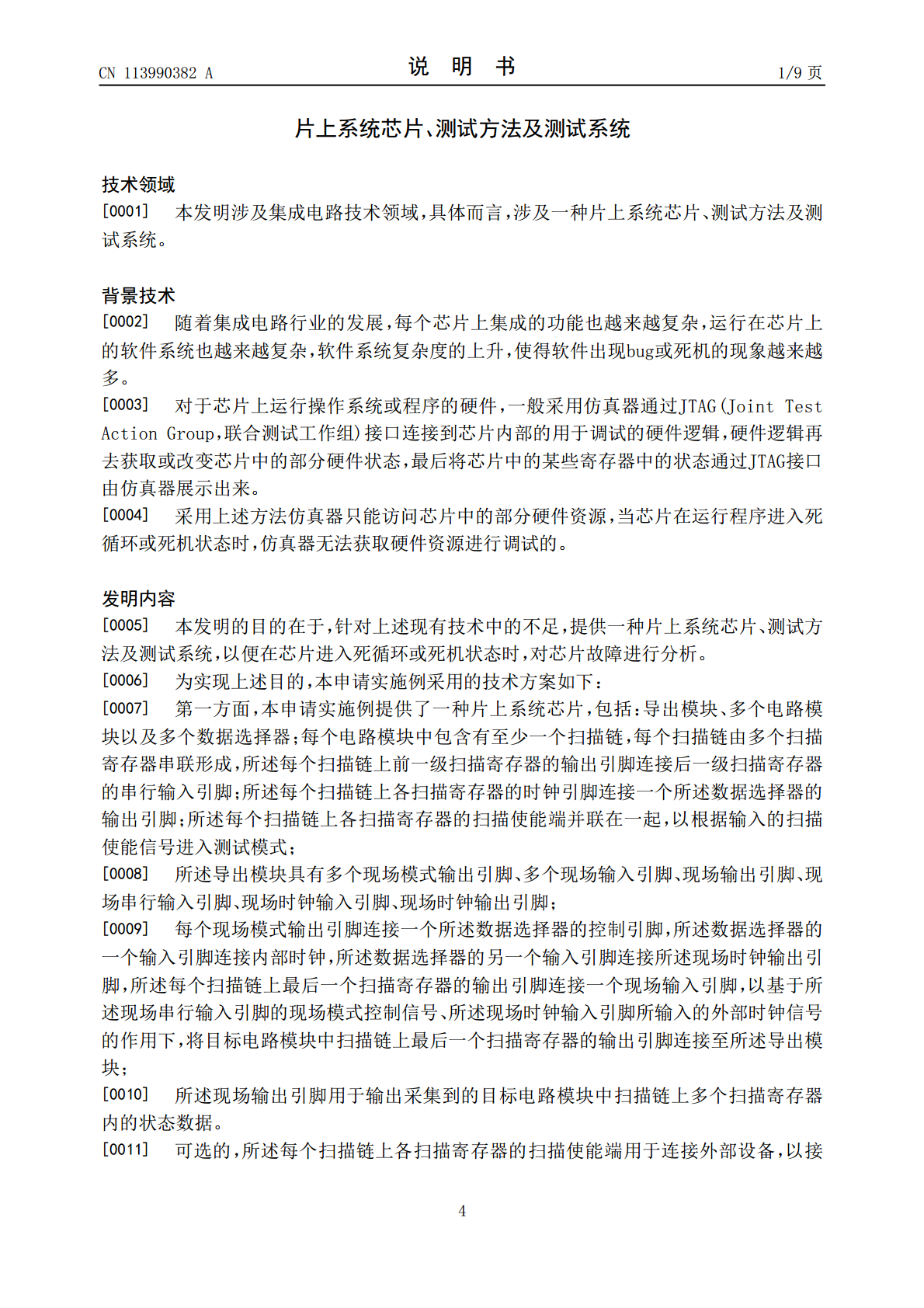

本申请提供一种片上系统芯片、测试方法及测试系统,涉及集成电路技术领域。该片上系统芯片包括:导出模块、多个电路模块以及多个数据选择器;每个电路模块中包含有至少一个扫描链,每个扫描链由多个扫描寄存器串联形成,每个扫描链各扫描寄存器的时钟引脚连接一个数据选择器的输出引脚,各扫描寄存器的扫描使能端并联在一起,根据扫描使能信号进入测试模式;现场模式输出引脚连接数据选择器的控制引脚,数据选择器的一个输入引脚连接内部时钟,另一个输入引脚连接现场时钟输出引脚,最后一个扫描寄存器的输出引脚连接现场输入引脚,现场输出引脚用于

-系统芯片与片上通信结构.pptx

微处理器芯片的集成度不断提高未来单个芯片内将集成几百上千处理单元和存储单元•规定总线信号的逻辑电地址递增的4个数据的传输如何实现“分布式译码”?四、片上通信结构的新发展一个包含AHB和PCI总线的系统实例•规定模块插件的机械尺•给出各总线信号的名称及功能定义HBURST[2:0]•规定模块插件的机械尺2013~2015年?四、片上通信结构新发展*IEEEComputerSocietyAnnualSymposiumonVLSI,2002.PCI总线的分布式译码*IEEEComputerSocietyA

CPU功耗测试设备、方法、系统、控制芯片及测试芯片.pdf

本说明书公开了一种CPU功耗测试设备、方法、系统、控制芯片及测试芯片。首先,通过利用控制芯片的第一片内总线、第一通用输入输出控制器、片间总线、测试芯片的第二片内总线建立控制用CPU和测试芯片的第二存储单元之间的连接,接着,利用控制用CPU从控制芯片的第一存储单元中读取测试程序,且控制用CPU可以通过第一通用输入输出控制器和所述片间总线将读取到的测试程序写入至测试芯片的第二存储单元,实现针对CPU的功耗测试所需的快速方便的测试平台的构建,提升了测试平台重复使用性和广泛适配性。

片上系统在应变测试系统中的应用.docx

片上系统在应变测试系统中的应用IntroductionTheconceptofSystemonChip(SoC)hasenabledtheintegrationofcomplexelectronicsystemsintoasinglechip,providingsignificantbenefitssuchasreducedsize,powerconsumption,andcost.OneofthekeyareaswhereSoChasfoundapplicationsisinthefieldofstra

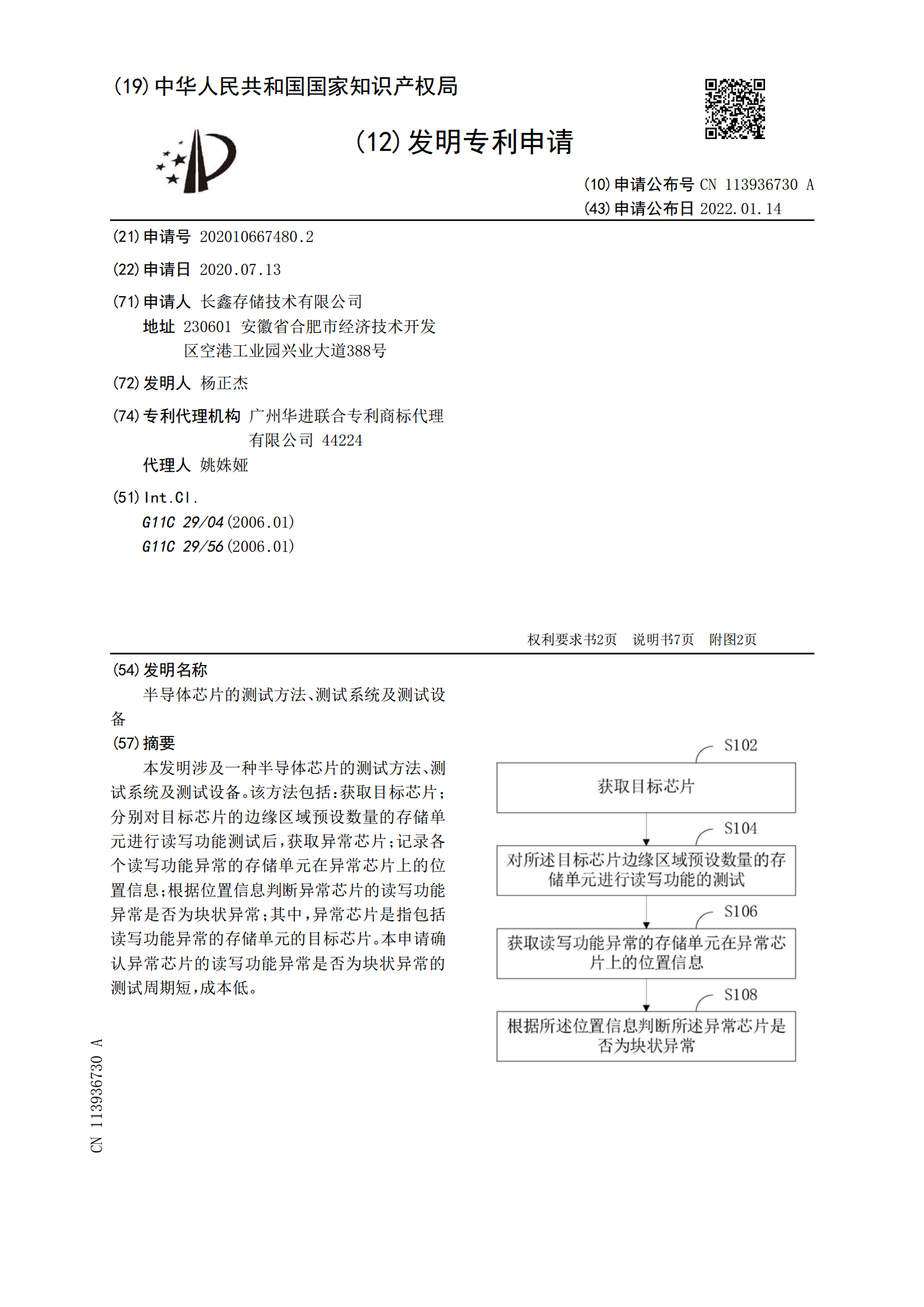

半导体芯片的测试方法、测试系统及测试设备.pdf

本发明涉及一种半导体芯片的测试方法、测试系统及测试设备。该方法包括:获取目标芯片;分别对目标芯片的边缘区域预设数量的存储单元进行读写功能测试后,获取异常芯片;记录各个读写功能异常的存储单元在异常芯片上的位置信息;根据位置信息判断异常芯片的读写功能异常是否为块状异常;其中,异常芯片是指包括读写功能异常的存储单元的目标芯片。本申请确认异常芯片的读写功能异常是否为块状异常的测试周期短,成本低。