封装结构及其制造方法.pdf

一吃****昕靓

亲,该文档总共25页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

封装结构及其制造方法.pdf

一种封装结构及其制造方法,包括芯片、重布线路结构、成型模料结构以及电磁干扰遮蔽结构。所述重布线路结构设置在所述芯片上并形成电性连接。所述成型模料结构环绕所述芯片以及所述重布线路结构的外围设置。所述电磁干扰遮蔽结构环绕所述成型模料结构的外围设置。通过所述成型模料结构环绕所述芯片以及所述重布线路结构的外围设置,以提供对结构的多面保护及强化。通过所述电磁干扰遮蔽结构环绕所述成型模料结构的外围设置,以提供对所述芯片以及所述重布线路结构的多面电磁干扰防护。借此达到提升结构强度以及使用可靠性、稳定性的目的。

封装结构及其制造方法.pdf

本公开实施例涉及半导体领域,提供一种封装结构及其制造方法,封装结构包括:基板;中介层,中介层位于基板上方;第一芯片,第一芯片位于中介层上方,第一芯片具有相对的第一面和第二面,第一面朝向中介层;第二芯片,第二芯片至少位于第一芯片远离中介层的表面上,第二芯片在基板表面的正投影面积小于第一芯片在基板表面的正投影面积,第二芯片具有相对的第三面和第四面,第三面朝向基板。至少可以解决封装结构的整体尺寸不具有统一标准的问题。

封装结构及其制造方法.pdf

本发明是关于一种封装结构以及其制造方法。该封装结构包含一基材层、多个芯片、一复合树脂层以及一支撑层。该基材层形成有一电路,该电路具有多个接点,自一防焊层显露出来。这些芯片结合至该基材层上,以形成一第一带体。其中,各该芯片具有多个接垫、形成于这些接垫上的多个凸块下金属层以及设置于这些凸块下金属层上的多个复合凸块。该第二带体包含支撑层及形成于支撑层上的复合树脂层。又第一带体与第二带体皆为卷带结构受滚轮传动展开,以于被加热和加压后封装这些芯片。本发明的优点是:可通过减少金的使用,以降低制造成本;其工艺可运用于大

封装结构及其制造方法.pdf

提供了一种封装结构及其制造方法,该封装结构包括:多个谐振腔,在衬底中;堆叠结构,在多个谐振腔上,包括下电极、功能层和上电极;封装层,至少在堆叠结构上,包括重叠了堆叠结构的空腔;电连接结构,在多个谐振腔周围,至少穿过封装层与下电极电连接。依照本发明的封装结构及其制造方法,采用低温工艺形成封装层,降低了封装高度,减小了封装残留应力,提高了可靠性。

封装结构及其制造方法.pdf

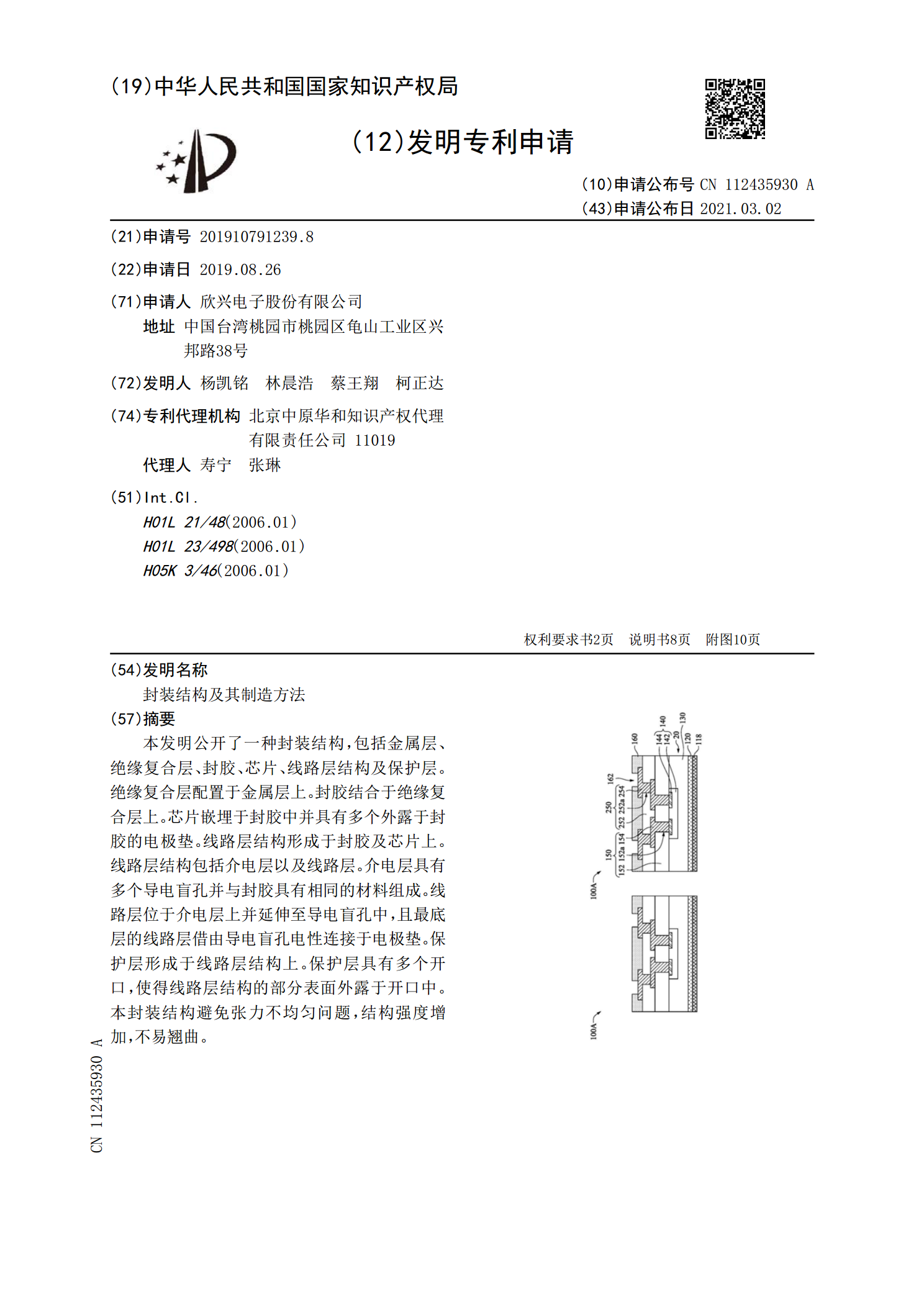

本发明公开了一种封装结构,包括金属层、绝缘复合层、封胶、芯片、线路层结构及保护层。绝缘复合层配置于金属层上。封胶结合于绝缘复合层上。芯片嵌埋于封胶中并具有多个外露于封胶的电极垫。线路层结构形成于封胶及芯片上。线路层结构包括介电层以及线路层。介电层具有多个导电盲孔并与封胶具有相同的材料组成。线路层位于介电层上并延伸至导电盲孔中,且最底层的线路层借由导电盲孔电性连接于电极垫。保护层形成于线路层结构上。保护层具有多个开口,使得线路层结构的部分表面外露于开口中。本封装结构避免张力不均匀问题,结构强度增加,不易翘曲