一种基于FPGA的数据处理方法、装置、设备及介质.pdf

宁馨****找我

亲,该文档总共20页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种基于FPGA的数据处理方法、装置、设备及介质.pdf

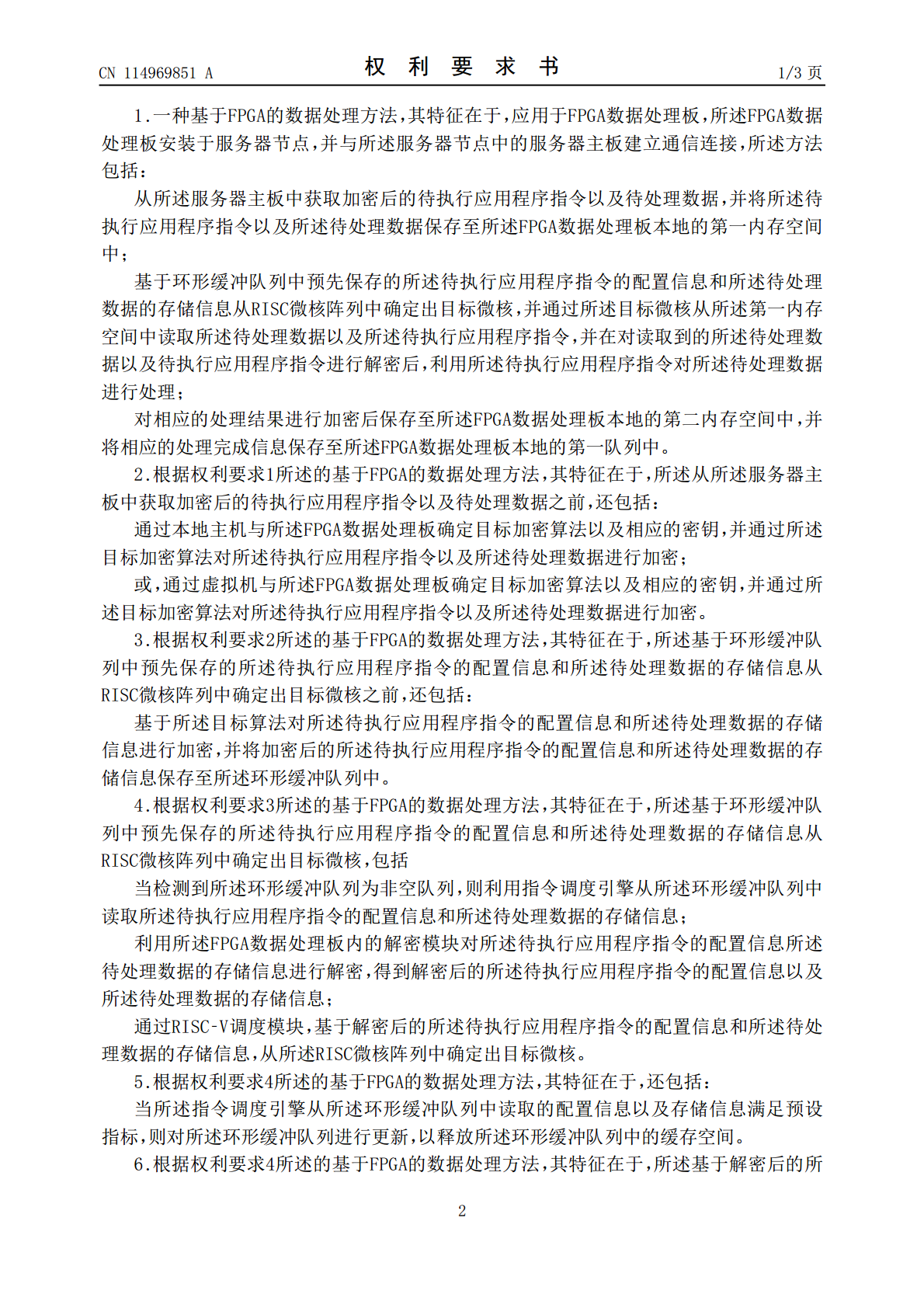

本申请公开了一种基于FPGA的数据处理方法、装置、设备及介质,涉及计算机技术领域,所述方法包括:将从服务器主板中获取的加密后的指令以及数据保存至FPGA数据处理板本地的第一内存空间中;基于指令的配置信息和数据的存储信息确定出目标微核,并通过目标微核从第一内存空间中读取数据以及指令,在对读取到的数据以及指令进行解密后,利用指令对数据进行处理;对相应的处理结果进行加密后保存至FPGA数据处理板本地的第二内存空间中。可见,本申请中数据、指令以及处理结果均以加密的方式在服务器主板与FPGA数据处理板之间进行传输,

基于FPGA的数据处理方法、装置、设备及存储介质.pdf

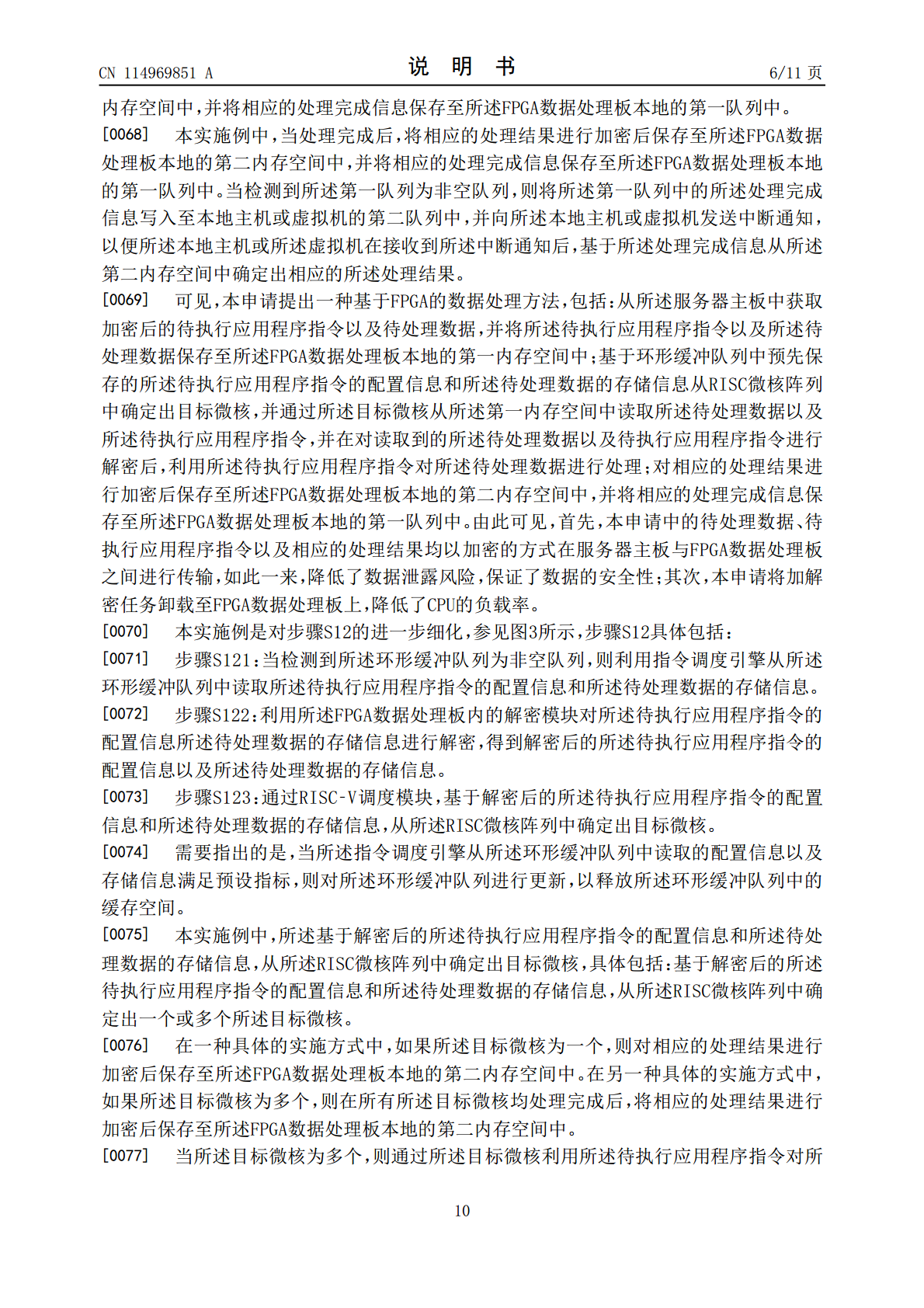

本申请提供一种基于FPGA的数据处理方法、装置、设备及存储介质。该FPGA包括多个算法核,其中,算法核数量预先设定,每个算法核均包括处理算法,且多个算法核能够对数据进行并行处理;该方法包括:接收待处理数据;确定处于空闲状态的目标算法核;利用目标算法核中的处理算法对待处理数据进行处理;获得目标算法核输出的处理结果,并将处理结果进行存储。本申请实施例通过不同应用场景需求,预先定义多个算法核,并且通过多个算法核对待处理数据并行处理,在满足处理算法对带宽要求的前提下,尽可能降低对FPGA资源的消耗。

基于FPGA的字节对齐方法、装置、设备及存储介质.pdf

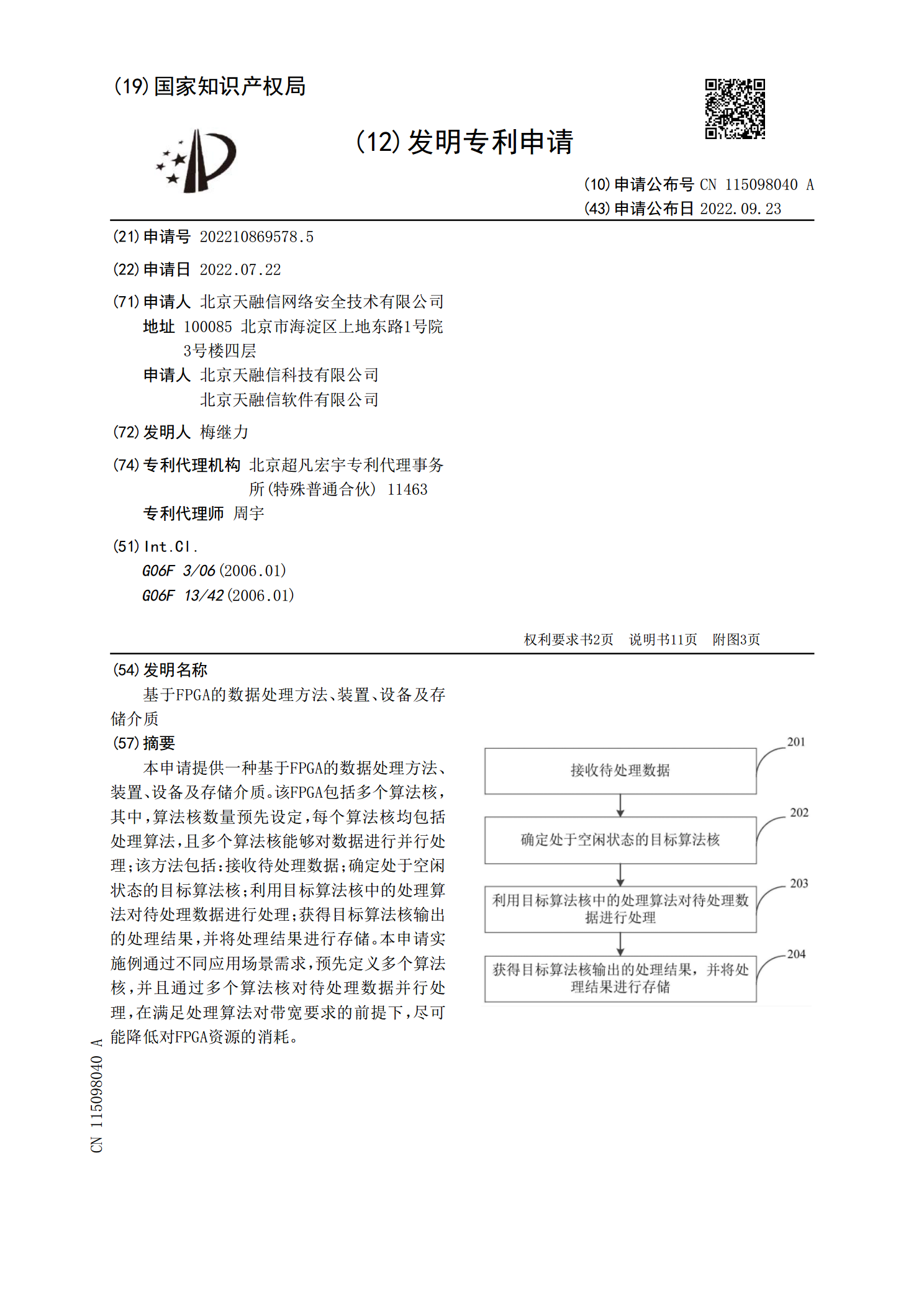

本发明公开了一种基于FPGA的字节对齐方法、装置、设备及存储介质,该方法包括:接收串行数据流,串行数据流包括标志位,串行数据流是通过发送端的FPGA中内置的SERDES收发器将第一并行数据流转换得到,第一并行数据流包括多个并行传输二进制码的第一数据位,标志位为任意一个第一数据位,除标志位外的第一数据位用于传输有效载荷;通过接收端FPGA中内置的SERDES收发器将串行数据流转换为第二并行数据流;查询标志位在第二并行数据流中的位置,作为目标位置;基于目标位置对第二并行数据流进行字节调整,以使第二并行数据流与

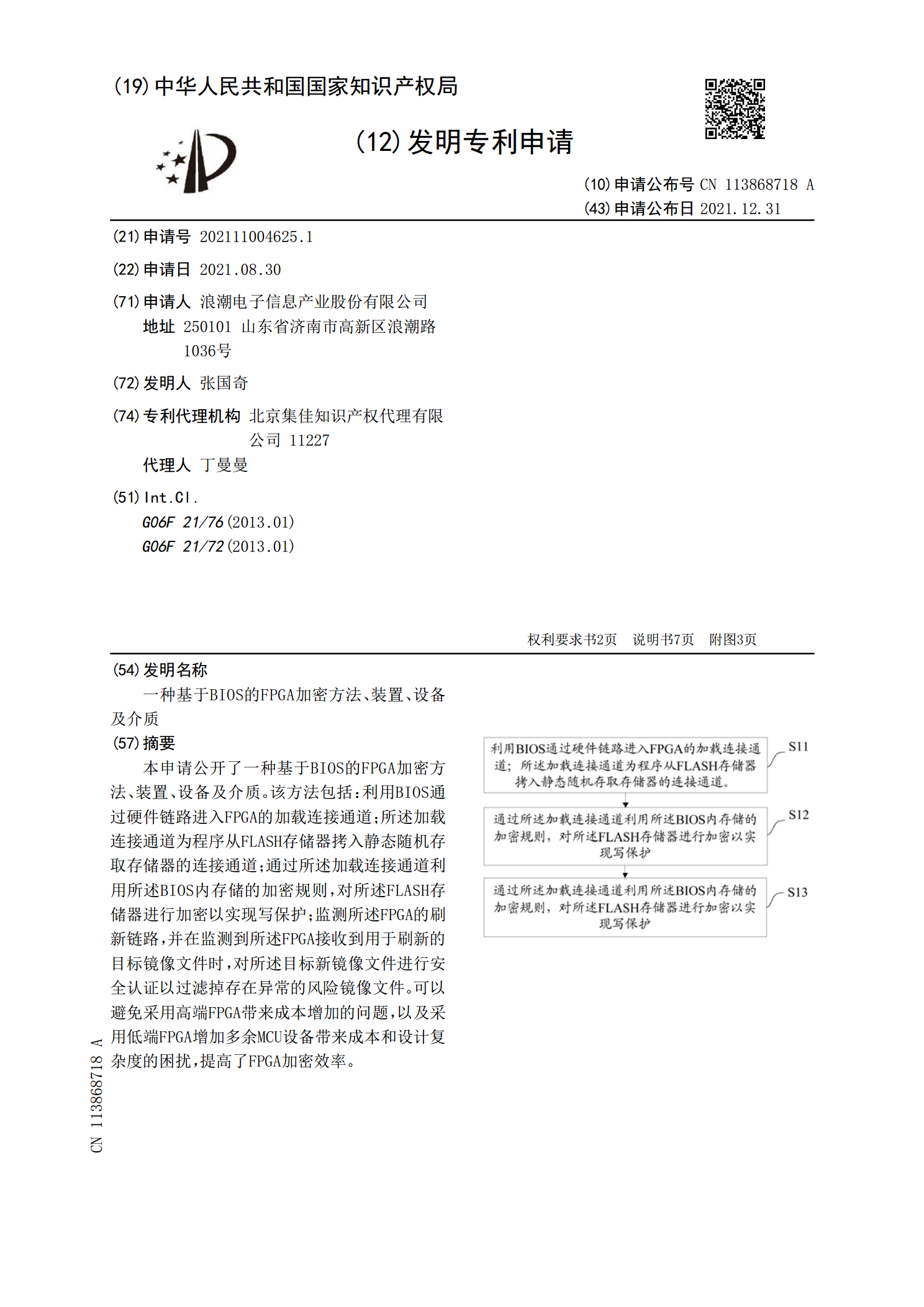

一种基于BIOS的FPGA加密方法、装置、设备及介质.pdf

本申请公开了一种基于BIOS的FPGA加密方法、装置、设备及介质。该方法包括:利用BIOS通过硬件链路进入FPGA的加载连接通道;所述加载连接通道为程序从FLASH存储器拷入静态随机存取存储器的连接通道;通过所述加载连接通道利用所述BIOS内存储的加密规则,对所述FLASH存储器进行加密以实现写保护;监测所述FPGA的刷新链路,并在监测到所述FPGA接收到用于刷新的目标镜像文件时,对所述目标新镜像文件进行安全认证以过滤掉存在异常的风险镜像文件。可以避免采用高端FPGA带来成本增加的问题,以及采用低端FPG

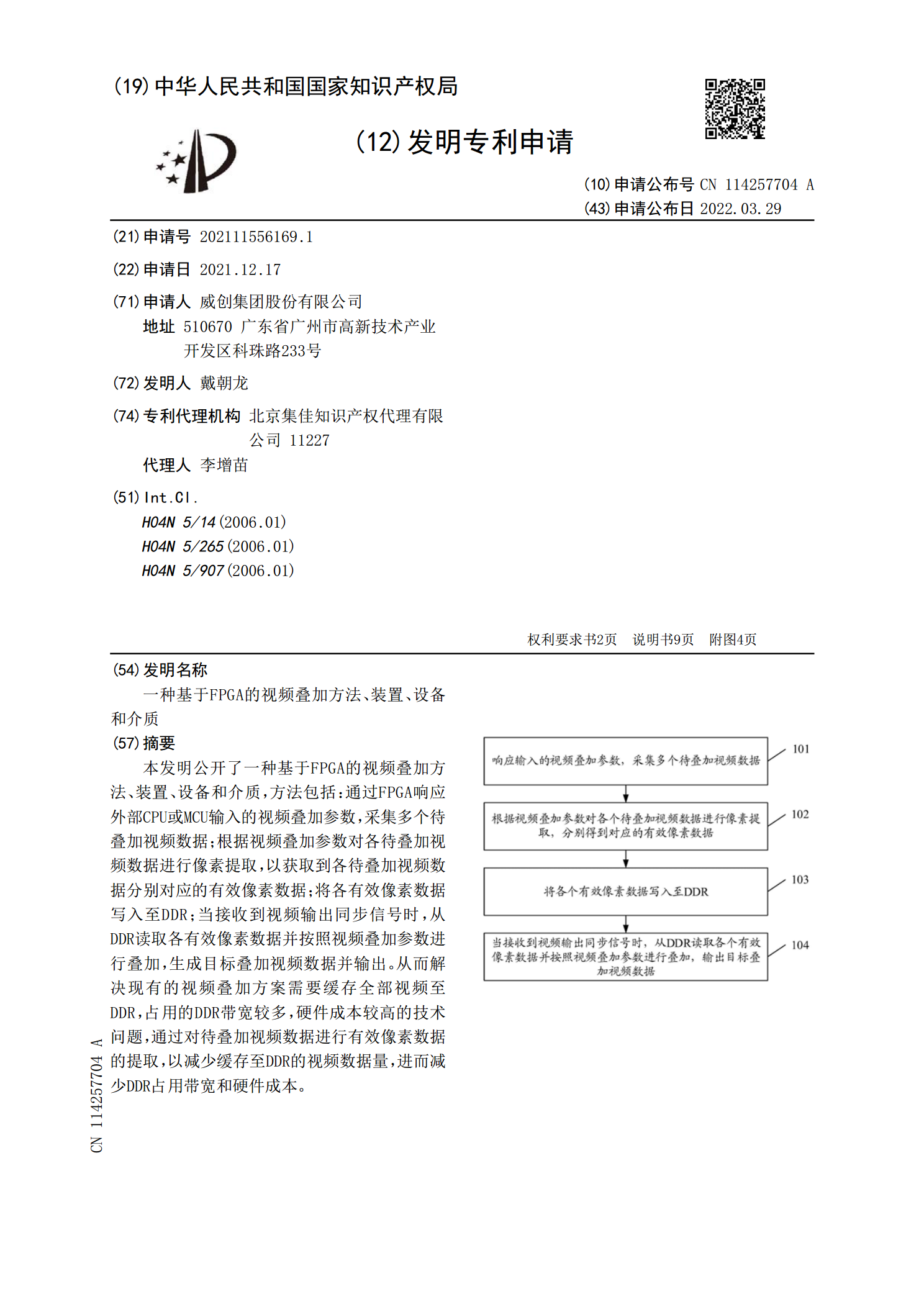

一种基于FPGA的视频叠加方法、装置、设备和介质.pdf

本发明公开了一种基于FPGA的视频叠加方法、装置、设备和介质,方法包括:通过FPGA响应外部CPU或MCU输入的视频叠加参数,采集多个待叠加视频数据;根据视频叠加参数对各待叠加视频数据进行像素提取,以获取到各待叠加视频数据分别对应的有效像素数据;将各有效像素数据写入至DDR;当接收到视频输出同步信号时,从DDR读取各有效像素数据并按照视频叠加参数进行叠加,生成目标叠加视频数据并输出。从而解决现有的视频叠加方案需要缓存全部视频至DDR,占用的DDR带宽较多,硬件成本较高的技术问题,通过对待叠加视频数据进行有