兼容CMOS工艺的体声波谐振器及其制造方法.pdf

玉怡****文档

亲,该文档总共47页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

兼容CMOS工艺的体声波谐振器及其制造方法.pdf

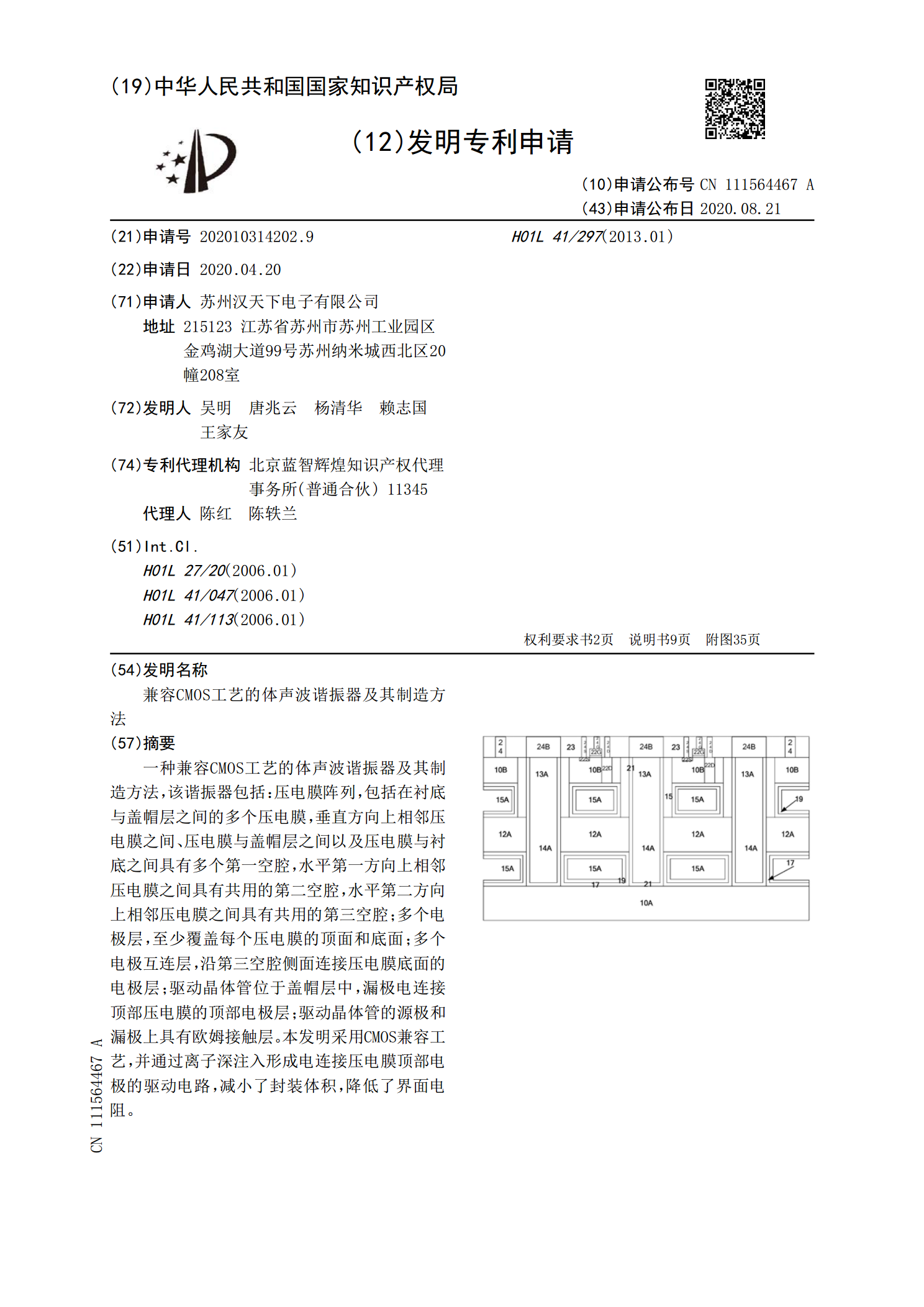

一种兼容CMOS工艺的体声波谐振器及其制造方法,该谐振器包括:压电膜阵列,包括在衬底与盖帽层之间的多个压电膜,垂直方向上相邻压电膜之间、压电膜与盖帽层之间以及压电膜与衬底之间具有多个第一空腔,水平第一方向上相邻压电膜之间具有共用的第二空腔,水平第二方向上相邻压电膜之间具有共用的第三空腔;多个电极层,至少覆盖每个压电膜的顶面和底面;多个电极互连层,沿第三空腔侧面连接压电膜底面的电极层;驱动晶体管位于盖帽层中,漏极电连接顶部压电膜的顶部电极层;驱动晶体管的源极和漏极上具有欧姆接触层。本发明采用CMOS兼容工艺

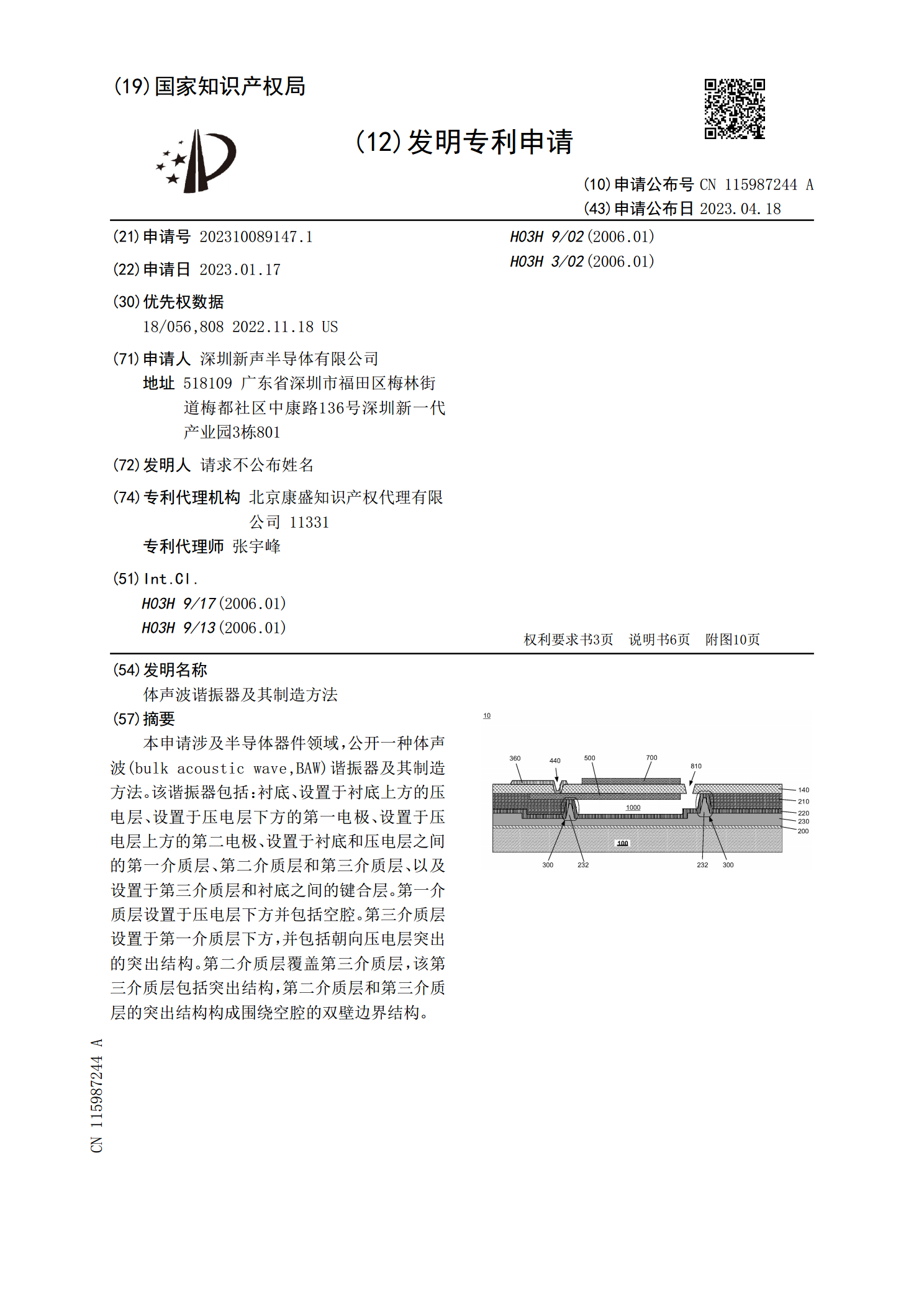

体声波谐振器及其制造方法.pdf

本申请涉及半导体器件领域,公开一种体声波(bulkacousticwave,BAW)谐振器及其制造方法。该谐振器包括:衬底、设置于衬底上方的压电层、设置于压电层下方的第一电极、设置于压电层上方的第二电极、设置于衬底和压电层之间的第一介质层、第二介质层和第三介质层、以及设置于第三介质层和衬底之间的键合层。第一介质层设置于压电层下方并包括空腔。第三介质层设置于第一介质层下方,并包括朝向压电层突出的突出结构。第二介质层覆盖第三介质层,该第三介质层包括突出结构,第二介质层和第三介质层的突出结构构成围绕空腔的双

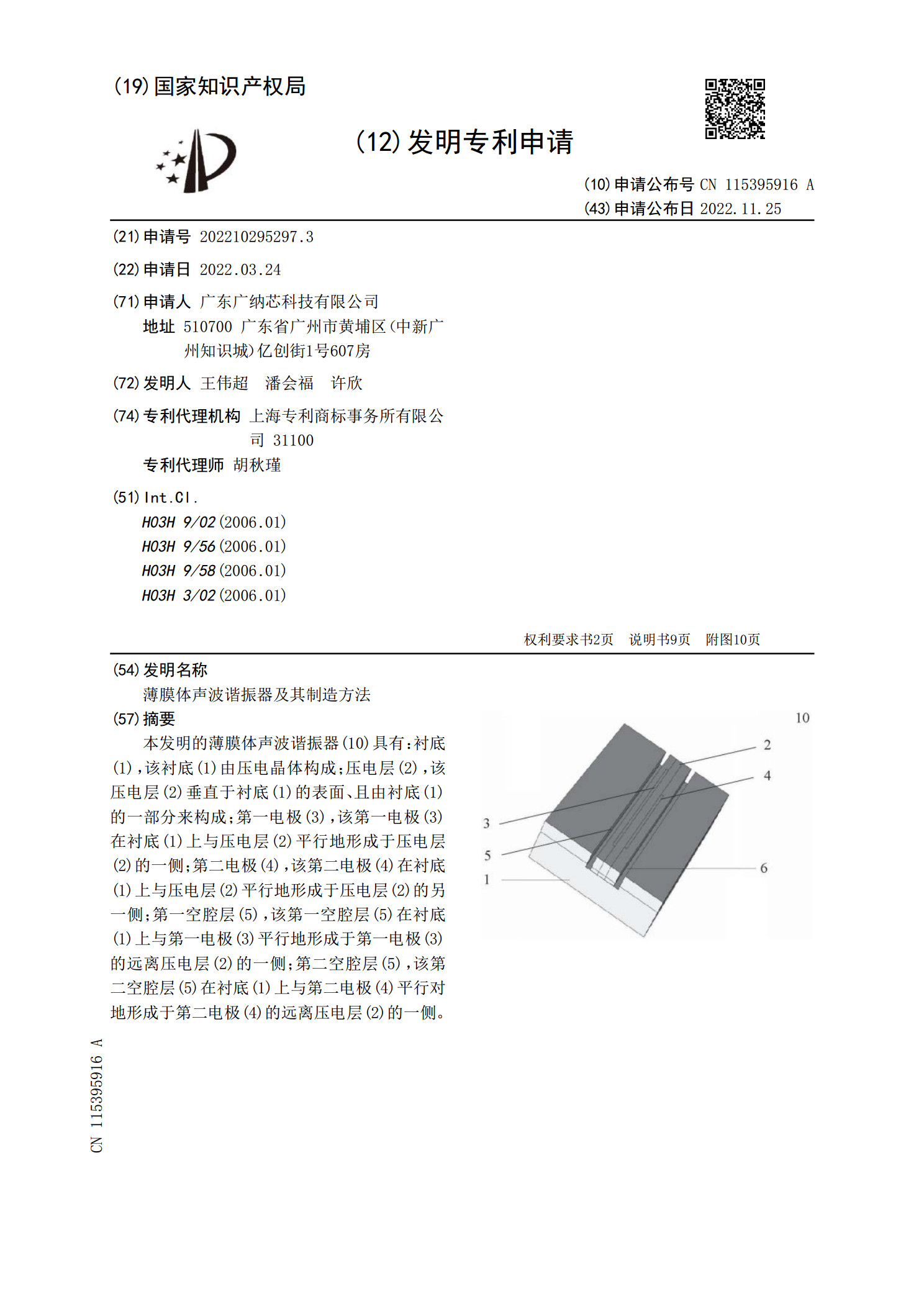

薄膜体声波谐振器及其制造方法.pdf

本发明的薄膜体声波谐振器(10)具有:衬底(1),该衬底(1)由压电晶体构成;压电层(2),该压电层(2)垂直于衬底(1)的表面、且由衬底(1)的一部分来构成;第一电极(3),该第一电极(3)在衬底(1)上与压电层(2)平行地形成于压电层(2)的一侧;第二电极(4),该第二电极(4)在衬底(1)上与压电层(2)平行地形成于压电层(2)的另一侧;第一空腔层(5),该第一空腔层(5)在衬底(1)上与第一电极(3)平行地形成于第一电极(3)的远离压电层(2)的一侧;第二空腔层(5),该第二空腔层(5)在衬底(1

一种体声波谐振器的制造工艺和体声波谐振器.pdf

公开了一种体声波谐振器的制造工艺,包括在衬底上制作声反射镜,在衬底上制作用于覆盖声反射镜的底电极层;对底电极层的外围部分进行化学处理以形成改性层,改性层环绕底电极层;在底电极层上制作压电层;在压电层上制作顶电极层。还公开了一种体声波谐振器,包括衬底、形成在衬底上的声反射镜以及依次形成具有声反射镜的衬底上的底电极层、压电层和顶电极层,其中底电极层的临近声反射镜的边缘的部分被化学处理以形成改性层。凭借改性层的形成削弱或消除了有效工作区域外电极之间的电场强度,电极无法激励其间的压电层产生机械波而抑制了谐振器寄生

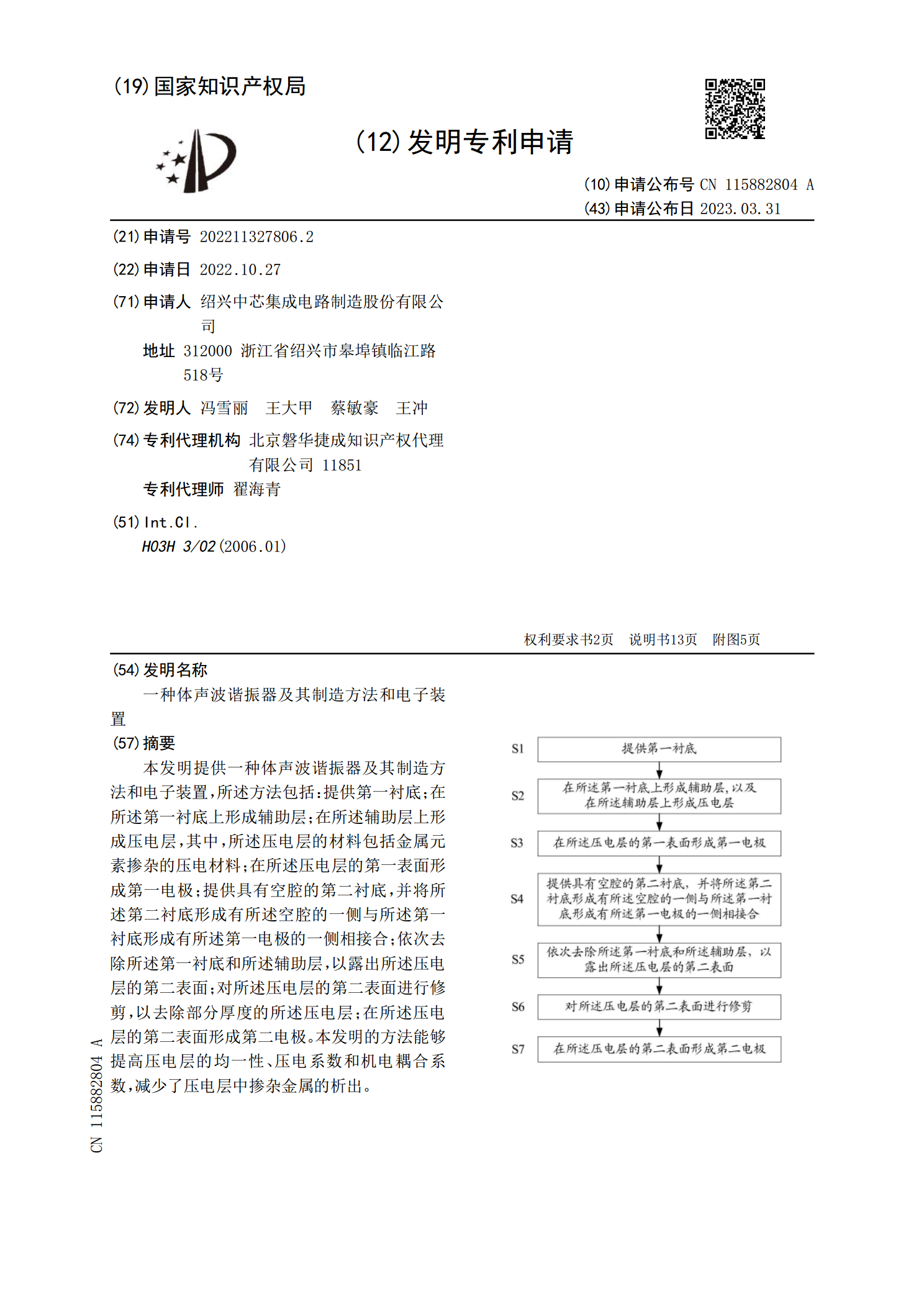

一种体声波谐振器及其制造方法和电子装置.pdf

本发明提供一种体声波谐振器及其制造方法和电子装置,所述方法包括:提供第一衬底;在所述第一衬底上形成辅助层;在所述辅助层上形成压电层,其中,所述压电层的材料包括金属元素掺杂的压电材料;在所述压电层的第一表面形成第一电极;提供具有空腔的第二衬底,并将所述第二衬底形成有所述空腔的一侧与所述第一衬底形成有所述第一电极的一侧相接合;依次去除所述第一衬底和所述辅助层,以露出所述压电层的第二表面;对所述压电层的第二表面进行修剪,以去除部分厚度的所述压电层;在所述压电层的第二表面形成第二电极。本发明的方法能够提高压电层的