具有电介质帽盖层和蚀刻停止层堆叠的互连结构.pdf

书生****22

亲,该文档总共32页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

具有电介质帽盖层和蚀刻停止层堆叠的互连结构.pdf

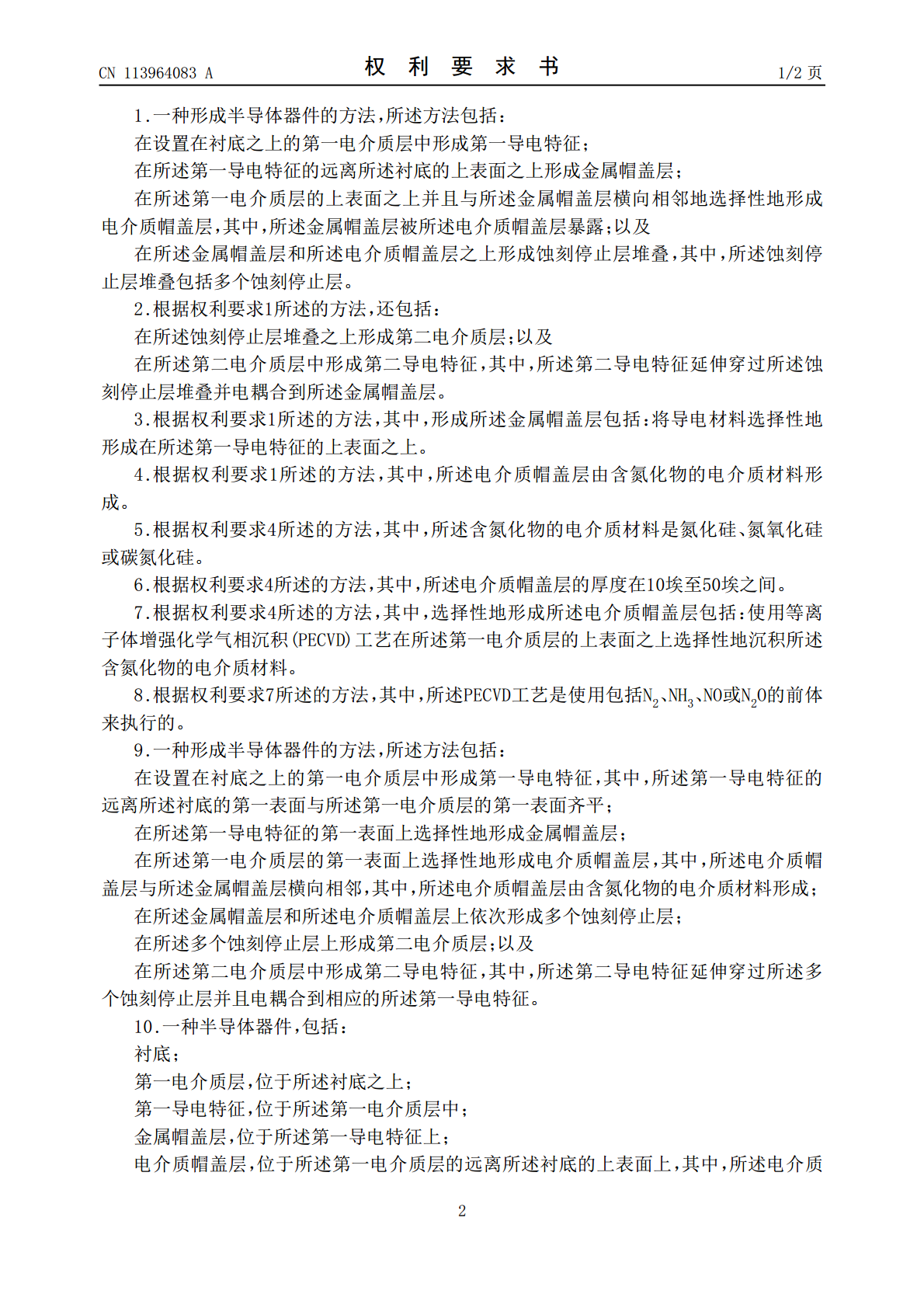

本公开涉及具有电介质帽盖层和蚀刻停止层堆叠的互连结构。一种形成半导体器件的方法包括:在设置在衬底之上的第一电介质层中形成第一导电特征;在第一导电特征的远离衬底的上表面之上形成金属帽盖层;在第一电介质层的上表面之上并且与金属帽盖层横向相邻地选择性地形成电介质帽盖层,其中,金属帽盖层被电介质帽盖层暴露;以及在金属帽盖层和电介质帽盖层之上形成蚀刻停止层堆叠,其中,蚀刻停止层堆叠包括多个蚀刻停止层。

用于蚀刻金属互连层的方法.pdf

本申请公开了用于蚀刻金属互连层的方法。在一些示例中,一种方法(100)包括:获得具有沉积在衬底(402)上方的金属互连层的衬底;在金属互连层(404)上形成第一介电层(406);在第一介电层上形成第二介电层(408);在第二介电层上形成电容器金属层;将电容器金属层和第二介电层图案化和蚀刻至第一介电层,以将电容器金属层和第二介电层的部分留在第一介电层上(410);形成抗反射涂层以覆盖电容器金属层和第二介电层的部分,并覆盖金属互连层(412);以及图案化金属互连层以形成第一金属层和第二金属层(414)。

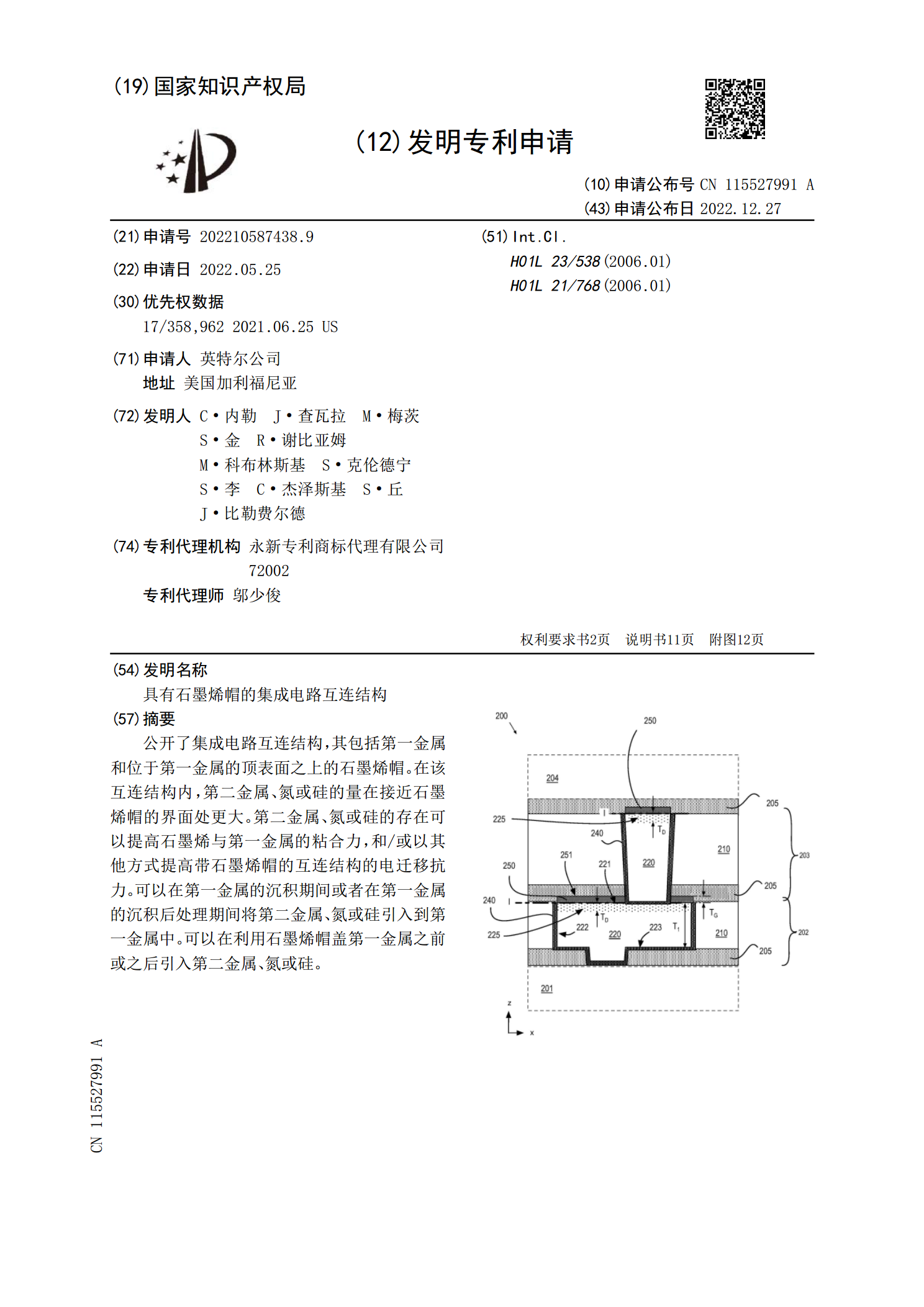

具有石墨烯帽的集成电路互连结构.pdf

公开了集成电路互连结构,其包括第一金属和位于第一金属的顶表面之上的石墨烯帽。在该互连结构内,第二金属、氮或硅的量在接近石墨烯帽的界面处更大。第二金属、氮或硅的存在可以提高石墨烯与第一金属的粘合力,和/或以其他方式提高带石墨烯帽的互连结构的电迁移抗力。可以在第一金属的沉积期间或者在第一金属的沉积后处理期间将第二金属、氮或硅引入到第一金属中。可以在利用石墨烯帽盖第一金属之前或之后引入第二金属、氮或硅。

具有垂直互连件的可堆叠全模制半导体结构.pdf

一种制造半导体器件的方法可以包括:提供载体并且在载体上形成具有通过第一光致抗蚀剂的第一开口的第一光致抗蚀剂。可以在第一光致抗蚀剂上形成不平坦的导电晶种层,并且所述导电晶种层通过第一光致抗蚀剂共形地延伸至第一开口中。可以在第一光致抗蚀剂上和不平坦的导电晶种层上形成第二光致抗蚀剂。可以对第二光致抗蚀剂层进行图案化,以形成通过第二光致抗蚀剂延伸至不平坦的导电晶种层的第二开口。可以在不平坦的导电晶种层上和第二开口内镀覆导电柱。可以去除第二光致抗蚀剂而将第一光致抗蚀剂留在原处。半导体晶粒可以接合至载体。可以利用模制

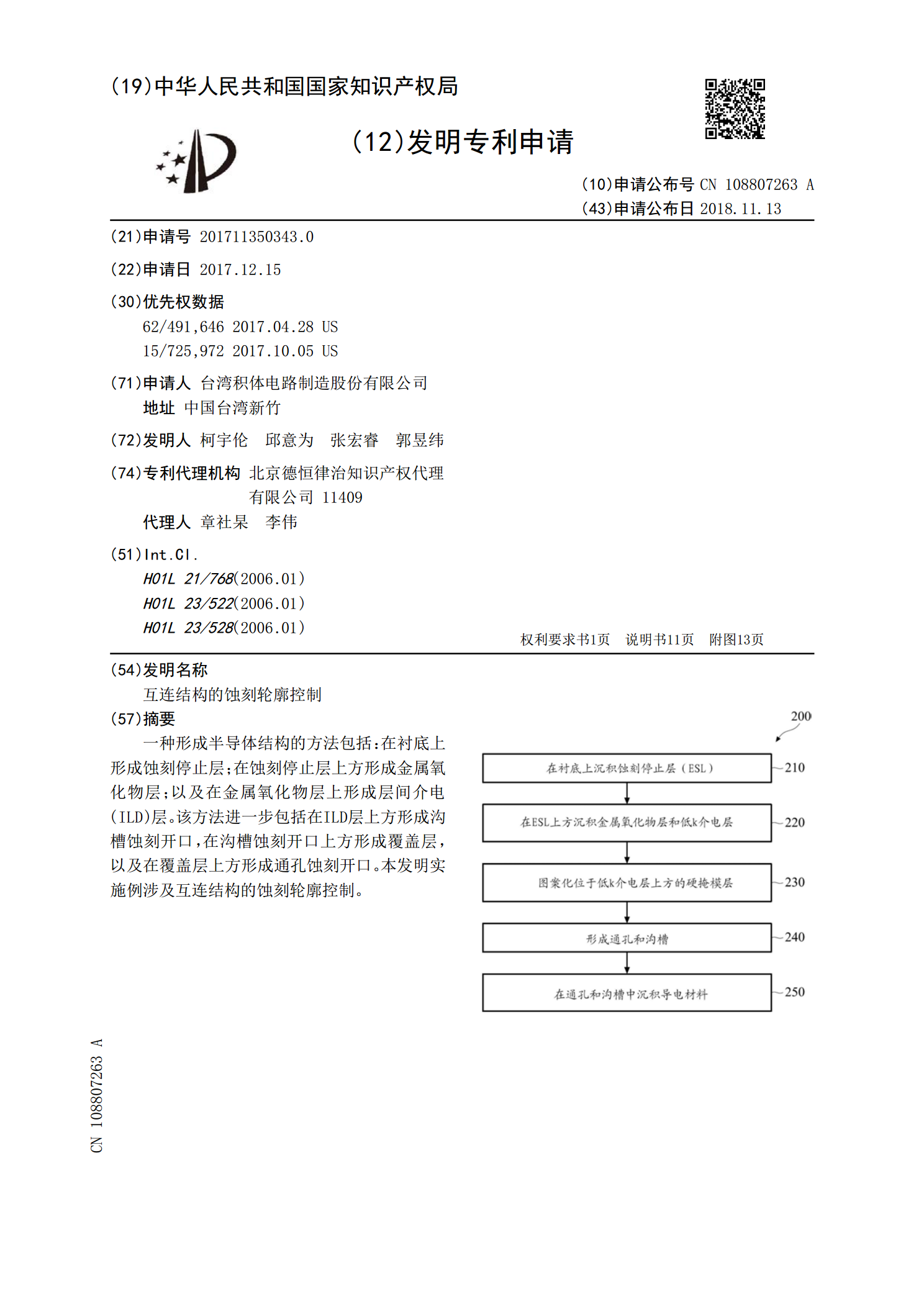

互连结构的蚀刻轮廓控制.pdf

一种形成半导体结构的方法包括:在衬底上形成蚀刻停止层;在蚀刻停止层上方形成金属氧化物层;以及在金属氧化物层上形成层间介电(ILD)层。该方法进一步包括在ILD层上方形成沟槽蚀刻开口,在沟槽蚀刻开口上方形成覆盖层,以及在覆盖层上方形成通孔蚀刻开口。本发明实施例涉及互连结构的蚀刻轮廓控制。