基于硅钝化的p-GaN栅增强型MIS-HEMT器件及其制备方法.pdf

努力****爱敏

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于硅钝化的p-GaN栅增强型MIS-HEMT器件及其制备方法.pdf

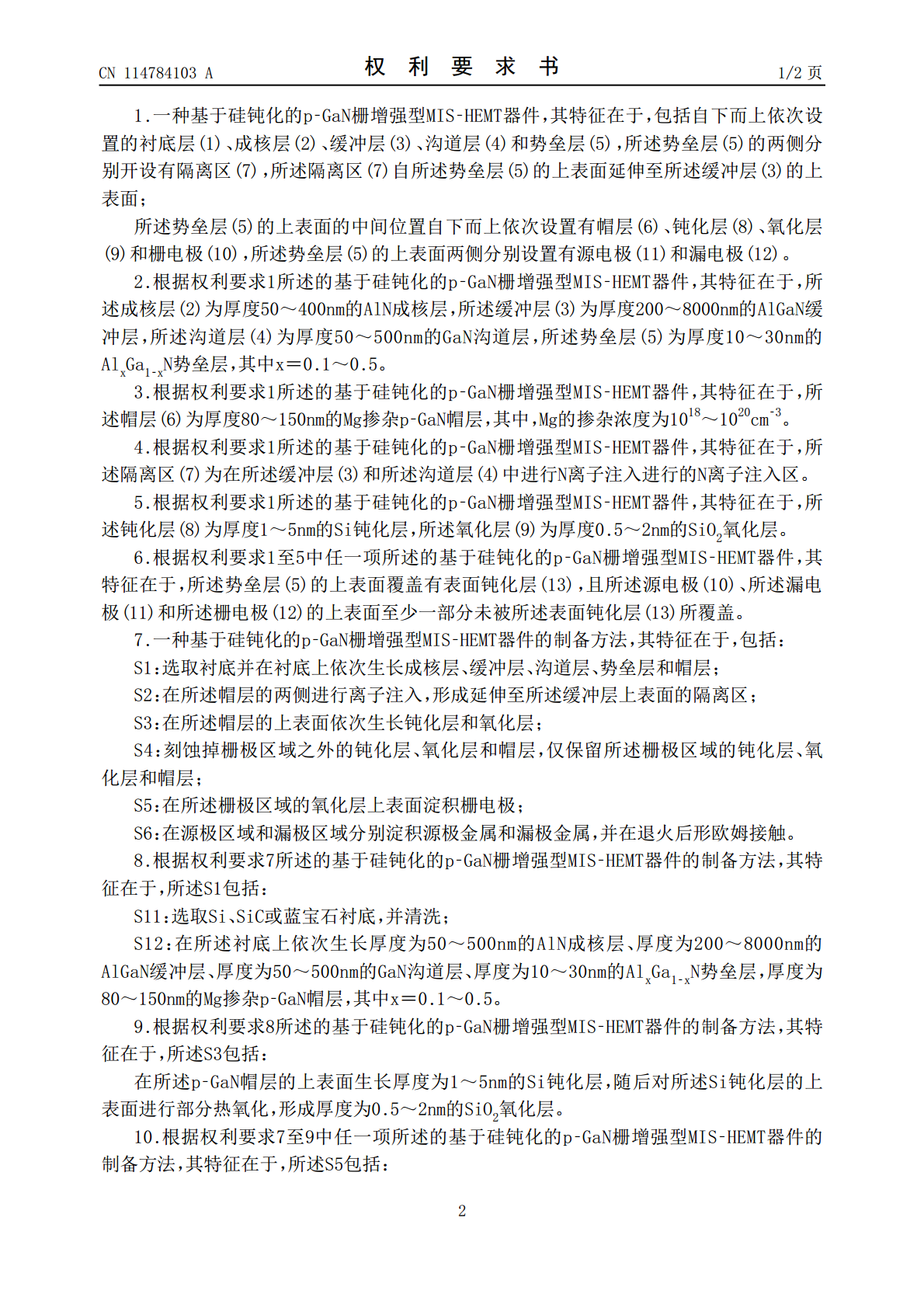

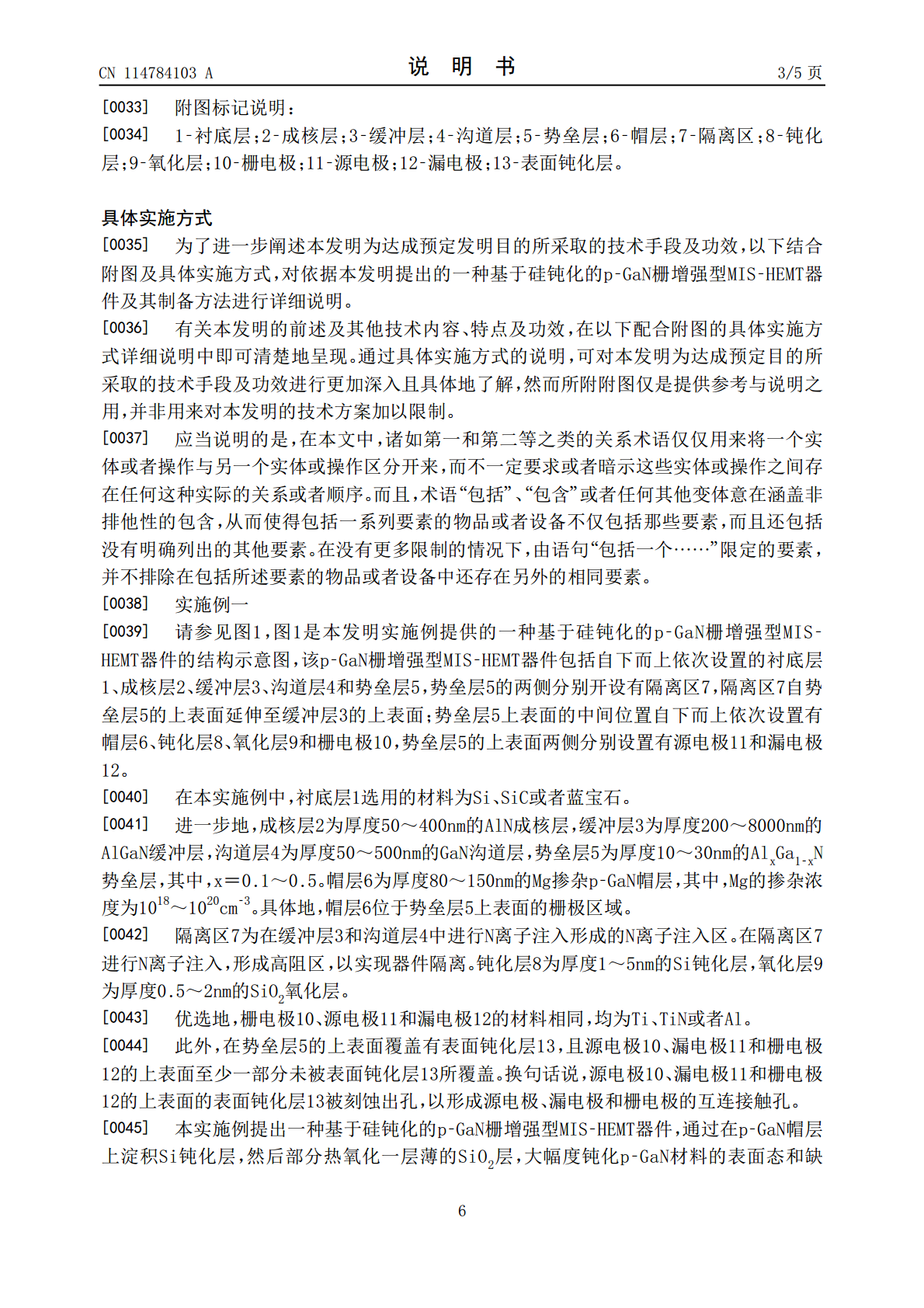

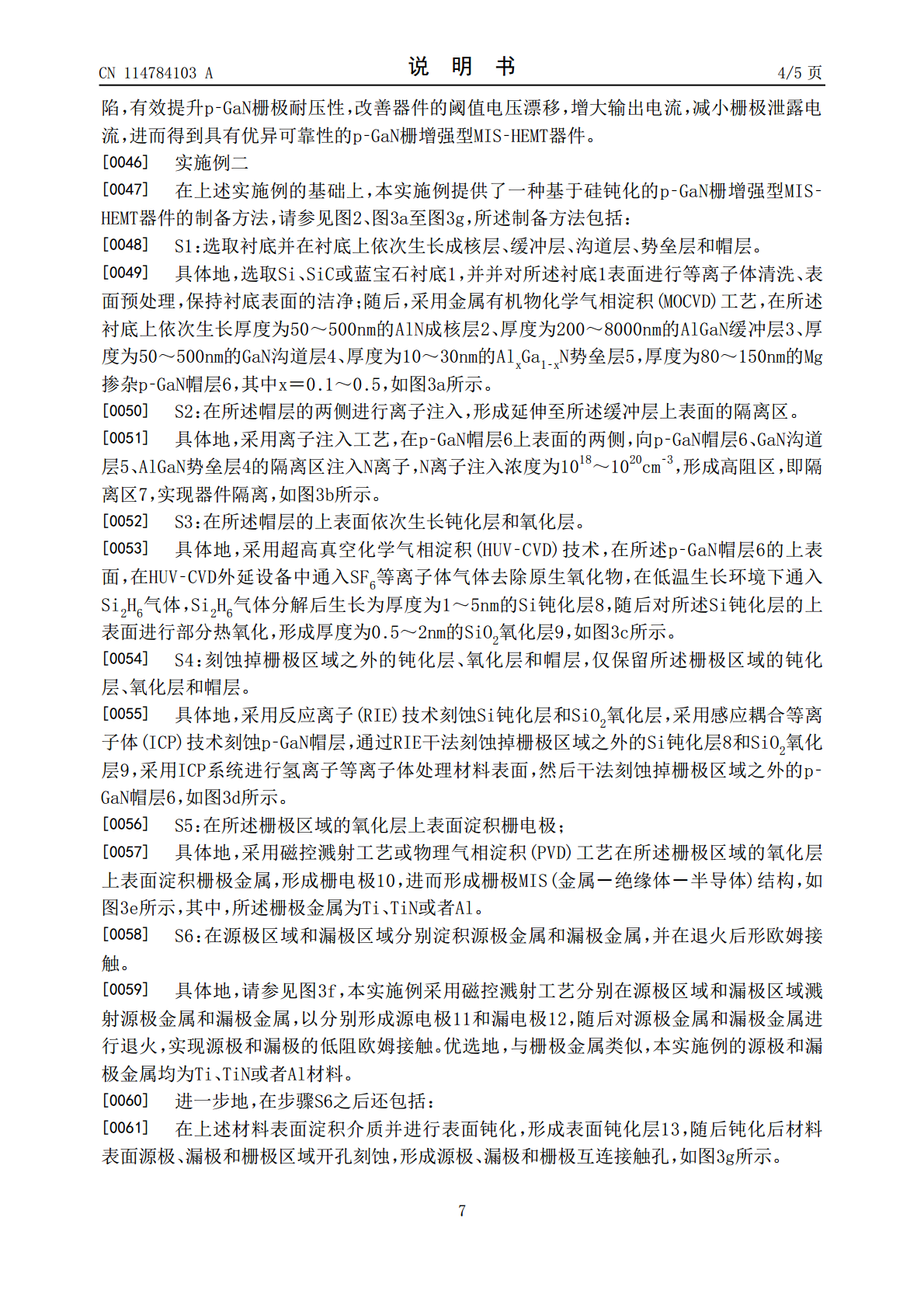

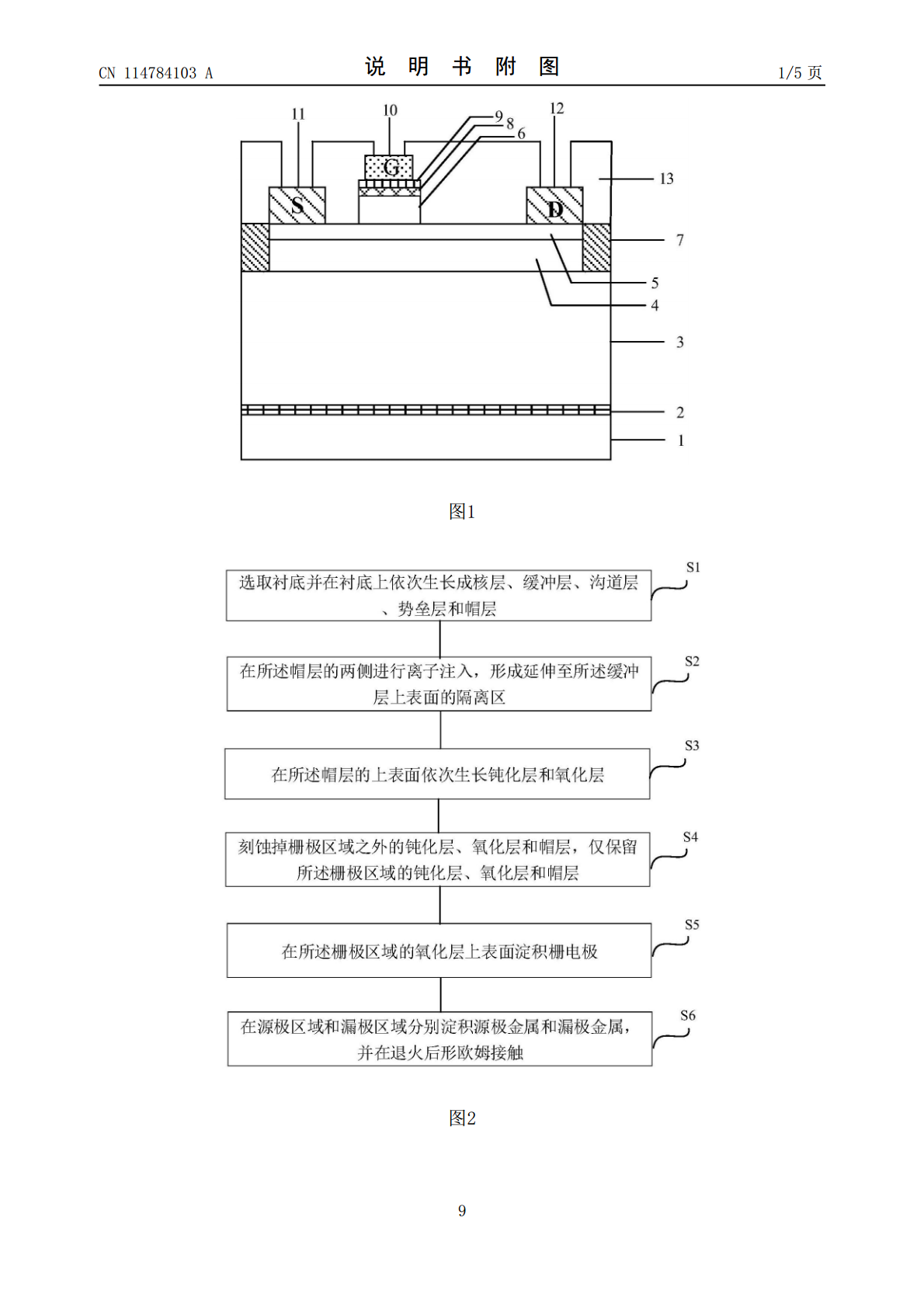

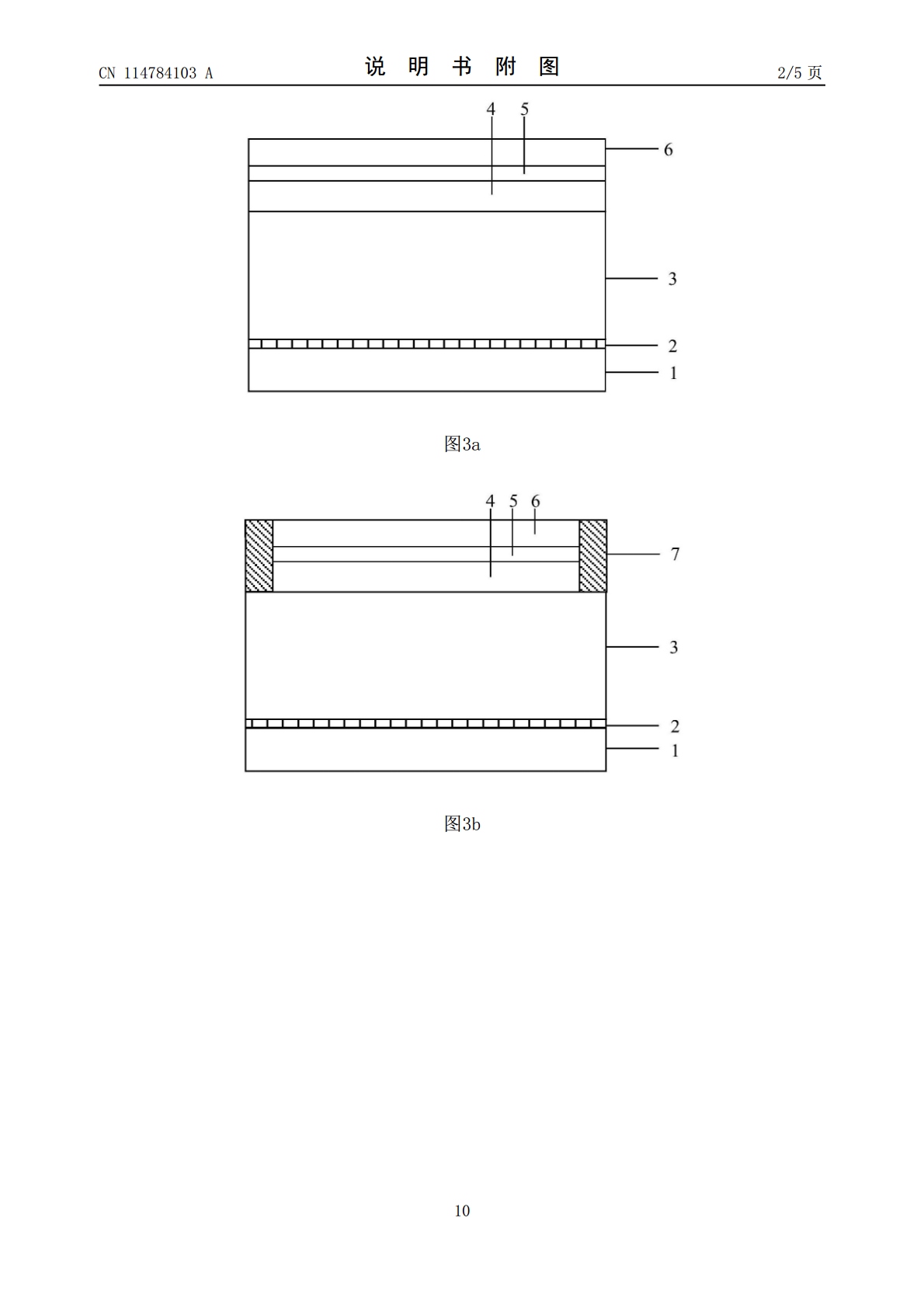

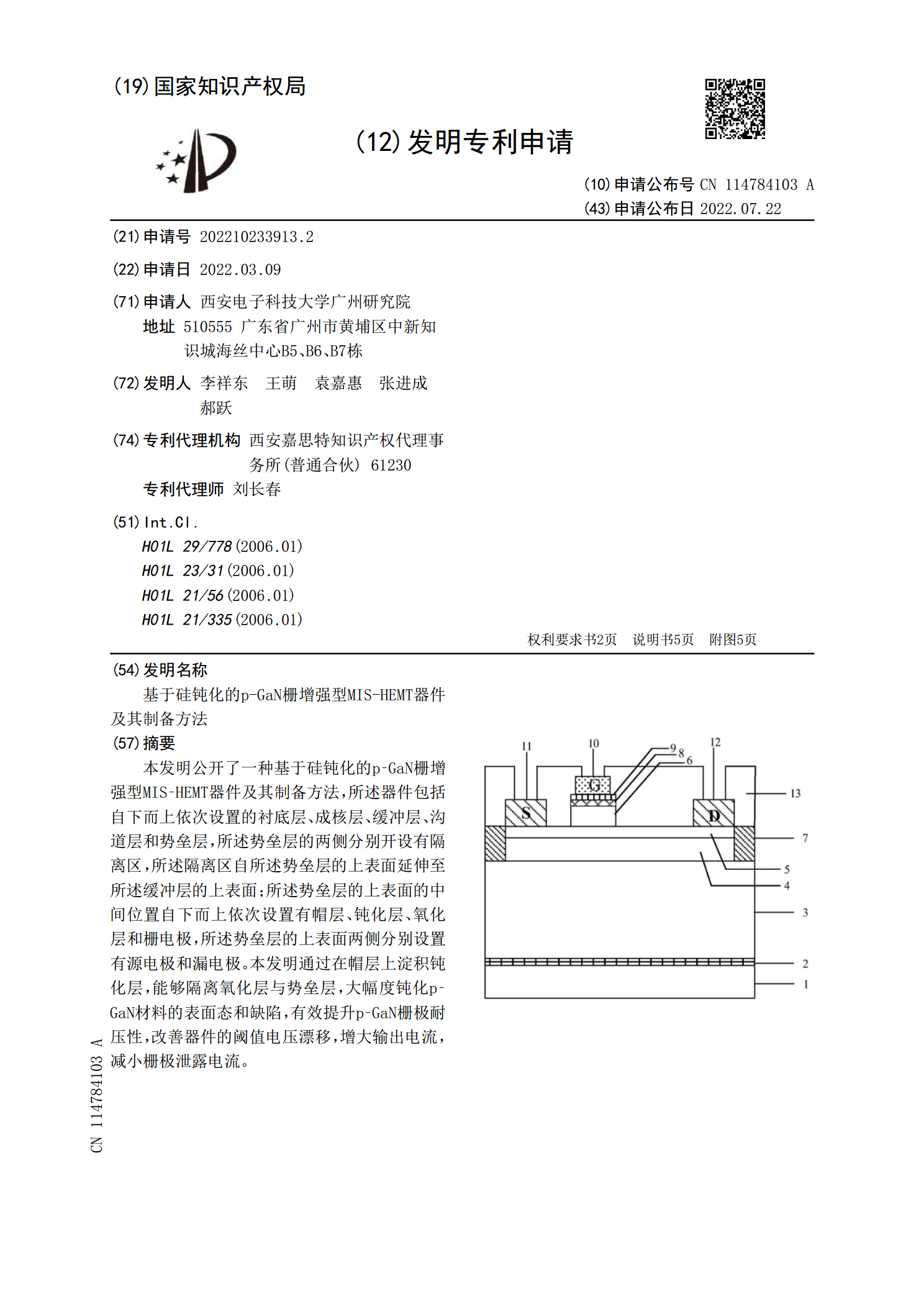

本发明公开了一种基于硅钝化的p‑GaN栅增强型MIS‑HEMT器件及其制备方法,所述器件包括自下而上依次设置的衬底层、成核层、缓冲层、沟道层和势垒层,所述势垒层的两侧分别开设有隔离区,所述隔离区自所述势垒层的上表面延伸至所述缓冲层的上表面;所述势垒层的上表面的中间位置自下而上依次设置有帽层、钝化层、氧化层和栅电极,所述势垒层的上表面两侧分别设置有源电极和漏电极。本发明通过在帽层上淀积钝化层,能够隔离氧化层与势垒层,大幅度钝化p‑GaN材料的表面态和缺陷,有效提升p‑GaN栅极耐压性,改善器件的阈值电压漂移

一种具有高介电常数栅介质叠层的槽栅增强型MISHEMT器件及其制备方法.pdf

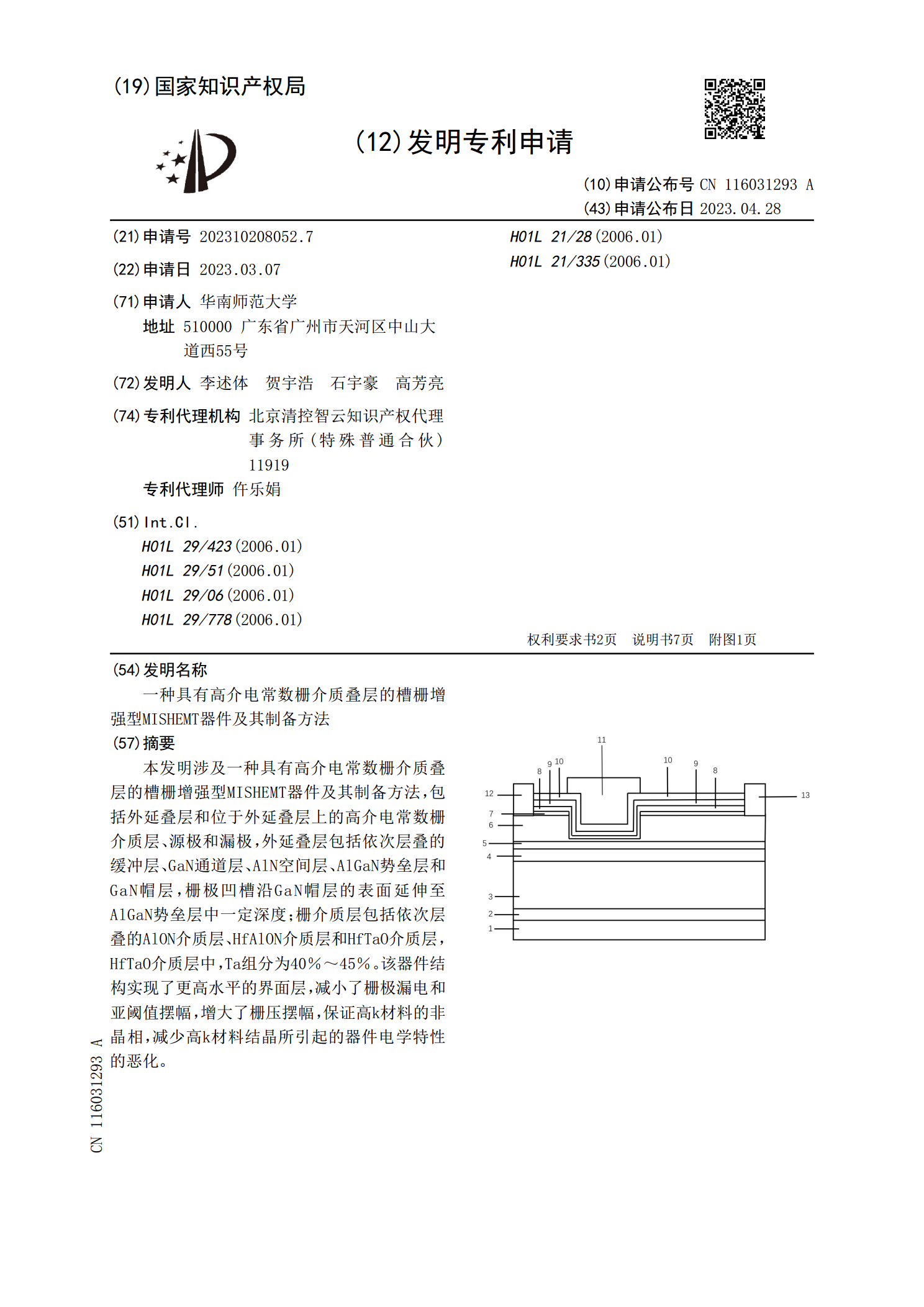

(19)国家知识产权局(12)发明专利申请(10)申请公布号CN116031293A(43)申请公布日2023.04.28(21)申请号202310208052.7H01L21/28(2006.01)(22)申请日2023.03.07H01L21/335(2006.01)(71)申请人华南师范大学地址510000广东省广州市天河区中山大道西55号(72)发明人李述体贺宇浩石宇豪高芳亮(74)专利代理机构北京清控智云知识产权代理事务所(特殊普通合伙)11919专利代理师仵乐娟(51)Int.Cl.H01L2

P型栅增强型HEMT器件及其制备方法.pdf

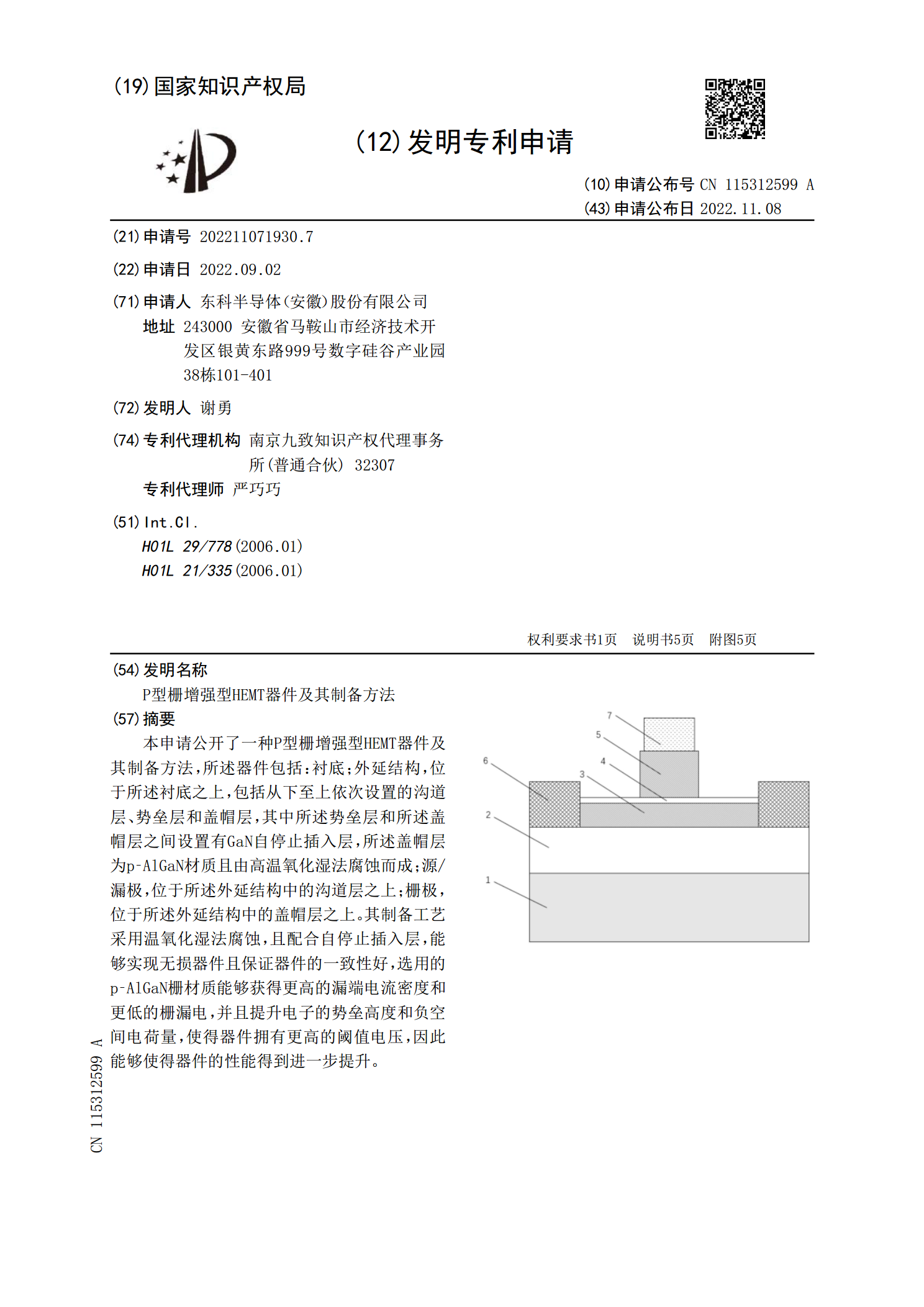

本申请公开了一种P型栅增强型HEMT器件及其制备方法,所述器件包括:衬底;外延结构,位于所述衬底之上,包括从下至上依次设置的沟道层、势垒层和盖帽层,其中所述势垒层和所述盖帽层之间设置有GaN自停止插入层,所述盖帽层为p‑AlGaN材质且由高温氧化湿法腐蚀而成;源/漏极,位于所述外延结构中的沟道层之上;栅极,位于所述外延结构中的盖帽层之上。其制备工艺采用温氧化湿法腐蚀,且配合自停止插入层,能够实现无损器件且保证器件的一致性好,选用的p‑AlGaN栅材质能够获得更高的漏端电流密度和更低的栅漏电,并且提升电子的

沟槽栅功率器件及其制备方法.pdf

本申请实施例公开了一种沟槽栅功率器件的制备方法及沟槽栅功率器件,其中所述制备方法包括:提供一衬底,刻蚀衬底以在衬底中形成沟槽;在沟槽的内表面上形成一场氧化层,并进一步在沟槽中形成屏蔽栅以及用于形成沟槽栅的栅极凹槽;在屏蔽栅上形成隔离介质层,并对隔离介质层回刻蚀,以保留屏蔽栅上的隔离介质层;在栅极凹槽中填充多晶硅并回刻蚀,以形成沟槽栅;去除沟槽栅所暴露出的隔离介质层;生长一层栅氧化层,在栅极凹槽的衬底侧壁形成栅氧化层,同时在暴露的屏蔽栅上形成栅间介质层。这样能解决现有技术中存在的屏蔽栅残留FOX表面的风险及

增强型MOSFET器件及其制备方法.pdf

本申请公开了一种增强型MOSFET器件,包括:衬底;N型GaN缓冲层,位于衬底的上方;U型GaN层,位于N型GaN缓冲层的上方;P型GaN层,位于U型GaN层的上方;N型Poly‑Si层,位于P型GaN层的上方;栅介质层,位于N型Poly‑Si层的上方;栅极,位于栅介质层的上方;源极,位于N型Poly‑Si层的上方;漏极,位于U型GaN层的上方,漏极和源极分别位于栅极两侧。本申请将N型Poly‑Si层直接形成在载流子浓度较低的U型GaN层上,再将漏极形成在N型Poly‑Si层上,采用此结构相当于形成漏极的