一种具有高介电常数栅介质叠层的槽栅增强型MISHEMT器件及其制备方法.pdf

Do****76

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种具有高介电常数栅介质叠层的槽栅增强型MISHEMT器件及其制备方法.pdf

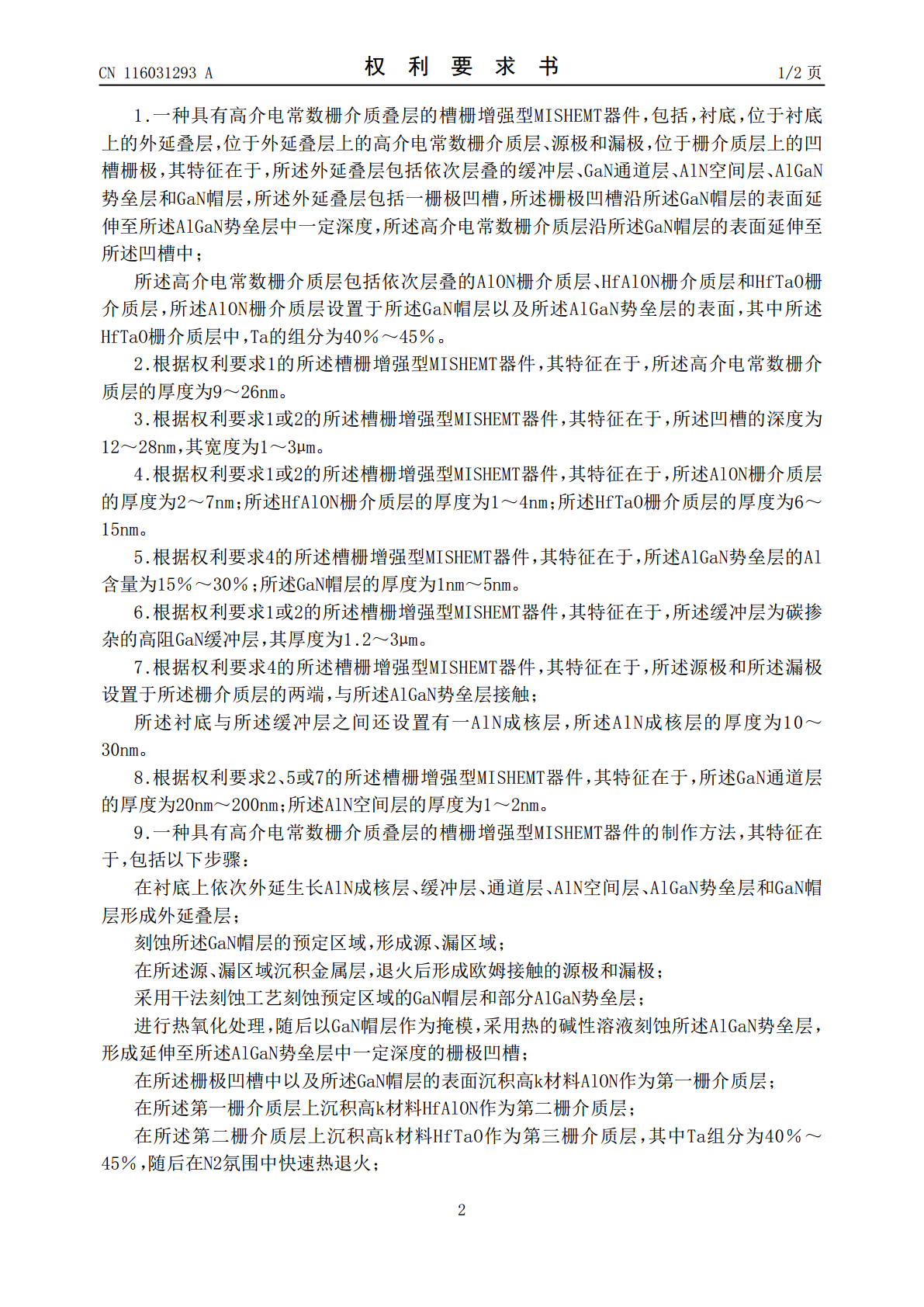

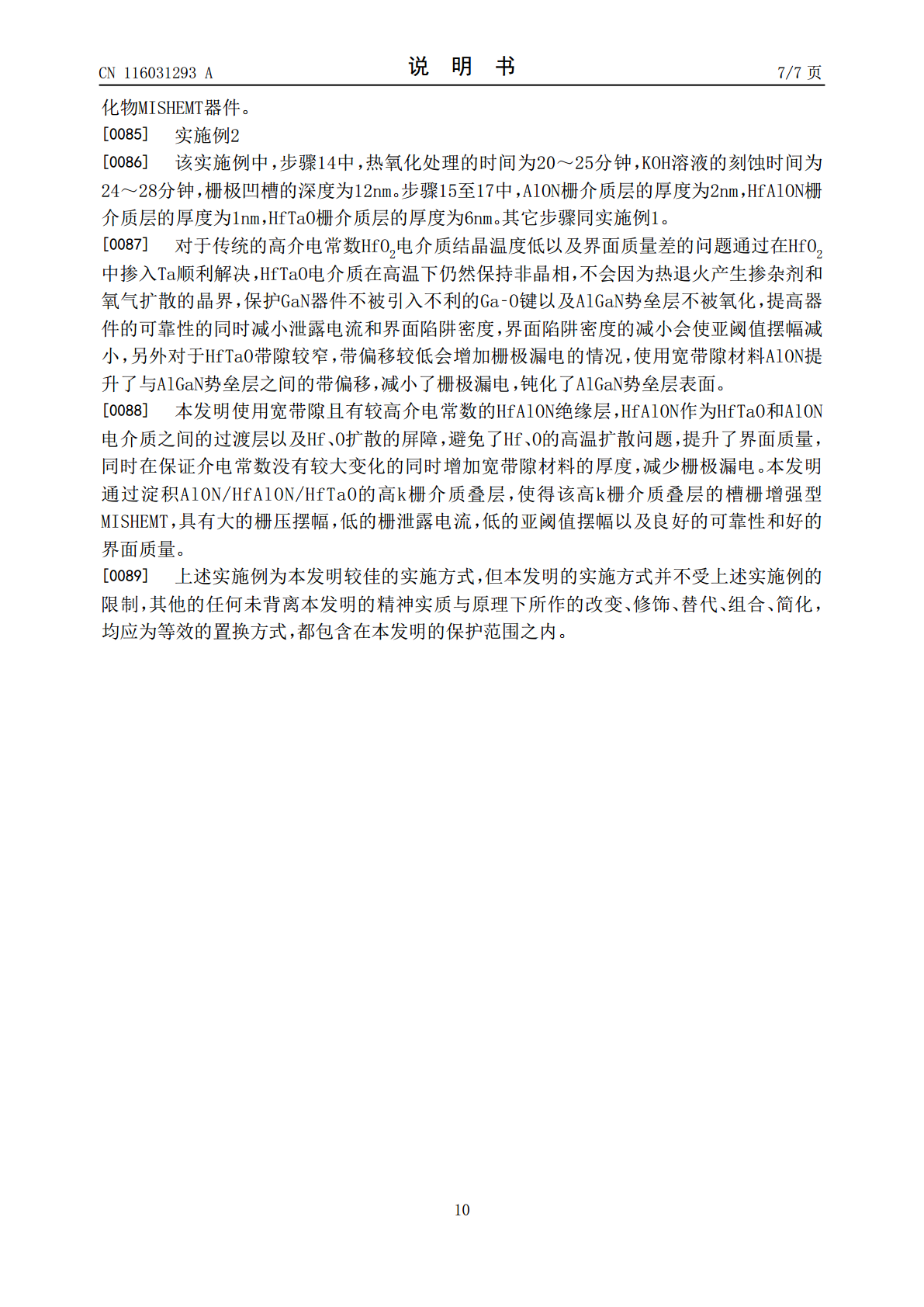

(19)国家知识产权局(12)发明专利申请(10)申请公布号CN116031293A(43)申请公布日2023.04.28(21)申请号202310208052.7H01L21/28(2006.01)(22)申请日2023.03.07H01L21/335(2006.01)(71)申请人华南师范大学地址510000广东省广州市天河区中山大道西55号(72)发明人李述体贺宇浩石宇豪高芳亮(74)专利代理机构北京清控智云知识产权代理事务所(特殊普通合伙)11919专利代理师仵乐娟(51)Int.Cl.H01L2

HfGdON高介电常数栅介质薄膜的制备及其器件性能优化.docx

HfGdON高介电常数栅介质薄膜的制备及其器件性能优化标题:HfGdON高介电常数栅介质薄膜的制备及其器件性能优化摘要:本论文研究了一种新型高介电常数栅介质薄膜材料HfGdON的制备方法,并探讨了其对器件性能的影响以及相关优化策略。通过采用漏气磁控溅射技术制备了高质量的HfGdON薄膜,并对其进行了结构、组成与电学性能的表征。研究结果表明,HfGdON薄膜具有较高的介电常数和较低的漏电流密度,能够作为高效栅介质材料应用于电子器件中。进一步通过优化制备工艺,优化了HfGdON薄膜的介电性能,提高了器件的性能

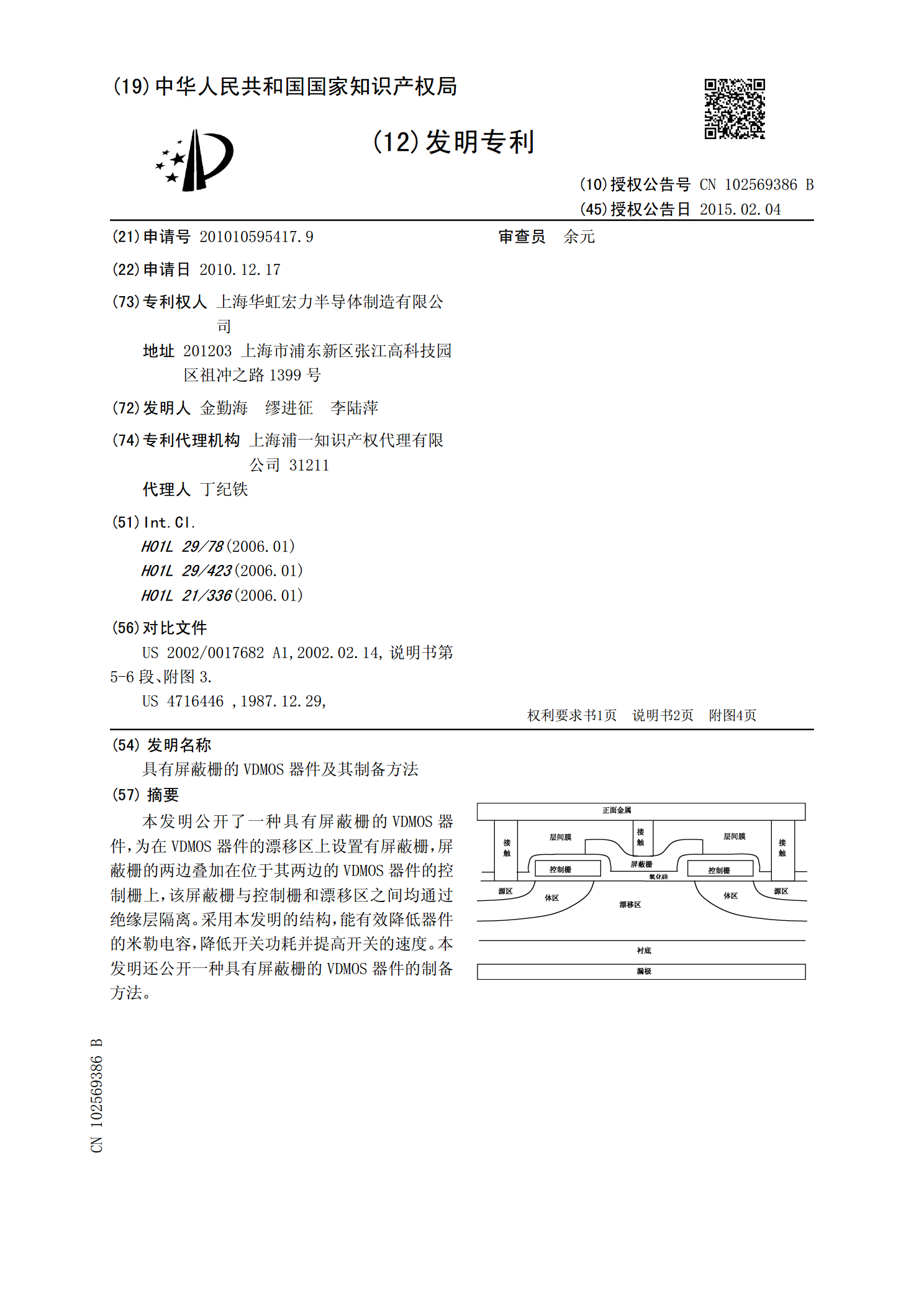

具有屏蔽栅的VDMOS器件及其制备方法.pdf

本发明公开了一种具有屏蔽栅的VDMOS器件,为在VDMOS器件的漂移区上设置有屏蔽栅,屏蔽栅的两边叠加在位于其两边的VDMOS器件的控制栅上,该屏蔽栅与控制栅和漂移区之间均通过绝缘层隔离。采用本发明的结构,能有效降低器件的米勒电容,降低开关功耗并提高开关的速度。本发明还公开一种具有屏蔽栅的VDMOS器件的制备方法。

铪基高介电常数栅介质薄膜的制备及其物性研究.docx

铪基高介电常数栅介质薄膜的制备及其物性研究引言近年来,随着电子行业的不断发展,高介电常数栅介质薄膜作为重要的电子材料在电容器、传感器以及微波器件等领域广泛应用。而铪基高介电常数栅介质薄膜因具有高密度和高介电常数等特性,被认为是未来电子材料的首选之一。本文主要探讨铪基高介电常数栅介质薄膜的制备及其物性研究,为材料科学领域的研究提供参考。1.铪基高介电常数栅介质薄膜制备方法铪基高介电常数栅介质薄膜的制备方法较多,本文重点介绍两种常用方法。1.1.离子束沉积法离子束沉积法是一种将离子束注入到基底材料中的技术方法

一种槽栅功率半导体器件及其制备方法.pdf

本发明涉及一种槽栅功率半导体器件,包括元胞区、栅极引出部分和终端区,所述元胞区和所述栅极引出部分具有多个间隔设置的沟槽,所述沟槽包括连续设置的沟槽前端和沟槽末端,所述沟槽末端的形状为水滴状,并且每个所述沟槽末端的宽度比沟槽前端的宽度宽。所述沟槽分为栅电极部分和栅极引出部分,所述栅极引出部分将栅极和外部相连,沟槽末端的形状为水滴状,并且沟槽末端的宽度比沟槽前端的宽度宽,增大了曲率半径,从而避免了更薄的绝缘层产生,抑制了泄漏电流的发生。