半导体器件及其制备方法.pdf

慧颖****23

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体器件及其制备方法.pdf

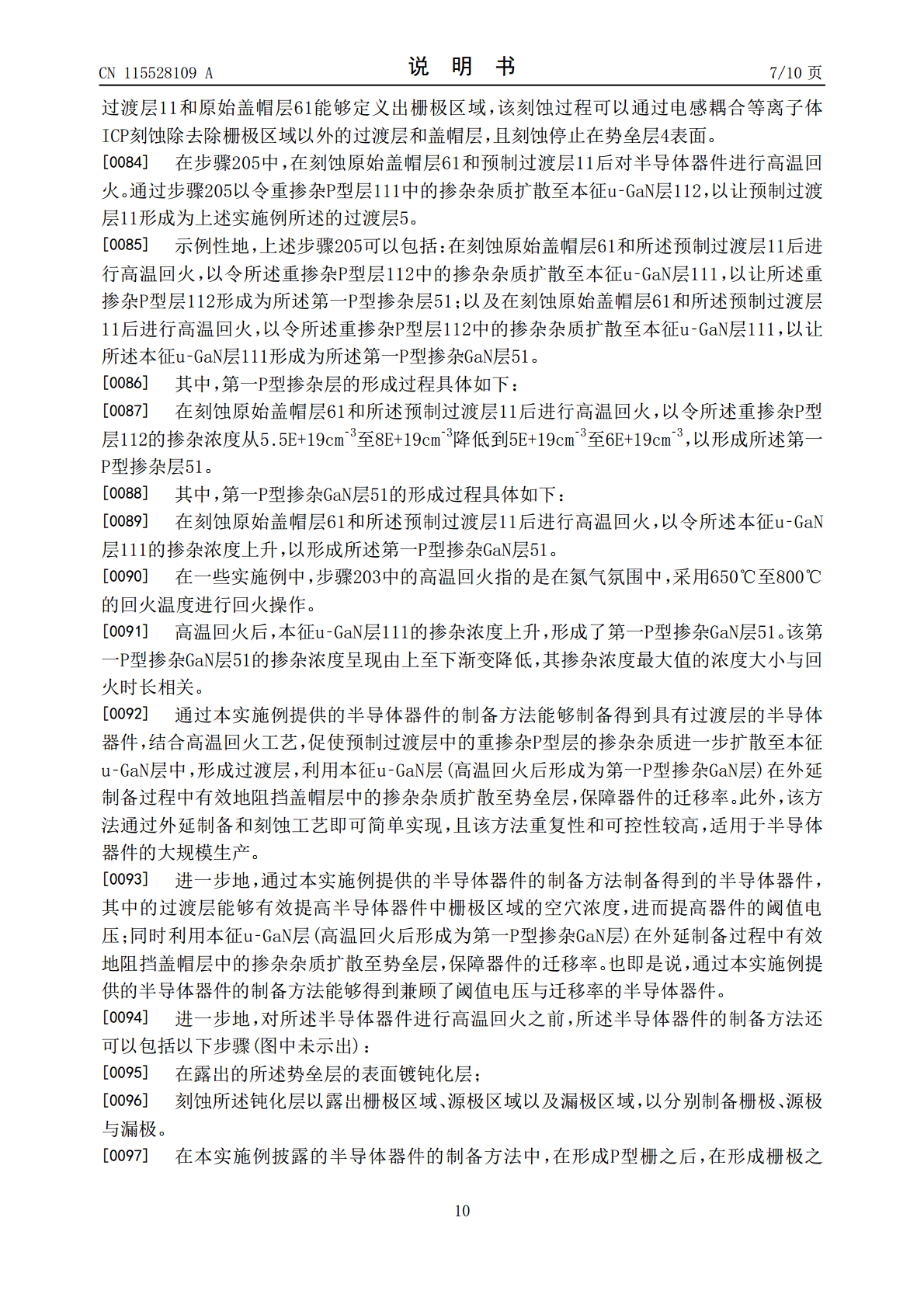

本发明提供一种半导体器件及其制备方法,半导体器件,包括:衬底;衬底上相对设置的源极和漏极;纳米堆叠结构,源极和漏极分别位于纳米堆叠结构的相对的两侧;纳米堆叠结构包括多个导电纳米片,多个导电纳米片与衬底的表面平行,多个导电纳米片沿垂直于衬底的方向间隔堆叠,导电纳米片两端分别嵌入源极和漏极;以及环绕式栅极;其中,导电纳米片平行于衬底的表面开设有容纳槽;容纳槽内填充有外延层,外延层的载流子迁移率高于导电纳米片的载流子迁移率,外延层与相应的导电纳米片形成复合式纳米片;环绕式栅极环绕于多个复合式纳米片的周侧。本发明

半导体器件及其制备方法.pdf

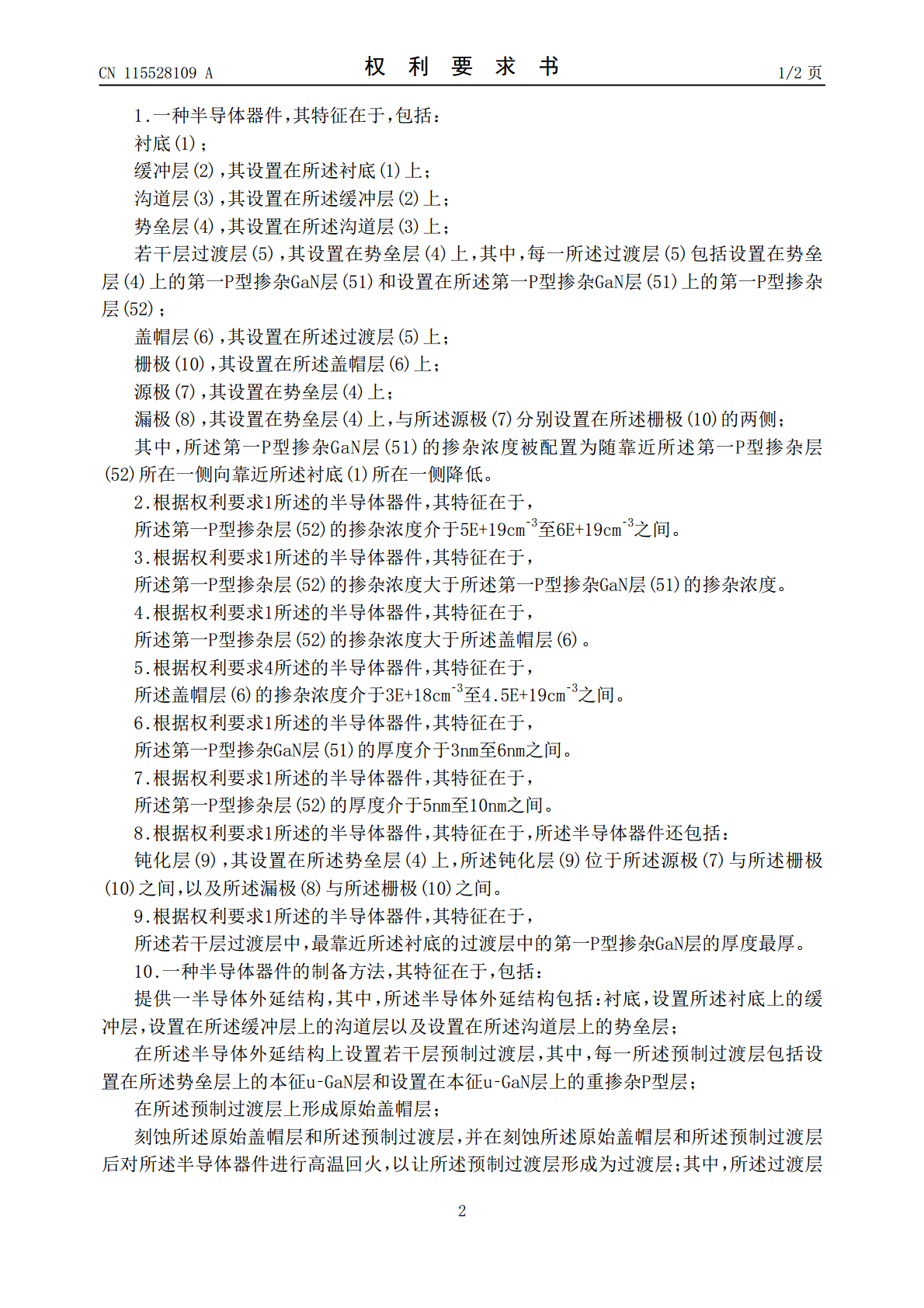

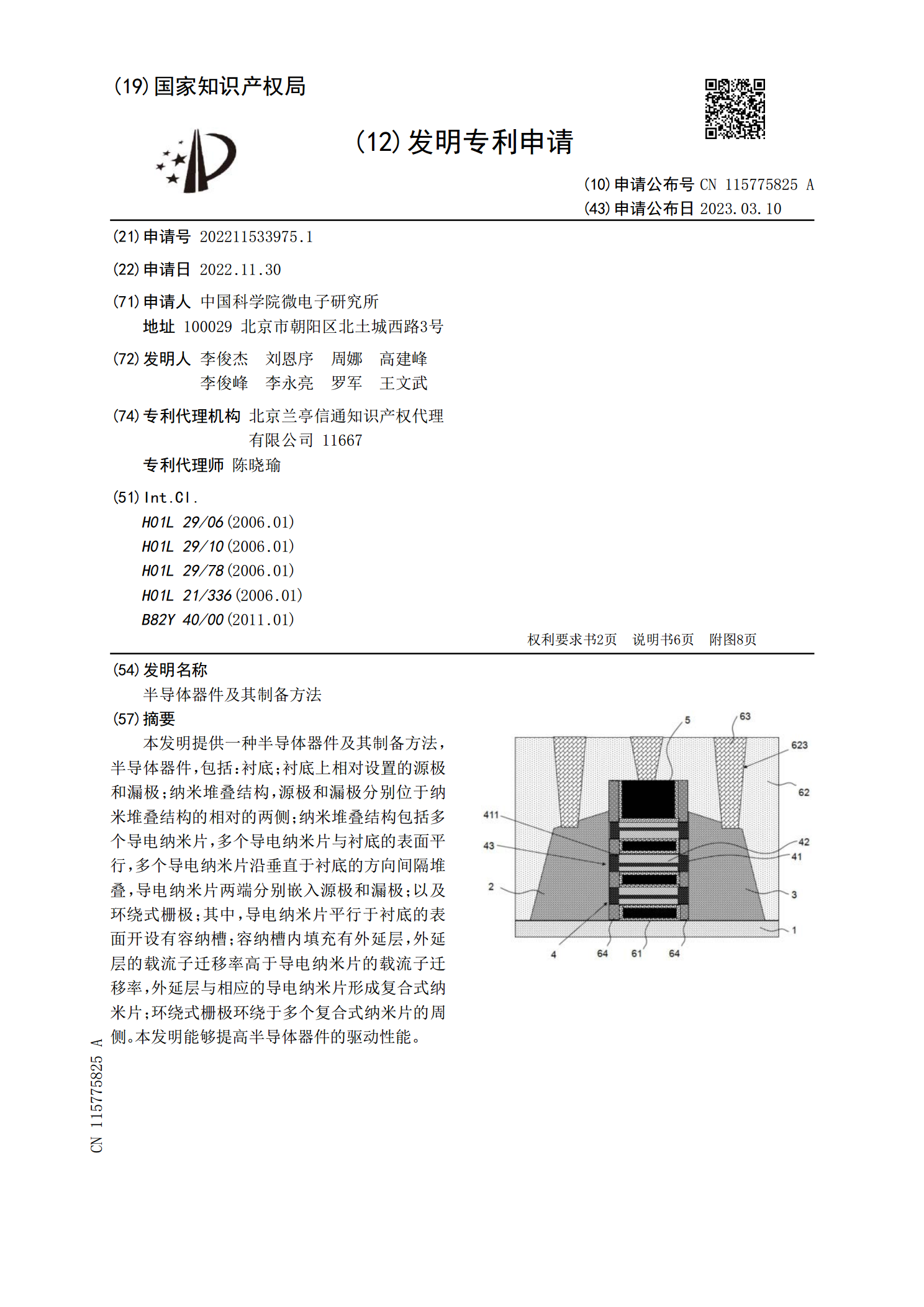

本披露公开了一种半导体器件及其制备方法。该半导体器件包括:依次叠置的衬底、缓冲层、沟道层和势垒层;若干层过渡层,其设置在势垒层上,其中,每一过渡层包括设置在势垒层上的第一P型掺杂GaN层和设置在第一P型掺杂GaN层上的第一P型掺杂层;盖帽层,其设置在过渡层上;栅极,其设置在盖帽层上;源极,其设置在势垒层上;漏极,其设置在势垒层上,与源极分别设置在栅极的两侧;其中,第一P型掺杂GaN层的掺杂浓度被配置为随靠近第一P型掺杂层所在一侧向靠近衬底所在一侧降低。本披露公开的技术方案能够改善了非栅区域迁移率下降的问题

半导体器件及其制备方法.pdf

该发明公开了一种半导体器件及其制备方法,所述半导体器件的制备方法包括:提供半导体衬底,所述半导体衬底内形成有有源区和位于所述有源区之间的沟槽隔离结构;于所述有源区内形成第一凹槽;于所述第一凹槽内填充形成与所述有源区互为反型掺杂的反型多晶硅层;形成第二凹槽,所述第二凹槽贯穿所述多晶硅层和部分所述半导体衬底,保留位于所述第二凹槽侧面的部分所述反型多晶硅层;于所述第二凹槽内形成埋入式字线结构。根据本发明实施例的半导体器件制备方法,能够降低半导体器件的GIDL电流,提高半导体器件的性能和可靠性。

半导体器件及其制备方法.pdf

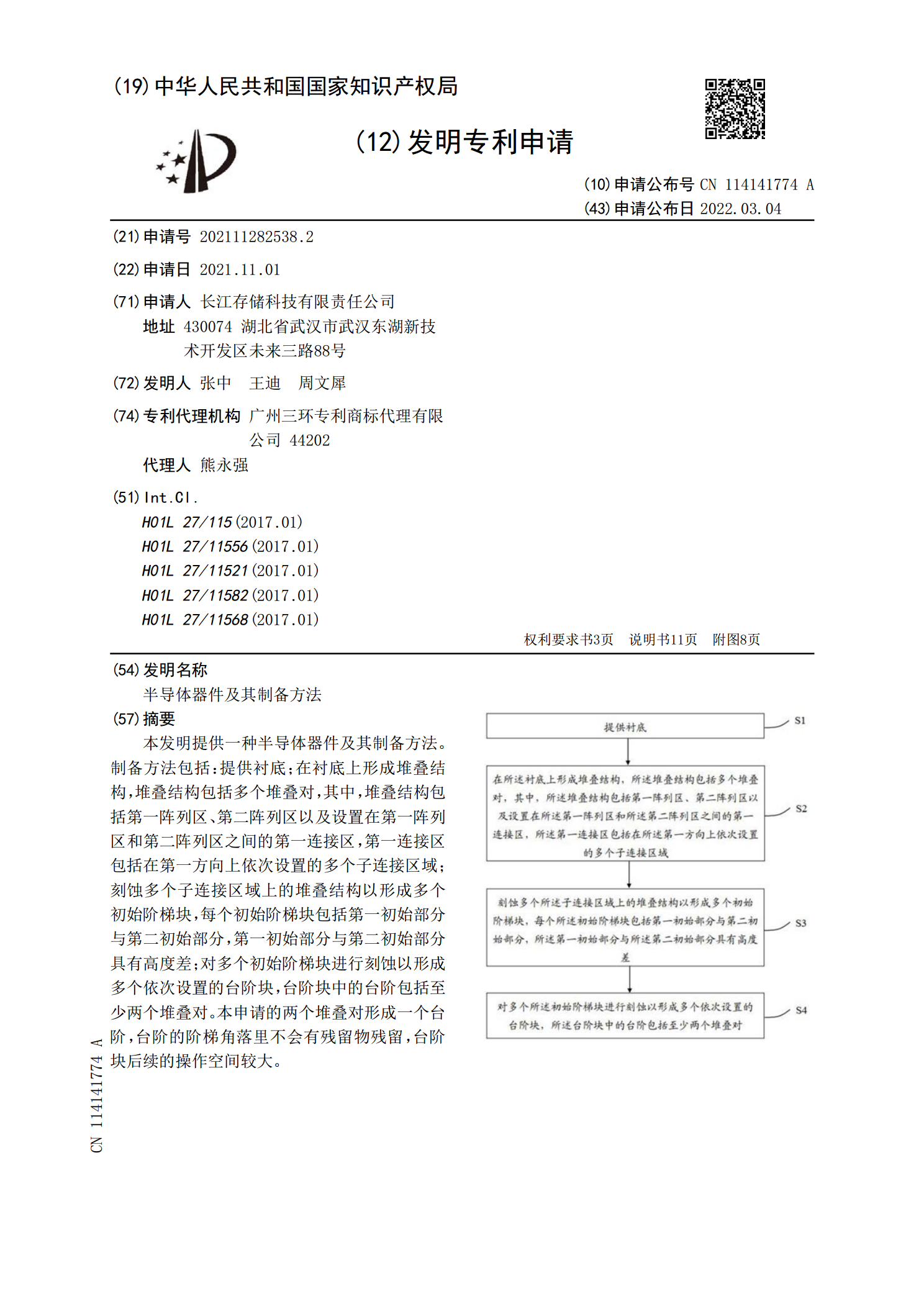

本发明提供一种半导体器件及其制备方法。制备方法包括:提供衬底;在衬底上形成堆叠结构,堆叠结构包括多个堆叠对,其中,堆叠结构包括第一阵列区、第二阵列区以及设置在第一阵列区和第二阵列区之间的第一连接区,第一连接区包括在第一方向上依次设置的多个子连接区域;刻蚀多个子连接区域上的堆叠结构以形成多个初始阶梯块,每个初始阶梯块包括第一初始部分与第二初始部分,第一初始部分与第二初始部分具有高度差;对多个初始阶梯块进行刻蚀以形成多个依次设置的台阶块,台阶块中的台阶包括至少两个堆叠对。本申请的两个堆叠对形成一个台阶,台阶的

半导体器件及其制备方法.pdf

该发明公开了一种半导体器件及其制备方法,所述制备方法包括提供半导体衬底,所述半导体衬底包括阵列区和外围区,所述阵列区形成有字线结构和浅沟槽隔离结构,所述字线结构上方形成有凹槽,所述外围区形成有浅沟槽隔离结构;于所述半导体衬底的表面沉积至少两层绝缘层,且每层所述绝缘层在同一刻蚀条件下刻蚀速率不同;依次去除位于所述阵列区和外围区表面的部分绝缘层,其中邻近所述绝缘层中位于下方的绝缘层成为上方绝缘层的刻蚀停止层,保留位于所述字线上方的凹槽内的所述所有绝缘层。根据本发明实施例的半导体器件的制备方法,能够减小对浅沟槽