形成通孔的方法.pdf

靖烟****魔王

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

形成通孔的方法.pdf

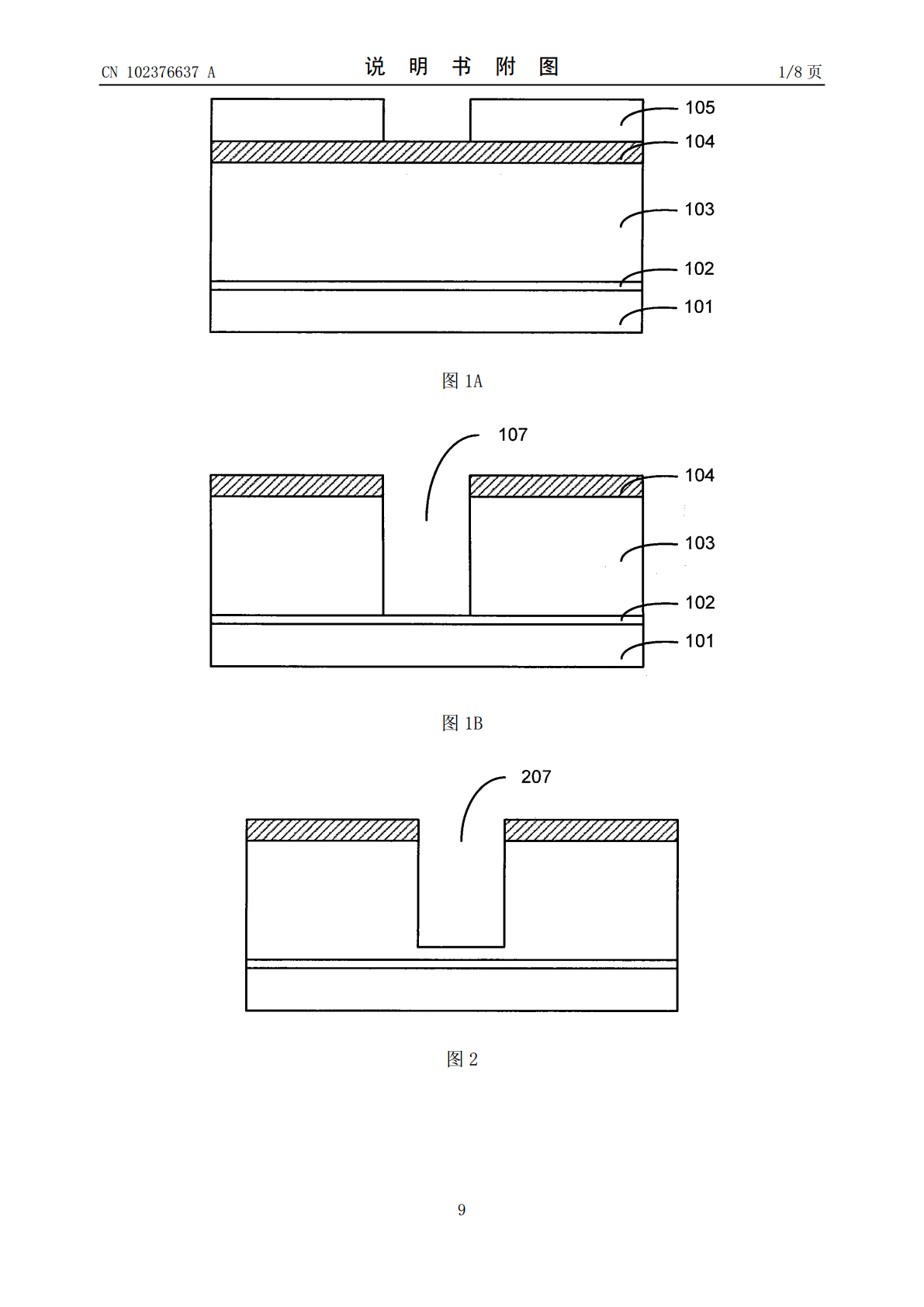

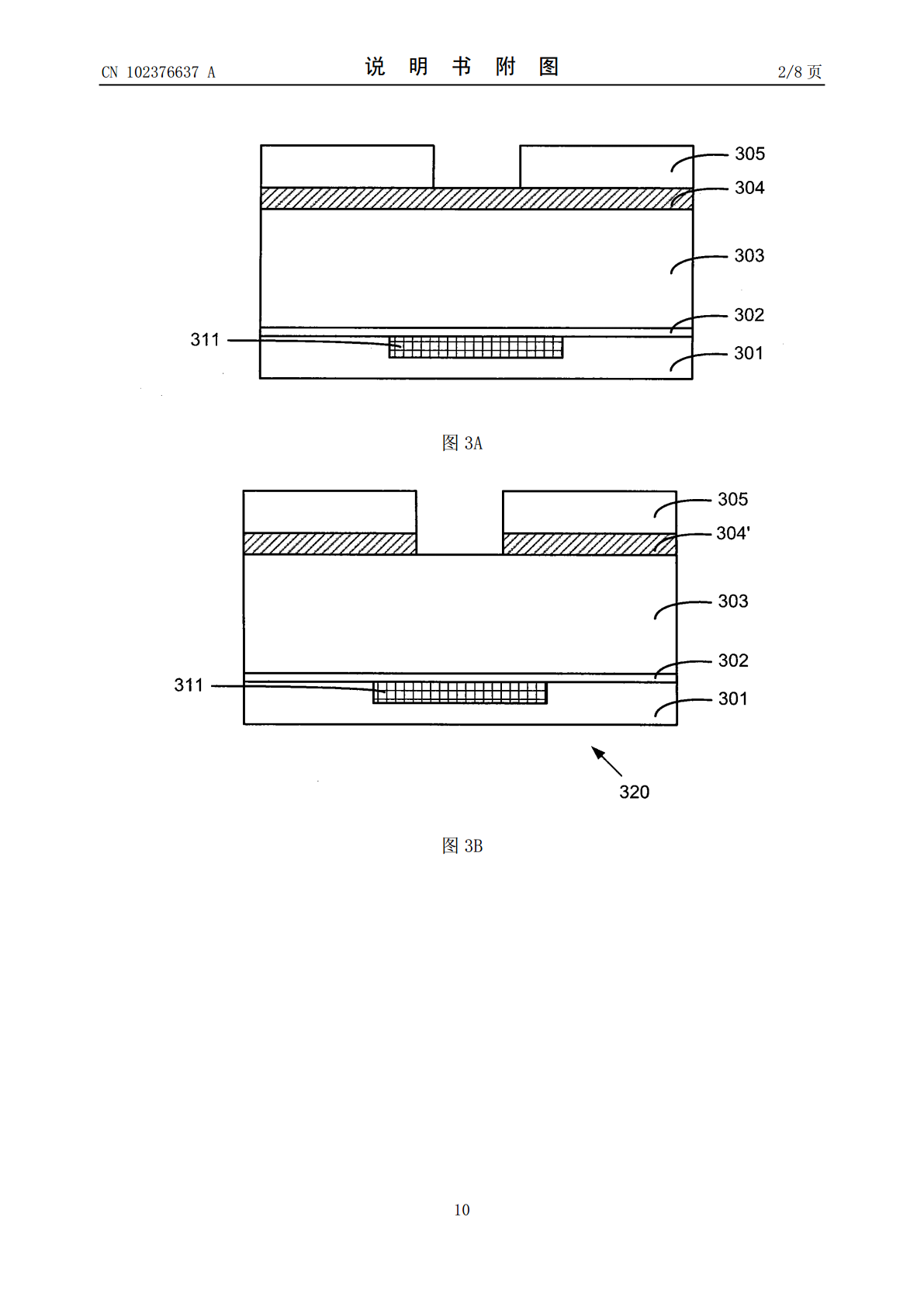

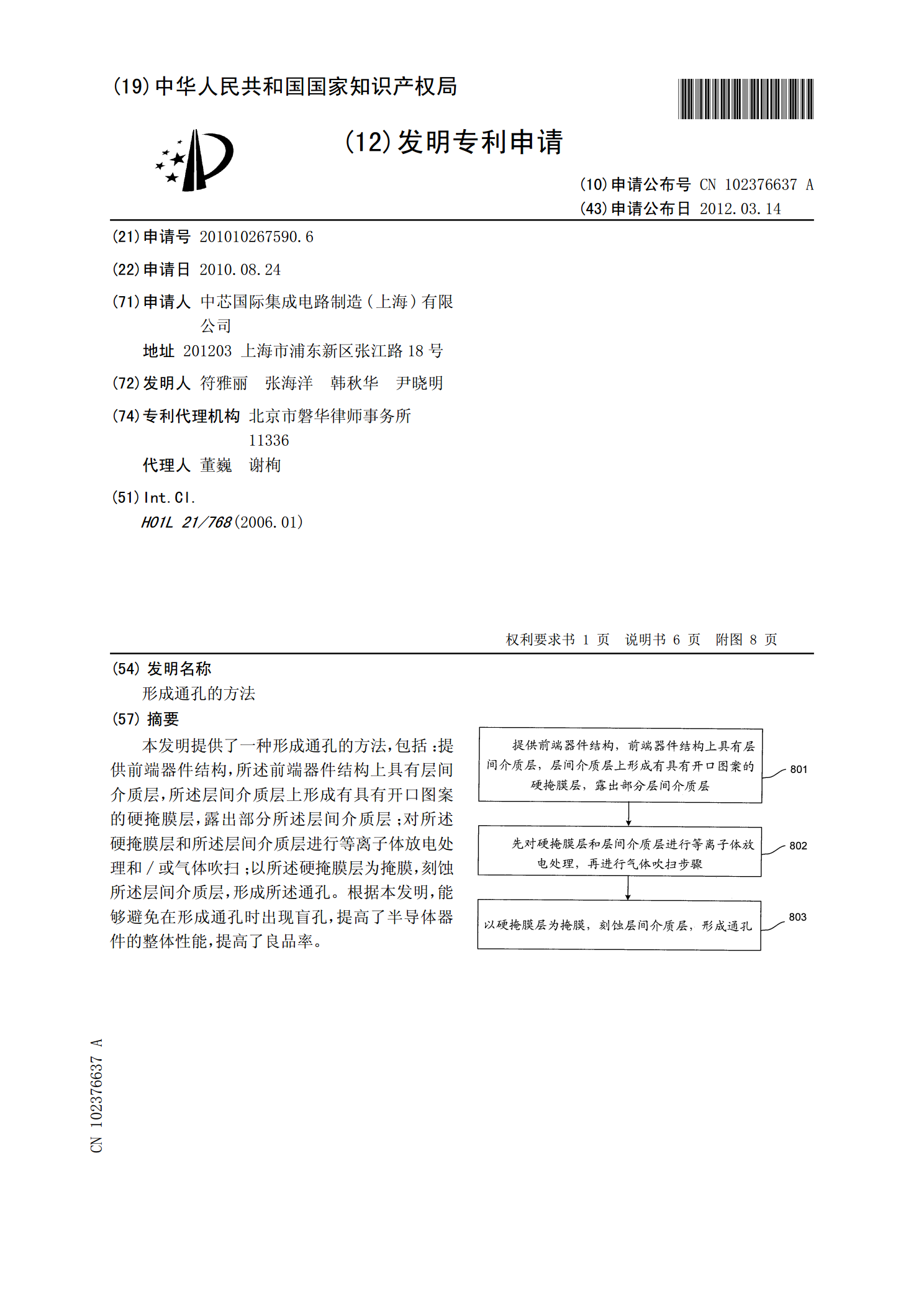

本发明提供了一种形成通孔的方法,包括:提供前端器件结构,所述前端器件结构上具有层间介质层,所述层间介质层上形成有具有开口图案的硬掩膜层,露出部分所述层间介质层;对所述硬掩膜层和所述层间介质层进行等离子体放电处理和/或气体吹扫;以所述硬掩膜层为掩膜,刻蚀所述层间介质层,形成所述通孔。根据本发明,能够避免在形成通孔时出现盲孔,提高了半导体器件的整体性能,提高了良品率。

硅通孔的形成方法.pdf

本发明提供一种硅通孔的形成方法,包括:提供衬底;在所述衬底上形成通孔;在所述通孔中填充金属层;进行第一平坦化处理,去除衬底上方的金属层,保留通孔中的金属层;在所述衬底和金属层上覆盖应力层,所述应力层用于提供压应力;对所述金属层进行再结晶处理;进行第二平坦化处理,去除衬底上方的应力层。其中,在第一平坦化处理之后,对所述金属层进行再结晶处理之前,在所述衬底和金属层上覆盖应力层,所述应力层能够提供压应力,提高金属原子向金属层表面扩散所需要的能量,从而降低金属原子向金属层表面扩散的扩散率,进而降低金属层内的空洞率

形成自对准通孔的方法.pdf

描述多种处理方法,所述方法包括:透过掩模选择性正交地生长第一材料,而提供扩展的第一材料。可移除该掩模,而留下从该第一材料的表面正交延伸的该扩展的第一材料。进一步的处理可产生自对准通孔。

硅通孔布局结构、硅通孔互联结构的形成方法.pdf

一种硅通孔布局结构、硅通孔互联结构的形成方法,其中,硅通孔互联结构的形成方法包括:提供半导体衬底,所述半导体衬底具有第一区域和第二区域;刻蚀第一区域和第二区域的半导体衬底,在第一区域和第二区域的半导体衬底中形成若干分立的通孔,第一区域的通孔密度大于通孔的平均密度,且所述通孔的平均密度小于等于2%;在所述半导体衬底上形成金属层,金属层填充满所述通孔;采用化学机械研磨工艺平坦化所述金属层,形成硅通孔互联结构。通过优化第一区域的通孔密度与半导体衬底上通孔的平均密度的关系,防止研磨后的表面金属的残留。

金属层间通孔形成方法.pdf

本发明公开了一种金属层间通孔形成方法,在介质凹槽侧壁上保留一定厚度的绝缘层材料,在后续对介质凹槽及对应通孔实施金属层间介质一体化刻蚀时,由于介质凹槽侧壁有绝缘层材料残余的保护,介质凹槽的开口尺寸保持不变不会变大,同时也是介质凹槽侧壁的残余绝缘层材料的作用,通孔相对底层金属即使有移位也不会偏移出相应的位线的底层金属外面,不会因通孔移位造成的某一边的金属间距更小,避免相邻通孔之间出现金属短接风险,增加了底层金属的通孔区域的工艺窗口,增加了次工艺的窗口边距,从而提升了金属层间通孔形成工艺的健康度。