HDI电路板及其制造方法.pdf

书錦****by

亲,该文档总共25页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

HDI电路板及其制造方法.pdf

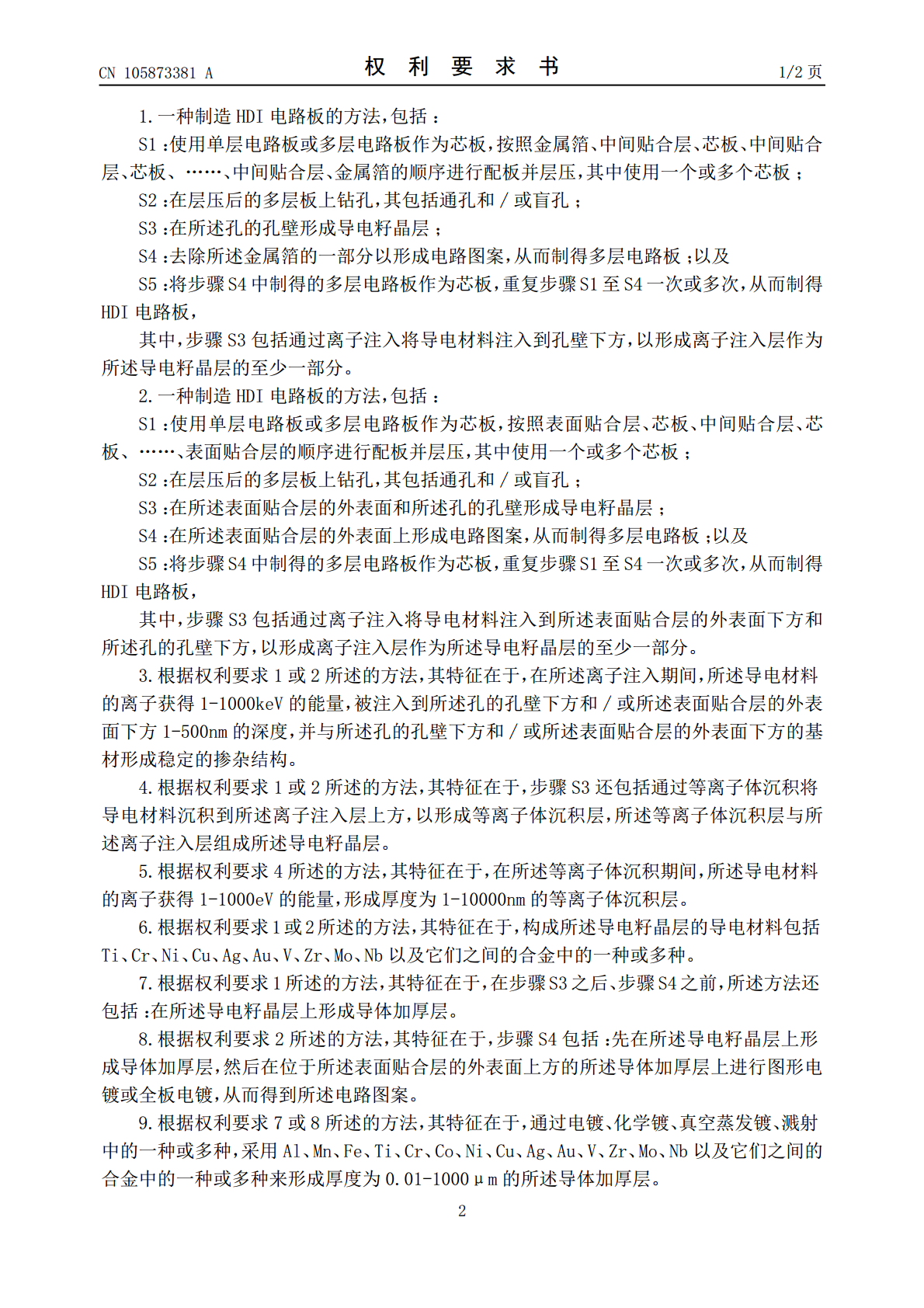

本发明涉及HDI电路板及其制造方法。一种制造HDI电路板的方法包括:使用单层电路板或多层电路板作为芯板,按照金属箔、中间贴合层、芯板、中间贴合层、芯板、……、中间贴合层、金属箔的顺序进行配板并层压,其中使用一个或多个芯板(S1);在层压后的多层板上钻孔,其包括通孔和/或盲孔(S2);在孔的孔壁形成导电籽晶层(S3);去除金属箔的一部分以形成电路图案,从而制得多层电路板(S4);以及将步骤S4中制得的多层电路板作为芯板,重复步骤S1至S4一次或多次,从而制得HDI电路板(S5),其中,步骤S3包括通过离子注

HDI板及其制造方法.pdf

本发明涉及一种HDI板及其制造方法。上述HDI板的制造方法包括如下步骤:在多层板上钻连通多层板表面和多层板的内部走线的盲孔;对多层板进行第一次化学沉铜,使盲孔电性导通多层板的内部走线;对第一次化学沉铜后的多层板进行第一次电镀;在第一次电镀后的盲孔内塞入液态树脂,并将液态树脂固化为固态树脂;将凸出于多层板表面的固态树脂打磨铲平;对多层板上的固态树脂的表面进行第二次化学沉铜,使固态树脂被密封在盲孔内。将液态树脂塞入盲孔中,塞孔饱满度高,因此可以避免孔内出现气泡、龟裂、空洞等不良现象。固态树脂打磨铲平后进行第二

电路板及其制造方法.pdf

本发明公开一种电路板及其制造方法,该电路板包括线路板及绝缘基板。线路板具有位于相反侧的第一表面及第二表面、且包含设置于第一表面上的第一线路层。其中,第一线路层包含有多个第一金属导体,并且多个第一金属导体之间分别形成有多个第一间隙。绝缘基板设置于线路板的第一表面的一侧,并且绝缘基板具有预留穿孔。其中,绝缘基板的预留穿孔与线路板包围地形成有孔穴(Cavity),并且多个第一金属导体的至少部分第一金属导体曝露于所述孔穴,而多个第一间隙的至少部分第一间隙在空间上连通于所述孔穴。

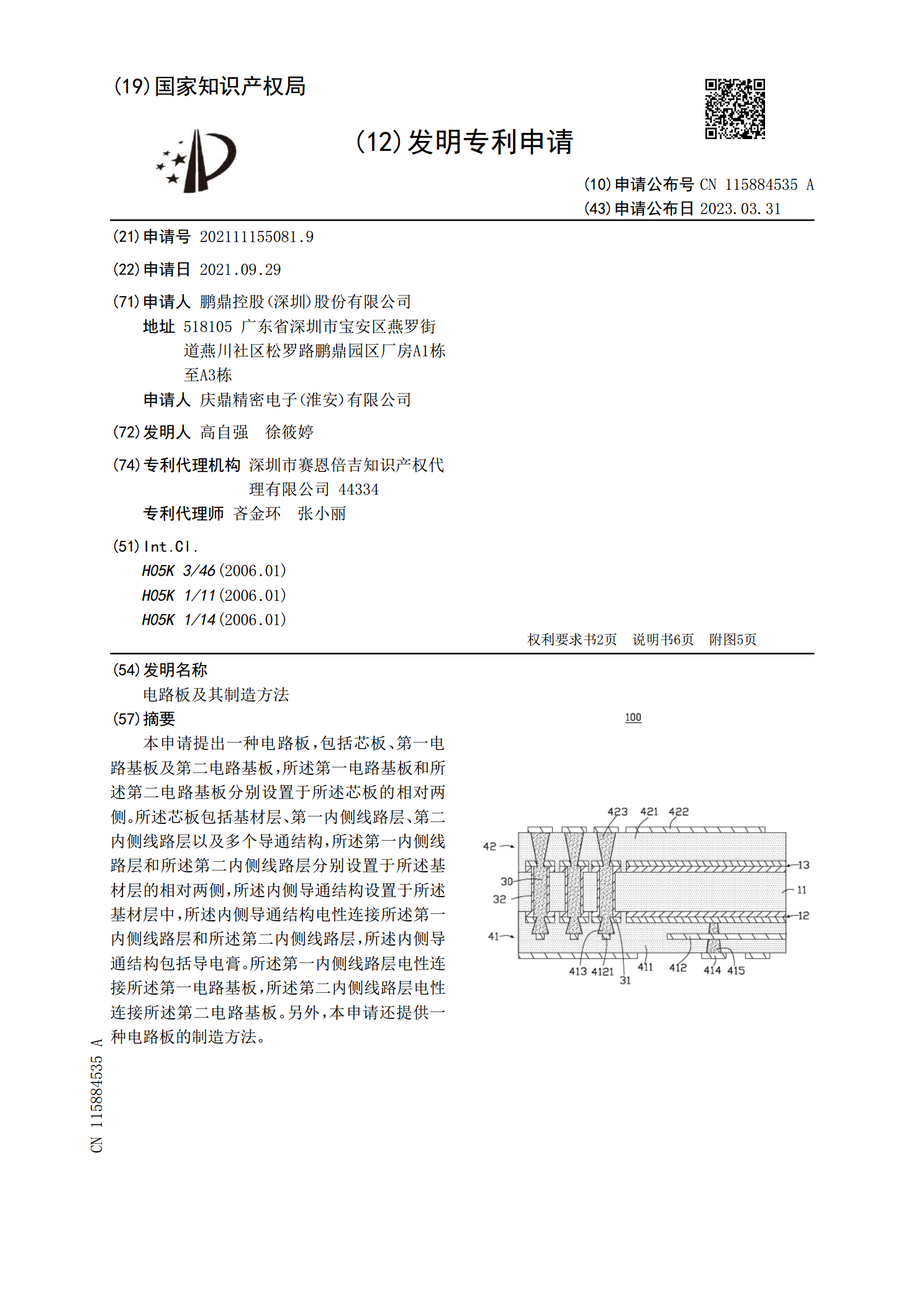

电路板及其制造方法.pdf

本申请提出一种电路板,包括芯板、第一电路基板及第二电路基板,所述第一电路基板和所述第二电路基板分别设置于所述芯板的相对两侧。所述芯板包括基材层、第一内侧线路层、第二内侧线路层以及多个导通结构,所述第一内侧线路层和所述第二内侧线路层分别设置于所述基材层的相对两侧,所述内侧导通结构设置于所述基材层中,所述内侧导通结构电性连接所述第一内侧线路层和所述第二内侧线路层,所述内侧导通结构包括导电膏。所述第一内侧线路层电性连接所述第一电路基板,所述第二内侧线路层电性连接所述第二电路基板。另外,本申请还提供一种电路板的制

电路板及其制造方法.pdf

一种电路板制造方法,包括:提供一包括一基底层和形成于基底层一侧的第一铜层的覆铜基板。在覆铜基板中开设盲孔,并在第一铜层上形成一镀铜层,部分镀铜层填充于盲孔中以形成导电部。于镀铜层上覆盖一第一感光膜,并对第一感光膜进行曝光显影以获得呈梯形结构的第一感光图案,第一感光图案覆盖导电部以及镀铜层围绕导电部设置的部分。通过第一感光图案对镀铜层进行蚀刻,得到位于导电部上的焊垫,焊垫包括远离第一铜层的第三表面及从第三表面向第一铜层延伸形成的一弯曲的第四表面。剥离第一感光图案以及蚀刻第一铜层,从而得到一第一导电线路层。本