一种复位延时鉴频鉴相器和一种锁相环频率合成器.pdf

是你****盟主

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种复位延时鉴频鉴相器和一种锁相环频率合成器.pdf

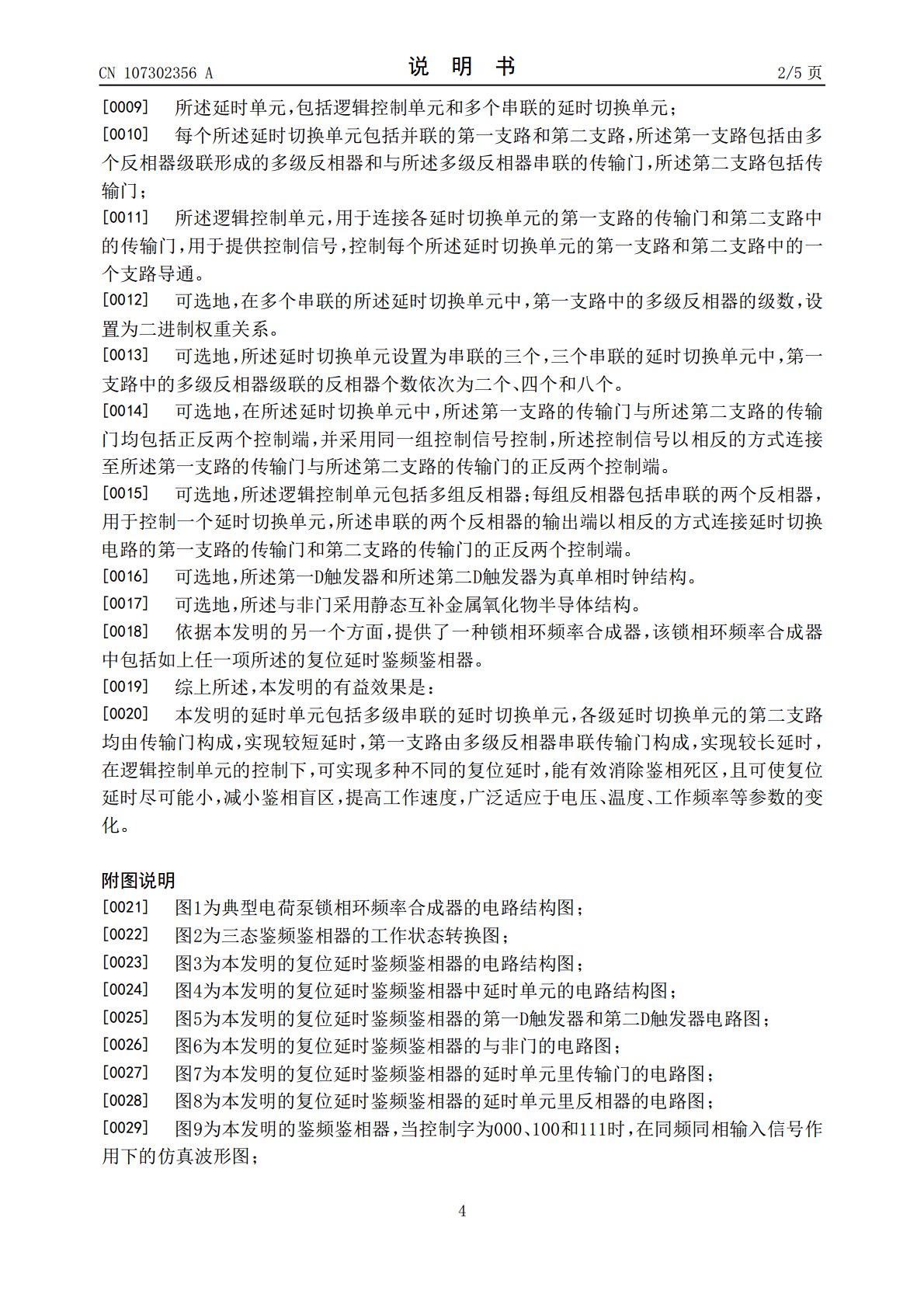

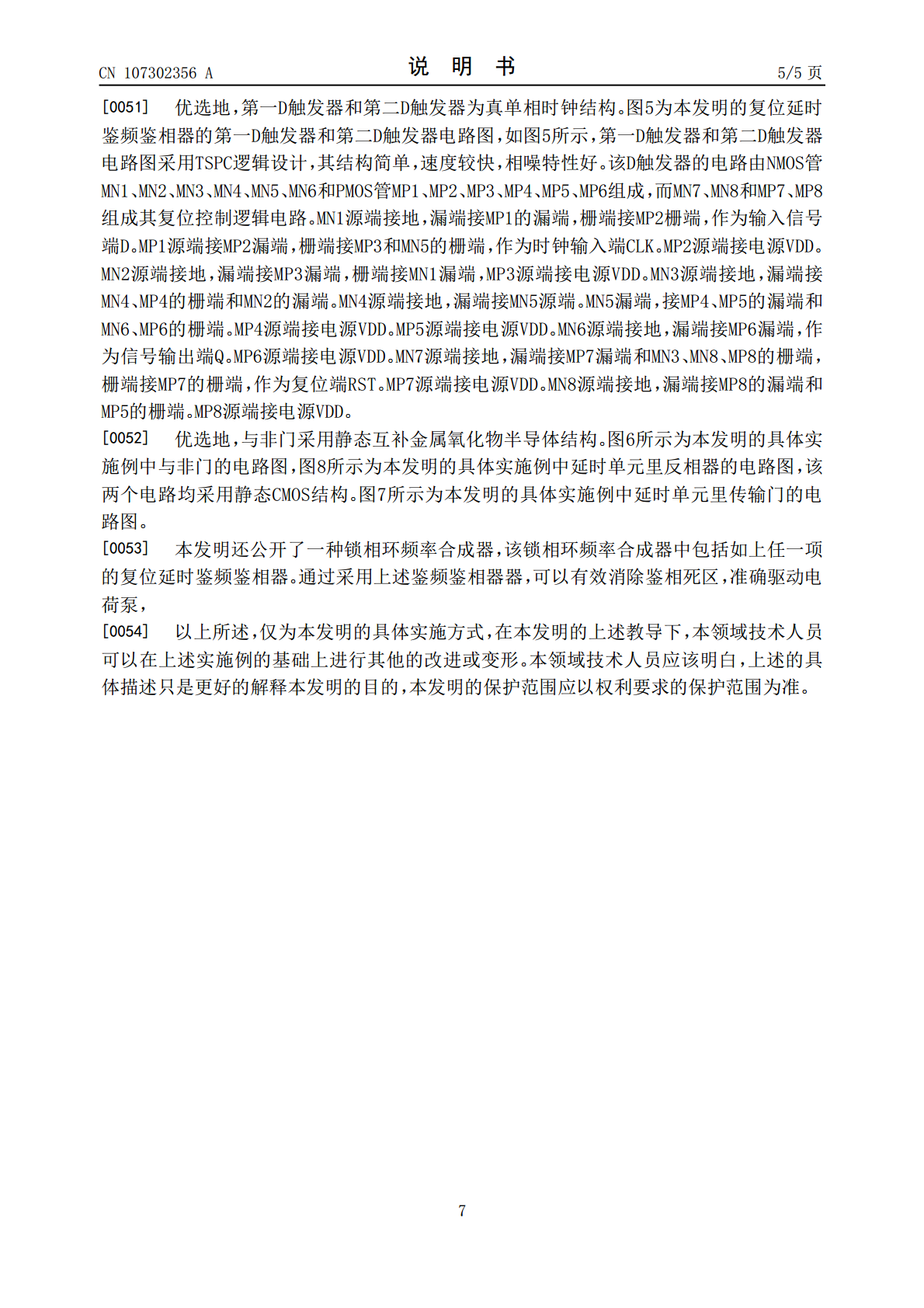

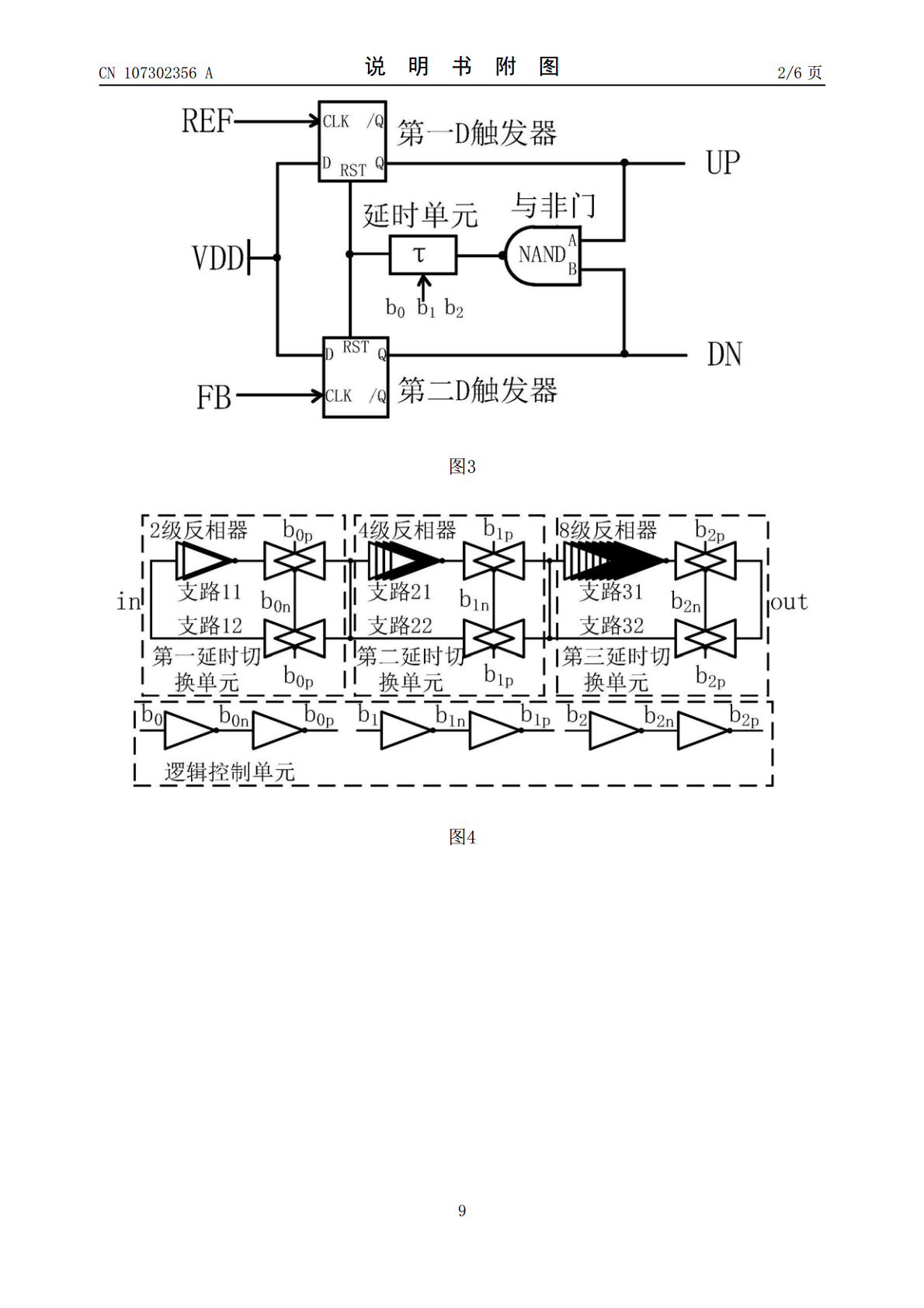

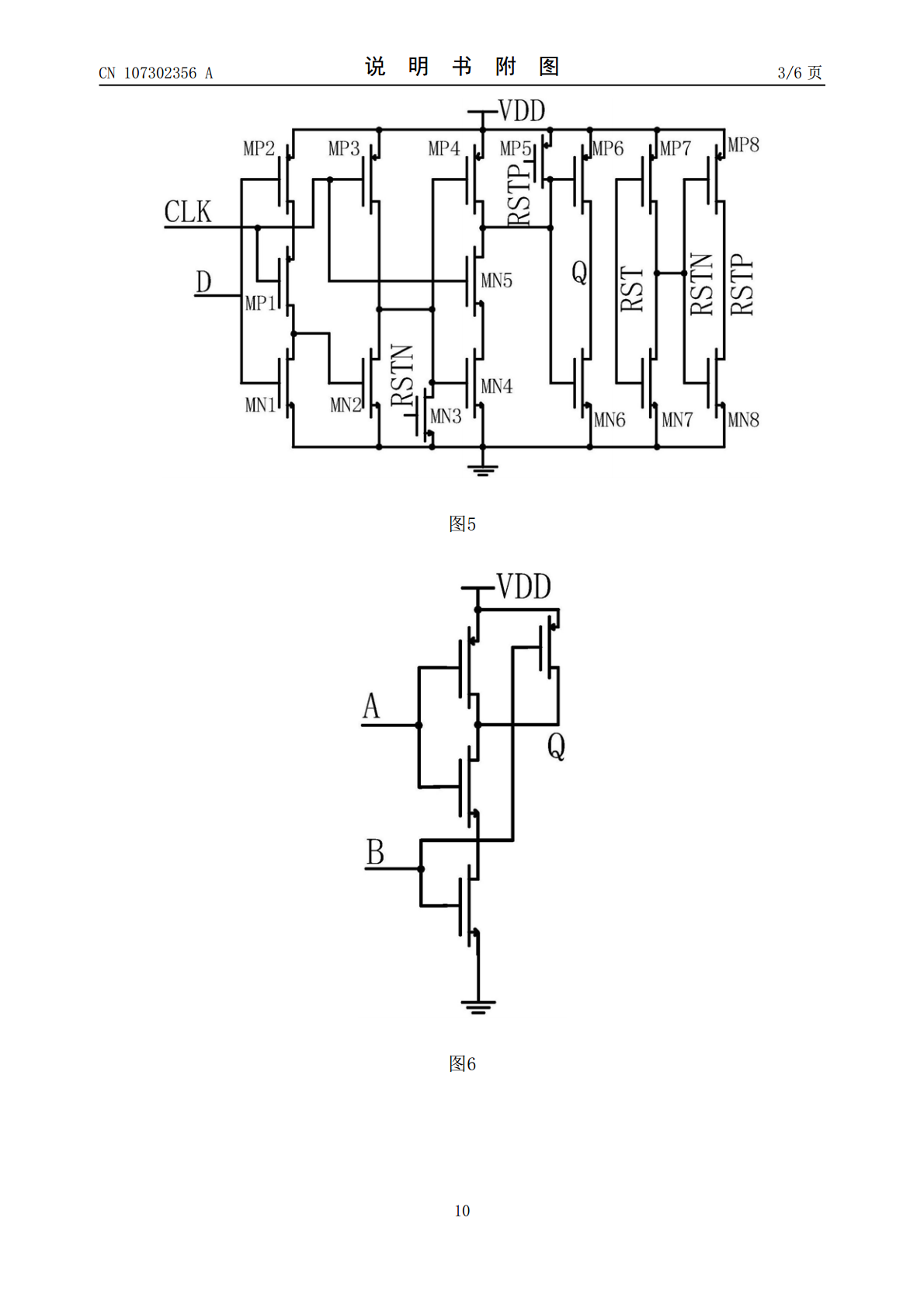

本发明公开了一种复位延时鉴频鉴相器和一种锁相环频率合成器。该复位延时鉴频鉴相器的复位路径中增加有一个基于传输门结构的延时单元,该延时单元,包括逻辑控制单元和多个串联的延时切换单元;每个延时切换单元包括并联的第一支路和第二支路,第一支路包括由多个反相器级联形成的多级反相器和与多级反相器串联的传输门,第二支路包括传输门;逻辑控制单元,用于连接各延时切换单元的第一支路的传输门和第二支路中的传输门,用于提供控制信号,控制每个延时切换单元的第一支路和第二支路中的一个支路导通。本发明的延时单元可实现多种不同的复位延时

锁相环频率合成器的鉴频鉴相器和电荷泵设计.docx

锁相环频率合成器的鉴频鉴相器和电荷泵设计锁相环频率合成器是一种常用的频率合成技术,其主要作用是将一个参考信号的频率精确地调制到期望的频率上。其核心电路包括相频检测器、电荷泵、低通滤波器和VCO(VoltageControlledOscillator)。其中,相频检测器负责检测输入信号和参考信号之间的相位和频率差异,电荷泵则负责根据检测结果对VCO进行调节,以使其输出的频率与期望频率保持一致。在锁相环频率合成器中,鉴频鉴相器和电荷泵是关键的部件,其设计的好坏将直接影响锁相环频率合成器的性能和精度。一、鉴频鉴

CMOS锁相环中鉴频鉴相器的研究.docx

CMOS锁相环中鉴频鉴相器的研究CMOS锁相环中鉴频鉴相器的研究引言:随着现代通信系统对于低功耗、高性能的要求不断增加,锁相环(PLL)作为一种重要的时钟生成和信号处理技术得到广泛应用。而锁相环中的鉴频鉴相器是其关键组成部分,直接影响了锁相环的性能和稳定性。因此,对于CMOS锁相环中鉴频鉴相器的研究具有很大的意义。一、锁相环(PLL)的基本原理锁相环是一种基础的反馈控制系统,主要由相位比较器、带通滤波器、电压控制振荡器(VCO)和分频器组成。其工作原理是不断调整参考信号和VCO产生的信号之间的相位差,使其

鉴频鉴相器电路.pdf

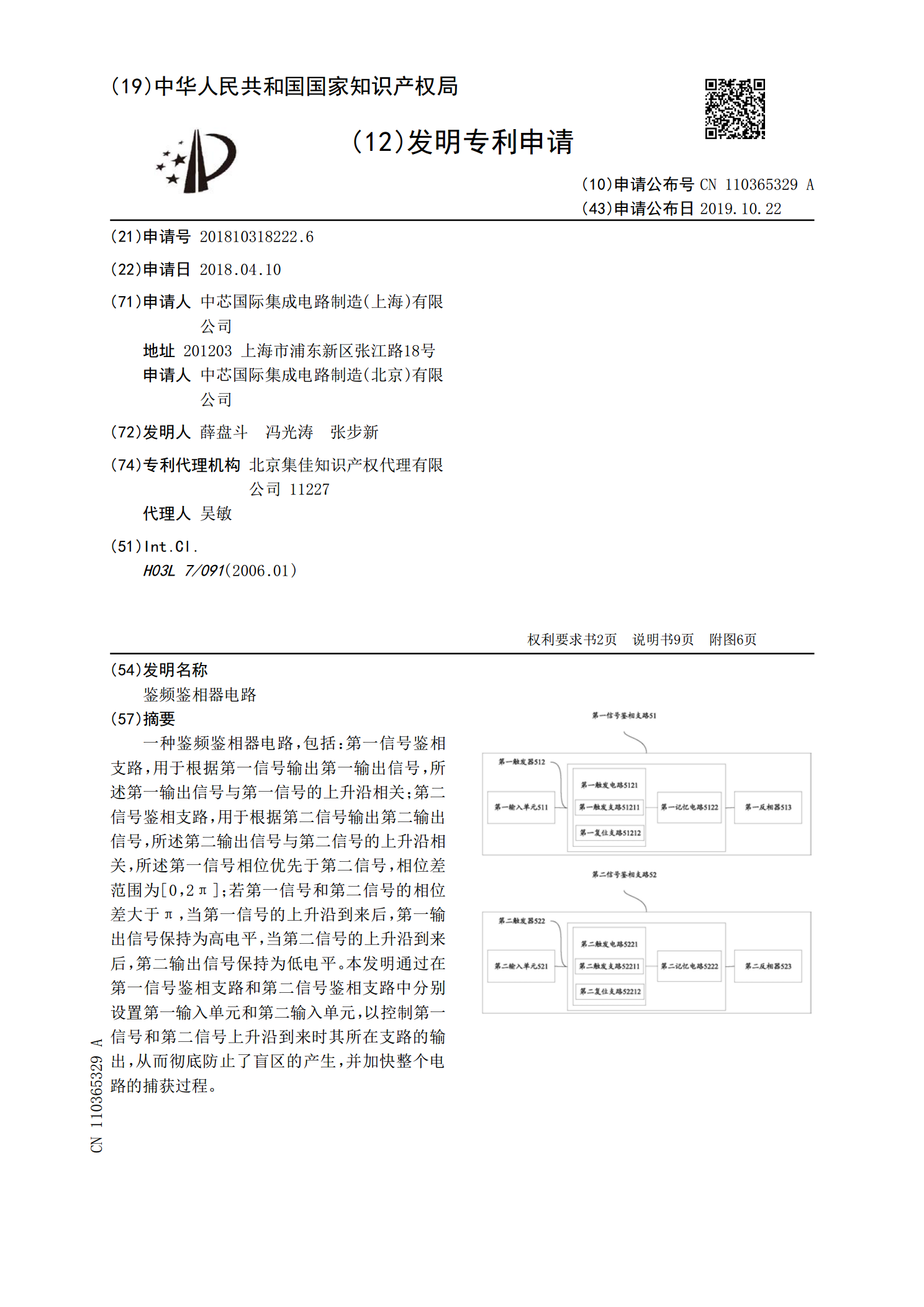

一种鉴频鉴相器电路,包括:第一信号鉴相支路,用于根据第一信号输出第一输出信号,所述第一输出信号与第一信号的上升沿相关;第二信号鉴相支路,用于根据第二信号输出第二输出信号,所述第二输出信号与第二信号的上升沿相关,所述第一信号相位优先于第二信号,相位差范围为[0,2π];若第一信号和第二信号的相位差大于π,当第一信号的上升沿到来后,第一输出信号保持为高电平,当第二信号的上升沿到来后,第二输出信号保持为低电平。本发明通过在第一信号鉴相支路和第二信号鉴相支路中分别设置第一输入单元和第二输入单元,以控制第一信号和第

射频锁相环中鉴频鉴相器和电荷泵的设计的任务书.docx

射频锁相环中鉴频鉴相器和电荷泵的设计的任务书射频锁相环是一种广泛应用于通信、雷达等领域的电路,用于提取和跟踪输入信号中的特定频率成分。鉴频鉴相器和电荷泵是射频锁相环的基本组成部分,负责解调和调节输入信号。任务书内容如下:一、任务目标设计一个射频锁相环中的鉴频鉴相器和电荷泵电路,要求能够有效提取和跟踪输入信号的特定频率成分。二、任务背景射频锁相环是一种通过频率和相位反馈控制的闭环反馈系统,广泛应用于通信、雷达等领域。鉴频鉴相器和电荷泵是射频锁相环的核心部分,负责解调和调节输入信号。三、任务要求1.设计一个基