鉴频鉴相器电路.pdf

猫巷****熙柔

亲,该文档总共18页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

鉴频鉴相器电路.pdf

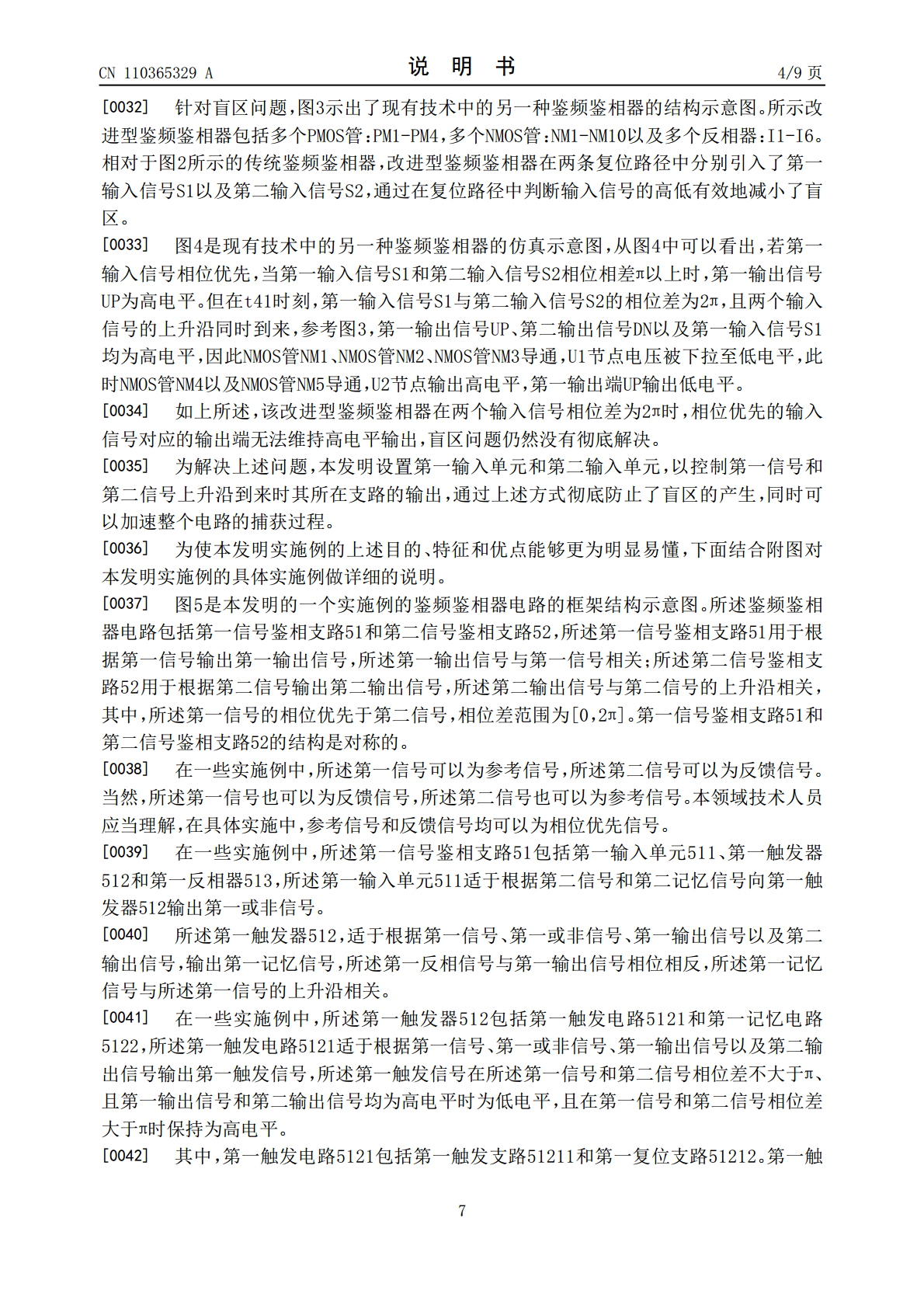

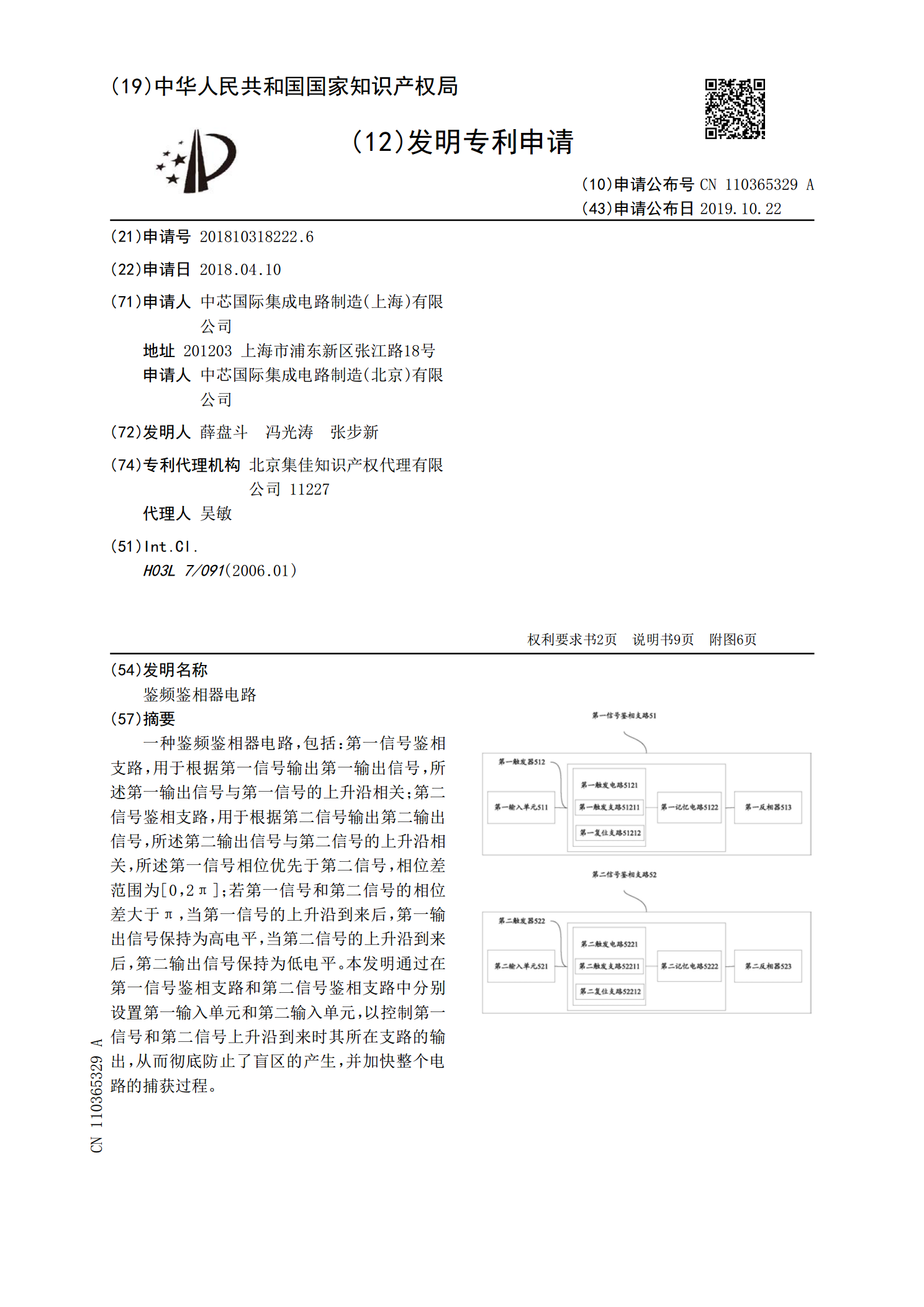

一种鉴频鉴相器电路,包括:第一信号鉴相支路,用于根据第一信号输出第一输出信号,所述第一输出信号与第一信号的上升沿相关;第二信号鉴相支路,用于根据第二信号输出第二输出信号,所述第二输出信号与第二信号的上升沿相关,所述第一信号相位优先于第二信号,相位差范围为[0,2π];若第一信号和第二信号的相位差大于π,当第一信号的上升沿到来后,第一输出信号保持为高电平,当第二信号的上升沿到来后,第二输出信号保持为低电平。本发明通过在第一信号鉴相支路和第二信号鉴相支路中分别设置第一输入单元和第二输入单元,以控制第一信号和第

D触发器及鉴频鉴相器电路.pdf

本发明涉及一种D触发器及鉴频鉴相器电路。其中,D触发器通过输入电路、预充电路和输出电路构成真单一时钟逻辑结构动态D触发器,实现D触发器的基本功能。同时,通过第一锁存电路,稳定D触发器在工作频率较低时预充电路输出端的电位,以拓展D触发器的工作频率范围。同时,鉴频鉴相器通过采用宽工作频率范围的第一D触发器和第二D触发器,拓展鉴频鉴相器的工作频率范围。同时,在引入控制信号后,通过第一控制模块和第二控制模块,使参考时钟信号和反馈时钟信号的相位差在π至2π时,复位反馈电路不会产生输出至第一D触发器和第二D触发器的复

CMOS锁相环中鉴频鉴相器的研究.docx

CMOS锁相环中鉴频鉴相器的研究CMOS锁相环中鉴频鉴相器的研究引言:随着现代通信系统对于低功耗、高性能的要求不断增加,锁相环(PLL)作为一种重要的时钟生成和信号处理技术得到广泛应用。而锁相环中的鉴频鉴相器是其关键组成部分,直接影响了锁相环的性能和稳定性。因此,对于CMOS锁相环中鉴频鉴相器的研究具有很大的意义。一、锁相环(PLL)的基本原理锁相环是一种基础的反馈控制系统,主要由相位比较器、带通滤波器、电压控制振荡器(VCO)和分频器组成。其工作原理是不断调整参考信号和VCO产生的信号之间的相位差,使其

基于FPGA的一种新型数字鉴频鉴相器的设计.docx

基于FPGA的一种新型数字鉴频鉴相器的设计随着数字通信技术的不断发展,数字鉴频鉴相器的应用越来越广泛。数字鉴频鉴相技术能够在数字通信中实现信号的鉴频和鉴相,提高信道传输效率和减少传输误差。本文基于FPGA设计了一种新型数字鉴频鉴相器,旨在提高数字通信系统的鉴频鉴相能力。一、FPGA技术FPGA,即现场可编程逻辑门阵列,是一种可编程的数字电路芯片。FPGA在数字电路设计中具有诸多优点,如实时性好、低功耗、低成本、易于设计、可重构等。在本文中,我们利用FPGA技术实现数字鉴频鉴相器的设计。二、数字鉴频鉴相的原

H调谐器的CMOS鉴频鉴相器和电荷泵的设计的开题报告.docx

应用于DVB-T/H调谐器的CMOS鉴频鉴相器和电荷泵的设计的开题报告1.研究背景随着数字电视的发展,DVB-T/H成为了广泛应用的数字电视标准,DVB-T/H调谐器也成为了数字电视中的重要组成部分。而在DVB-T/H调谐器中,鉴频鉴相器和电荷泵是核心设计部件,对调谐器的性能和功耗有着重要的影响。2.研究目的本文旨在研究基于CMOS工艺的鉴频鉴相器和电荷泵的设计,并采用相应的仿真工具进行验证。通过对鉴频鉴相器和电荷泵的设计和仿真分析,得到一个在DVB-T/H调谐器中可应用的优良性能的设计方案。3.研究内容