CMOS锁相环中鉴频鉴相器的研究.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

CMOS锁相环中鉴频鉴相器的研究.docx

CMOS锁相环中鉴频鉴相器的研究CMOS锁相环中鉴频鉴相器的研究引言:随着现代通信系统对于低功耗、高性能的要求不断增加,锁相环(PLL)作为一种重要的时钟生成和信号处理技术得到广泛应用。而锁相环中的鉴频鉴相器是其关键组成部分,直接影响了锁相环的性能和稳定性。因此,对于CMOS锁相环中鉴频鉴相器的研究具有很大的意义。一、锁相环(PLL)的基本原理锁相环是一种基础的反馈控制系统,主要由相位比较器、带通滤波器、电压控制振荡器(VCO)和分频器组成。其工作原理是不断调整参考信号和VCO产生的信号之间的相位差,使其

射频锁相环中鉴频鉴相器和电荷泵的设计的开题报告.docx

射频锁相环中鉴频鉴相器和电荷泵的设计的开题报告一、研究背景随着现代通信技术的发展和应用的不断扩大,高性能、低功耗的射频锁相环(PLL)逐渐成为了通信领域中不可或缺的关键器件。射频锁相环的核心部分是鉴频鉴相器和电荷泵,它们能够将输入信号与内部参考信号进行比较,从而实现频率的锁定。目前,射频锁相环中鉴频鉴相器和电荷泵的设计已经成为了研究的热点之一。在过去,研究人员主要关注于提高锁相环的稳定性和抗干扰能力。但是,随着移动通信技术的进一步发展,特别是5G技术的到来,对于射频锁相环的要求越来越高。因此,如何在保证锁

射频锁相环中鉴频鉴相器和电荷泵的设计的任务书.docx

射频锁相环中鉴频鉴相器和电荷泵的设计的任务书射频锁相环是一种广泛应用于通信、雷达等领域的电路,用于提取和跟踪输入信号中的特定频率成分。鉴频鉴相器和电荷泵是射频锁相环的基本组成部分,负责解调和调节输入信号。任务书内容如下:一、任务目标设计一个射频锁相环中的鉴频鉴相器和电荷泵电路,要求能够有效提取和跟踪输入信号的特定频率成分。二、任务背景射频锁相环是一种通过频率和相位反馈控制的闭环反馈系统,广泛应用于通信、雷达等领域。鉴频鉴相器和电荷泵是射频锁相环的核心部分,负责解调和调节输入信号。三、任务要求1.设计一个基

锁相环中鉴相器和环路滤波器的设计.docx

锁相环中鉴相器和环路滤波器的设计锁相环(Phase-LockedLoop,PLL)是一种经典的电子电路,常被用于提取或生成和输入信号相位相同的输出信号。在锁相环中,鉴相器(PhaseDetector)和环路滤波器(LoopFilter)是两个非常重要的组成部分。它们相互配合,起到控制锁相环的作用,保证输出信号和输入信号具有良好的相位和频率同步性。本文将详细介绍锁相环中鉴相器和环路滤波器的设计原理和方法。一、鉴相器的设计鉴相器是锁相环的核心部分,它用于比较输入信号和输出信号的相位差,并产生相位误差信号。常见

鉴频鉴相器电路.pdf

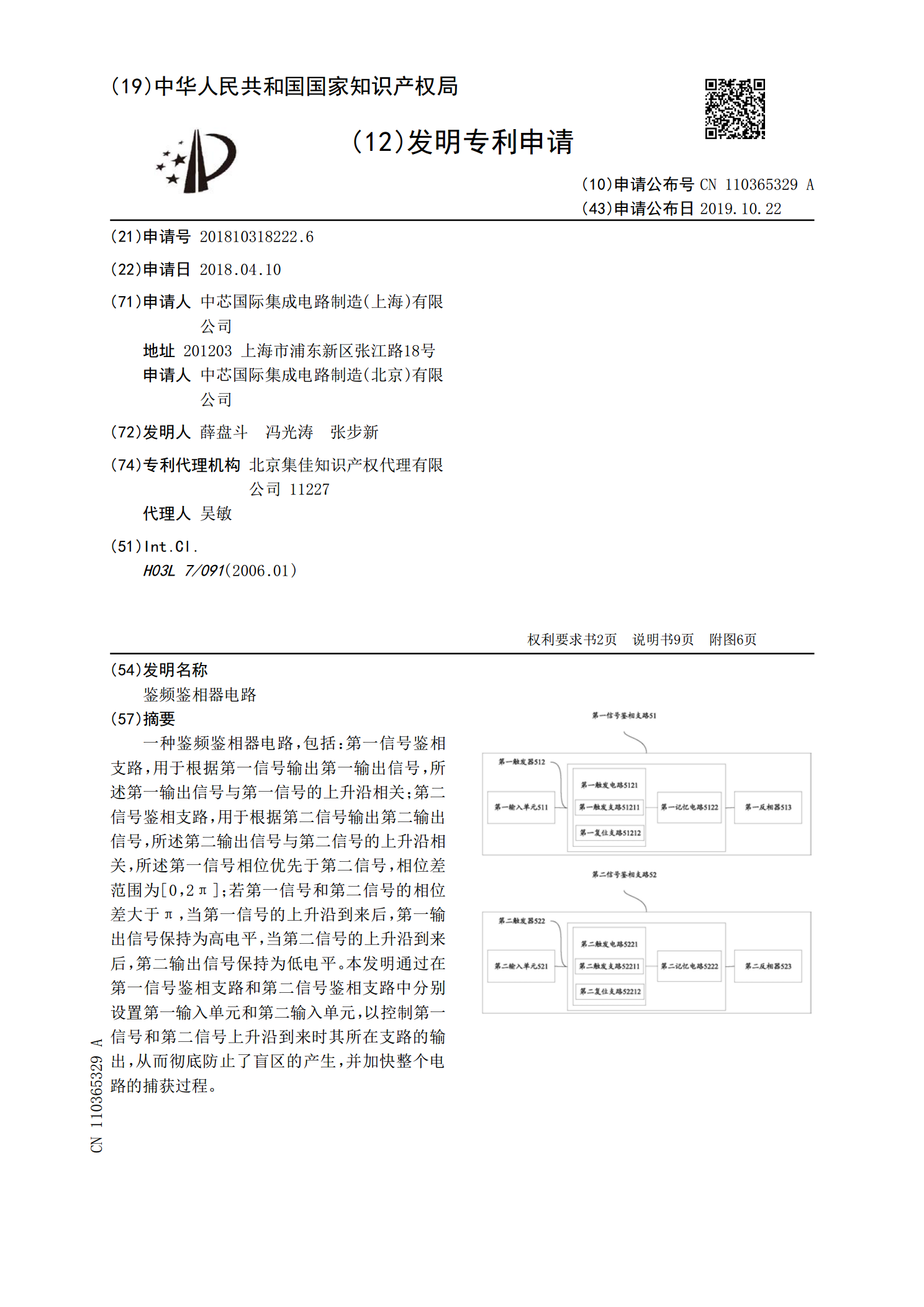

一种鉴频鉴相器电路,包括:第一信号鉴相支路,用于根据第一信号输出第一输出信号,所述第一输出信号与第一信号的上升沿相关;第二信号鉴相支路,用于根据第二信号输出第二输出信号,所述第二输出信号与第二信号的上升沿相关,所述第一信号相位优先于第二信号,相位差范围为[0,2π];若第一信号和第二信号的相位差大于π,当第一信号的上升沿到来后,第一输出信号保持为高电平,当第二信号的上升沿到来后,第二输出信号保持为低电平。本发明通过在第一信号鉴相支路和第二信号鉴相支路中分别设置第一输入单元和第二输入单元,以控制第一信号和第