一种零盲区测距系统.pdf

小云****66

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种零盲区测距系统.pdf

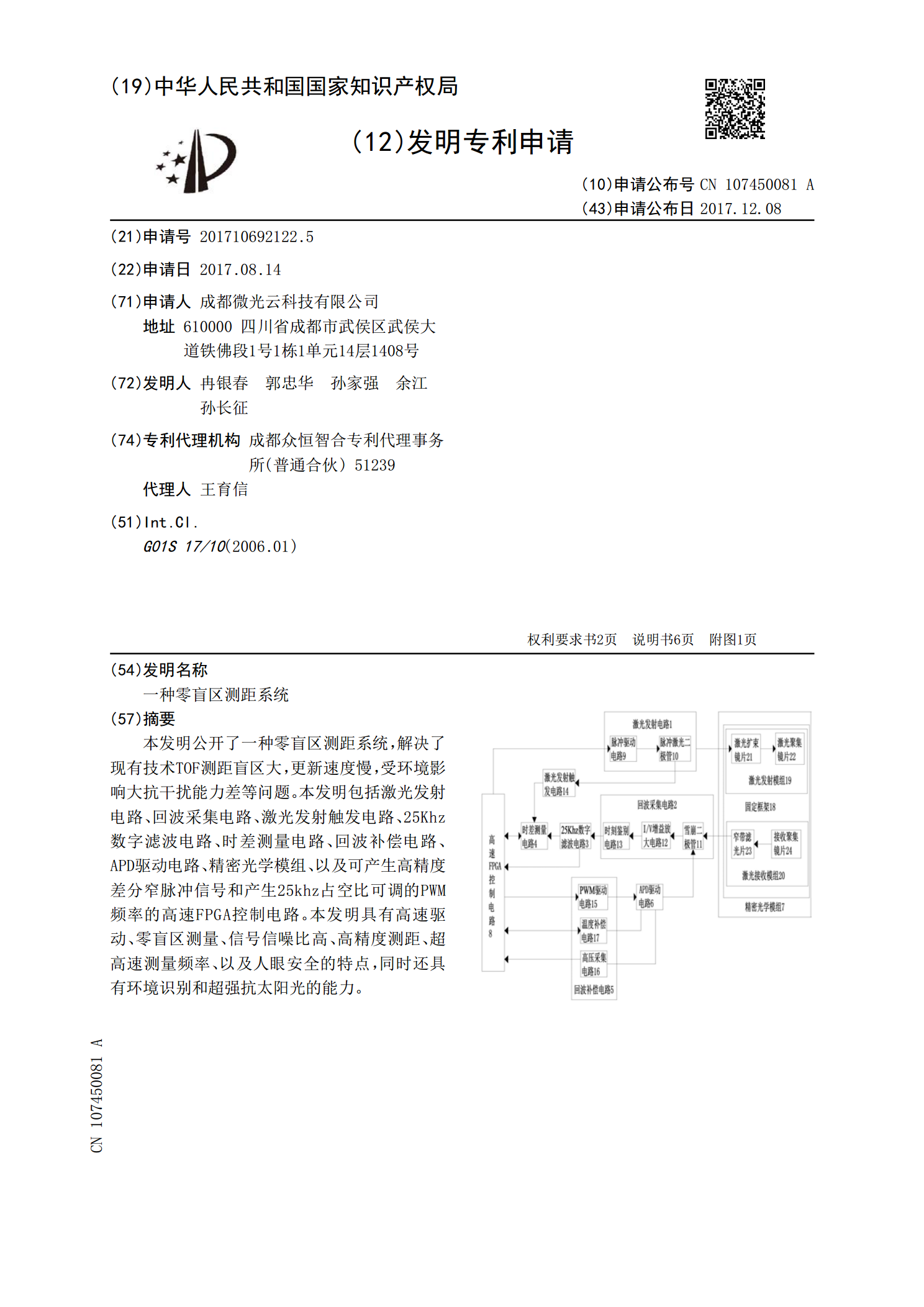

本发明公开了一种零盲区测距系统,解决了现有技术TOF测距盲区大,更新速度慢,受环境影响大抗干扰能力差等问题。本发明包括激光发射电路、回波采集电路、激光发射触发电路、25Khz数字滤波电路、时差测量电路、回波补偿电路、APD驱动电路、精密光学模组、以及可产生高精度差分窄脉冲信号和产生25khz占空比可调的PWM频率的高速FPGA控制电路。本发明具有高速驱动、零盲区测量、信号信噪比高、高精度测距、超高速测量频率、以及人眼安全的特点,同时还具有环境识别和超强抗太阳光的能力。

一种消除激光雷达盲区的测距方法及测距系统.pdf

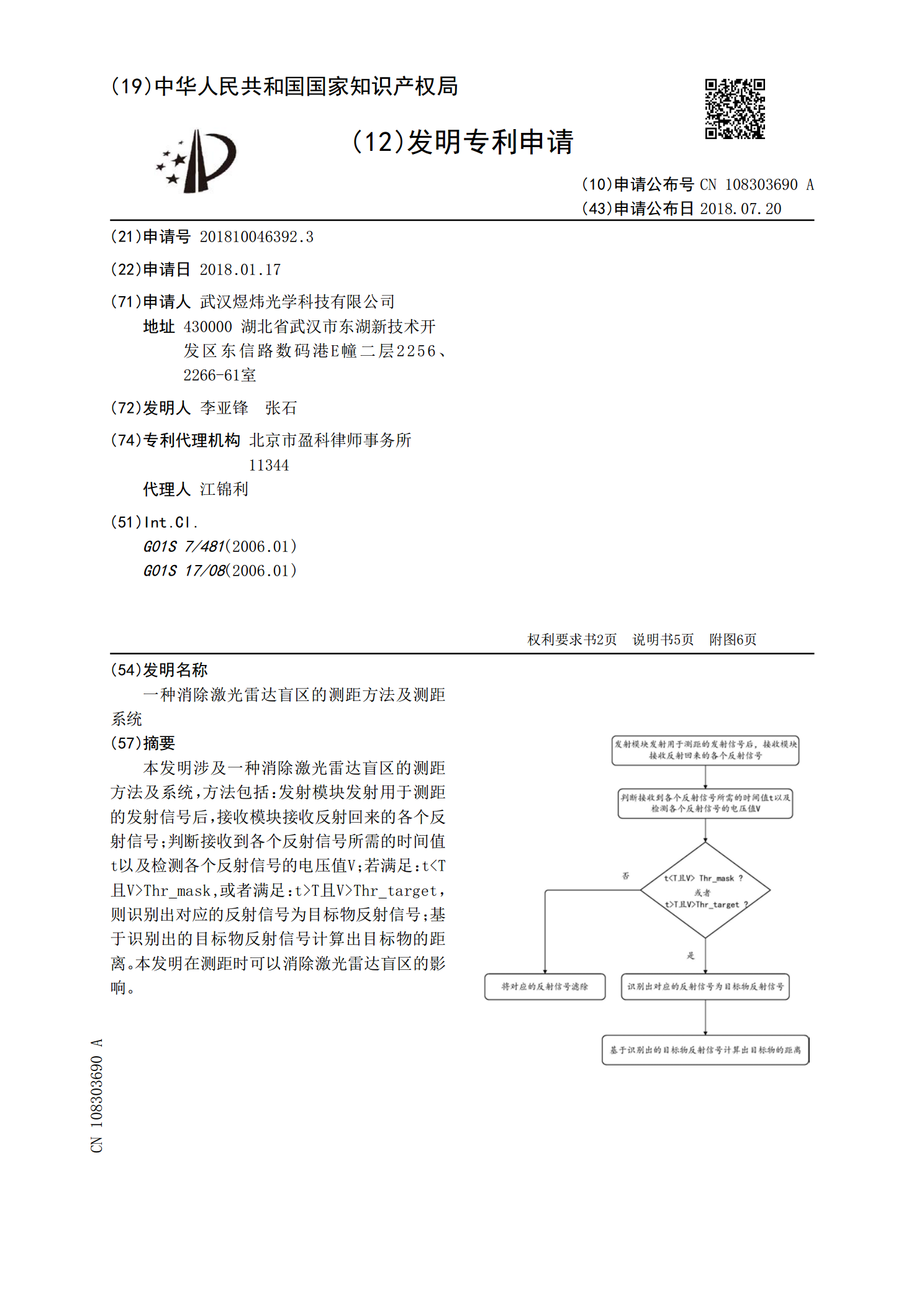

本发明涉及一种消除激光雷达盲区的测距方法及系统,方法包括:发射模块发射用于测距的发射信号后,接收模块接收反射回来的各个反射信号;判断接收到各个反射信号所需的时间值t以及检测各个反射信号的电压值V;若满足:tThr_mask,或者满足:t>T且V>Thr_target,则识别出对应的反射信号为目标物反射信号;基于识别出的目标物反射信号计算出目标物的距离。本发明在测距时可以消除激光雷达盲区的影响。

一种无盲区超声波测距探头及测距方法.pdf

本发明公开了一种无盲区超声波测距探头及测距方法,该探头包括处于同一平面上的超声波发射器T、第一超声波接收器R

一种汽车盲区测距警报装置.pdf

本发明公开了一种汽车盲区测距警报装置,包括安装在汽车的驾驶舱内的控制装置,于汽车的一对前照灯处分别安装有采集汽车前方图像的前置图像采集装置,于汽车的一对后视镜的镜架下分别安装有一对采集汽车侧方图像的侧方图像采集装置,于汽车的一对后照灯处分别安装有后置图像采集装置,前置图像采集装置、侧方图像采集装置、后置图像采集装置与控制装置信号连接。本发明结构新颖,采用多角度设置图像采集装置,通过图像整合修正,克服汽车盲区难题,有利于驾驶员掌握障碍物的实际大小、运动情况、具体位置,大大提高了汽车行驶的安全可靠性,避免事故

一种车载超低盲区双探头超声波测距系统及方法.pdf

本发明公开了一种车载超低盲区双探头超声波测距系统及方法,包括收发装置和信号处理装置。收发装置包括发射探头和接收探头,信号处理装置包括主控模块、通信模块、发射驱动模块和接收调理模块。主控模块通过发射驱动模块与发射探头电连接,主控模块通过接收调理模块与接收探头电连接。主控模块与通信模块电连接,通信模块用于与车载控制系统通信连接。本发明先通过发射驱动模块控制发射探头发出探测超声波;再利用接收探头和接收调理电路接收探测超声波的回波信号;然后根据回波信号计算并得到障碍物的距离信息,最后发送所述距离信息至车载控制系统