D触发器及鉴频鉴相器电路.pdf

运升****魔王

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

D触发器及鉴频鉴相器电路.pdf

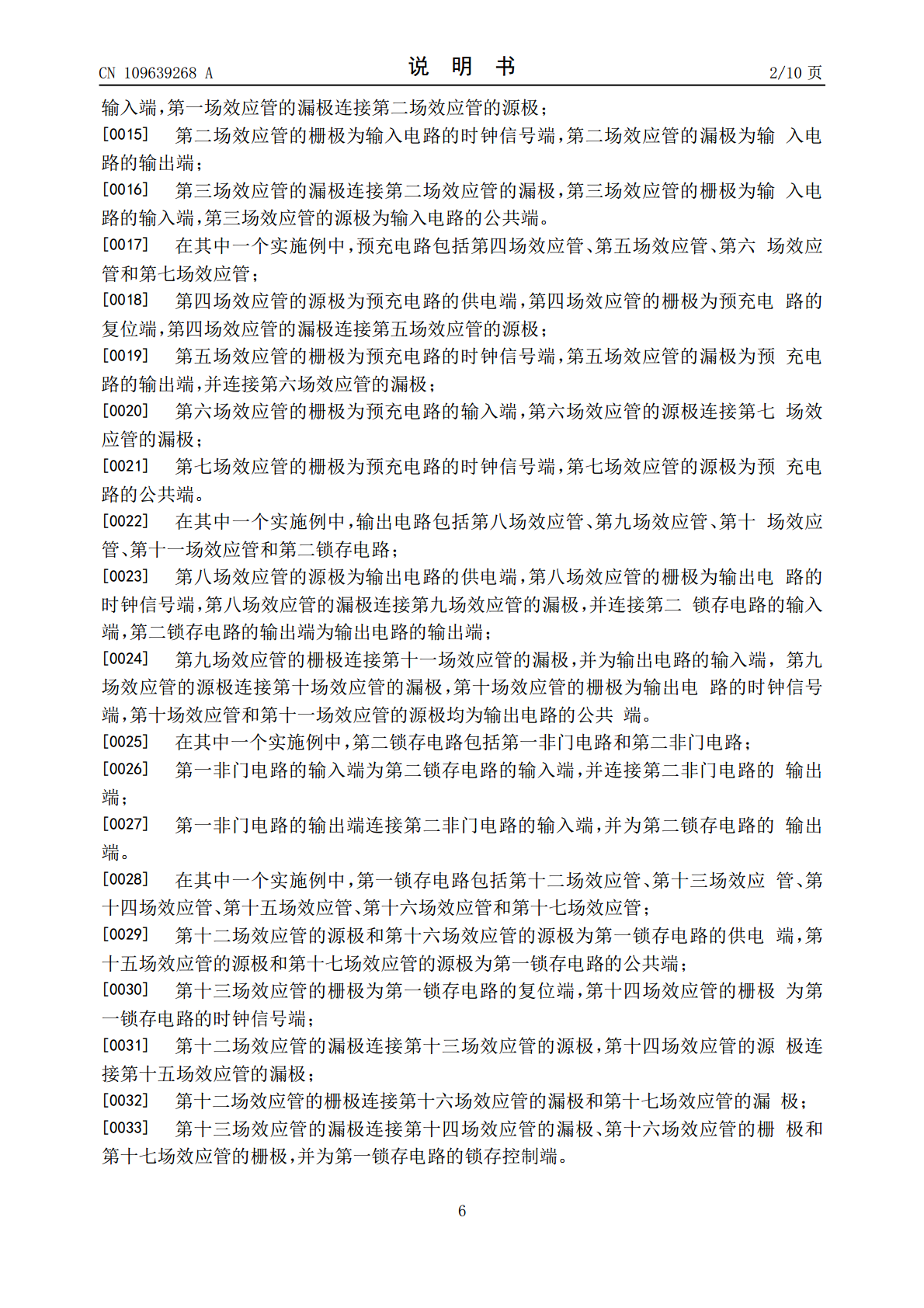

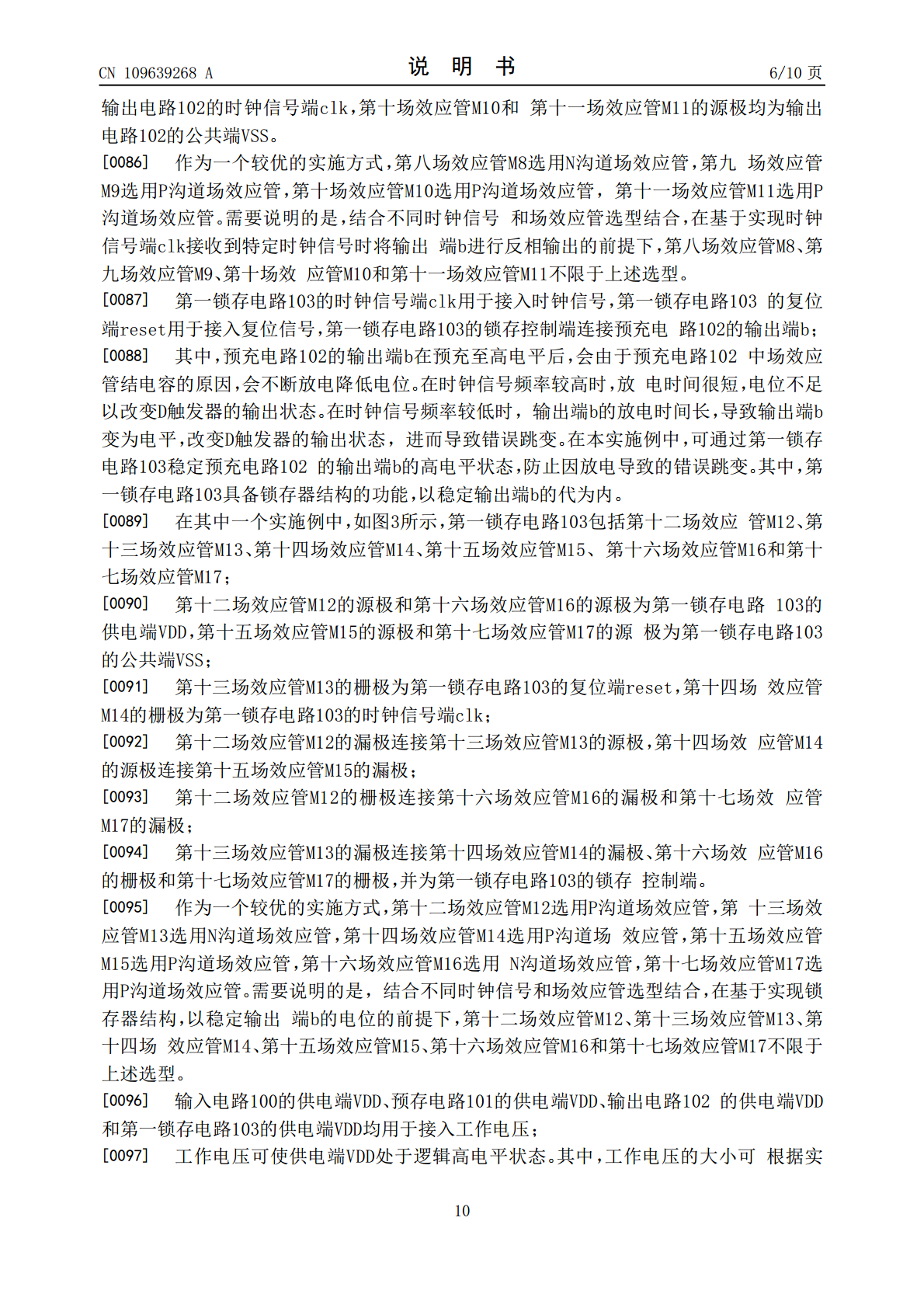

本发明涉及一种D触发器及鉴频鉴相器电路。其中,D触发器通过输入电路、预充电路和输出电路构成真单一时钟逻辑结构动态D触发器,实现D触发器的基本功能。同时,通过第一锁存电路,稳定D触发器在工作频率较低时预充电路输出端的电位,以拓展D触发器的工作频率范围。同时,鉴频鉴相器通过采用宽工作频率范围的第一D触发器和第二D触发器,拓展鉴频鉴相器的工作频率范围。同时,在引入控制信号后,通过第一控制模块和第二控制模块,使参考时钟信号和反馈时钟信号的相位差在π至2π时,复位反馈电路不会产生输出至第一D触发器和第二D触发器的复

鉴频鉴相器电路.pdf

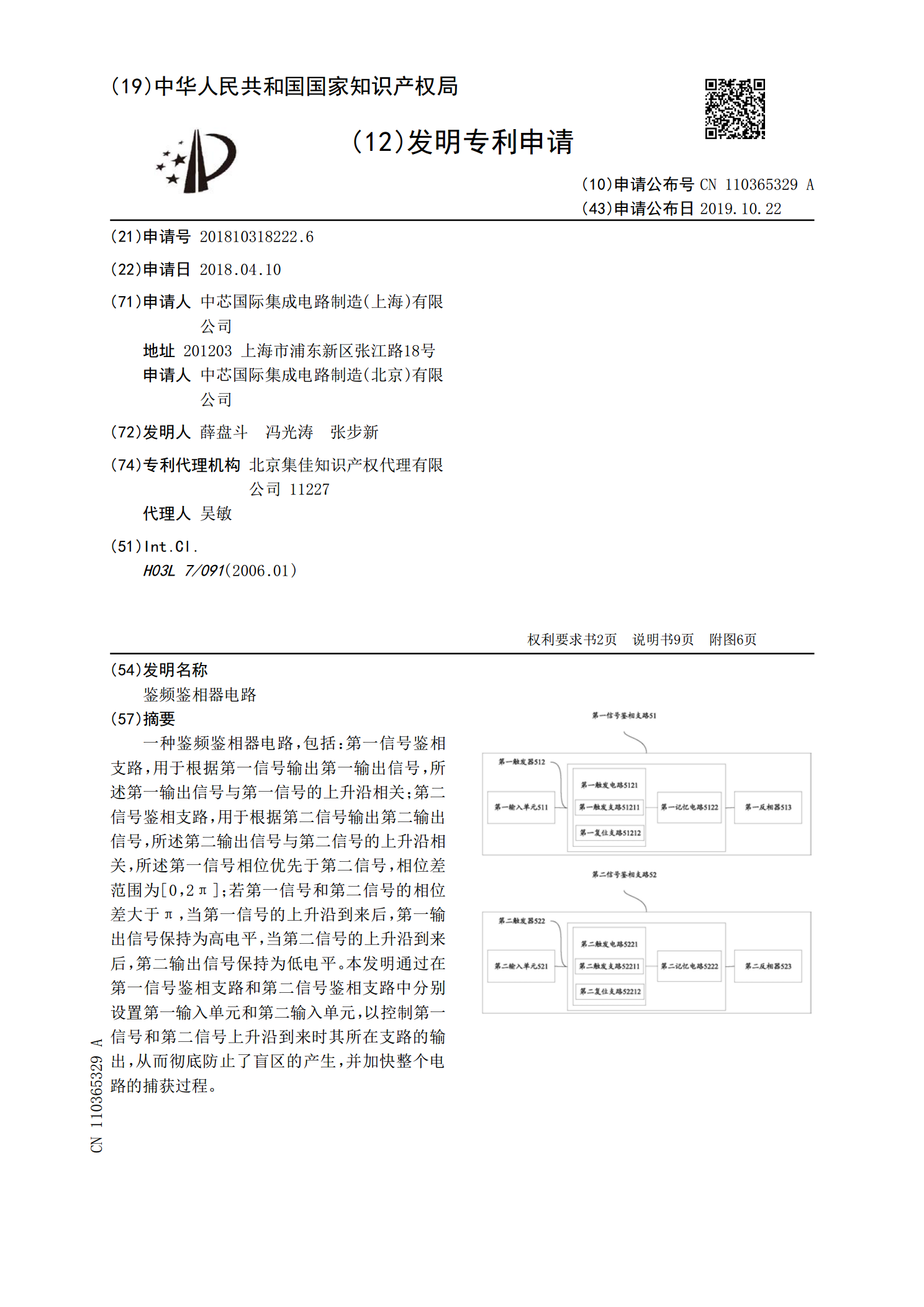

一种鉴频鉴相器电路,包括:第一信号鉴相支路,用于根据第一信号输出第一输出信号,所述第一输出信号与第一信号的上升沿相关;第二信号鉴相支路,用于根据第二信号输出第二输出信号,所述第二输出信号与第二信号的上升沿相关,所述第一信号相位优先于第二信号,相位差范围为[0,2π];若第一信号和第二信号的相位差大于π,当第一信号的上升沿到来后,第一输出信号保持为高电平,当第二信号的上升沿到来后,第二输出信号保持为低电平。本发明通过在第一信号鉴相支路和第二信号鉴相支路中分别设置第一输入单元和第二输入单元,以控制第一信号和第

CMOS锁相环中鉴频鉴相器的研究.docx

CMOS锁相环中鉴频鉴相器的研究CMOS锁相环中鉴频鉴相器的研究引言:随着现代通信系统对于低功耗、高性能的要求不断增加,锁相环(PLL)作为一种重要的时钟生成和信号处理技术得到广泛应用。而锁相环中的鉴频鉴相器是其关键组成部分,直接影响了锁相环的性能和稳定性。因此,对于CMOS锁相环中鉴频鉴相器的研究具有很大的意义。一、锁相环(PLL)的基本原理锁相环是一种基础的反馈控制系统,主要由相位比较器、带通滤波器、电压控制振荡器(VCO)和分频器组成。其工作原理是不断调整参考信号和VCO产生的信号之间的相位差,使其

D触发器原理-D触发器电路图.doc

边沿D触发器:负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。电路结构:该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。D触发器工作原理:SD和RD接至基本RS触发器的输入端,分别是预置和清零端,低电平有效。当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=

D触发器原理-D触发器电路图.doc

.实用文档.边沿D触发器:负跳沿触发的主从触发器工作时,在正跳沿前参加输入信号。如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP触发沿来到前一瞬间参加输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。电路结构:该触发器由6个与非门组成,其中G1和G2构成根本RS触发器。D触发器工作原理:SD和RD接至根本RS触发器的输入端,分别是预置和清零端,低电平有效。当SD=0且RD=1时,不管输入端D为何种状态