封装基板结构与其接合方法.pdf

Ch****91

亲,该文档总共34页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

封装基板结构与其接合方法.pdf

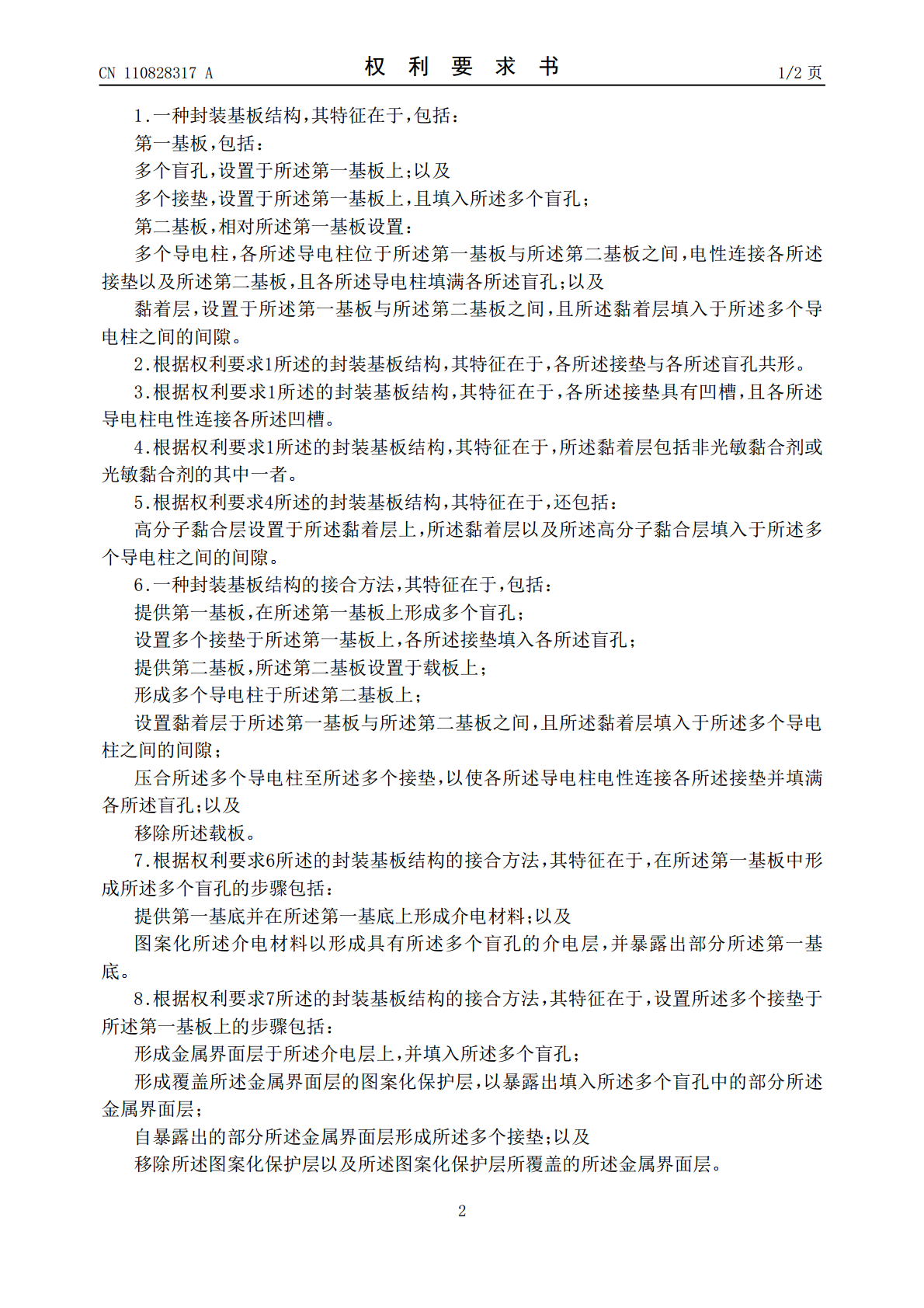

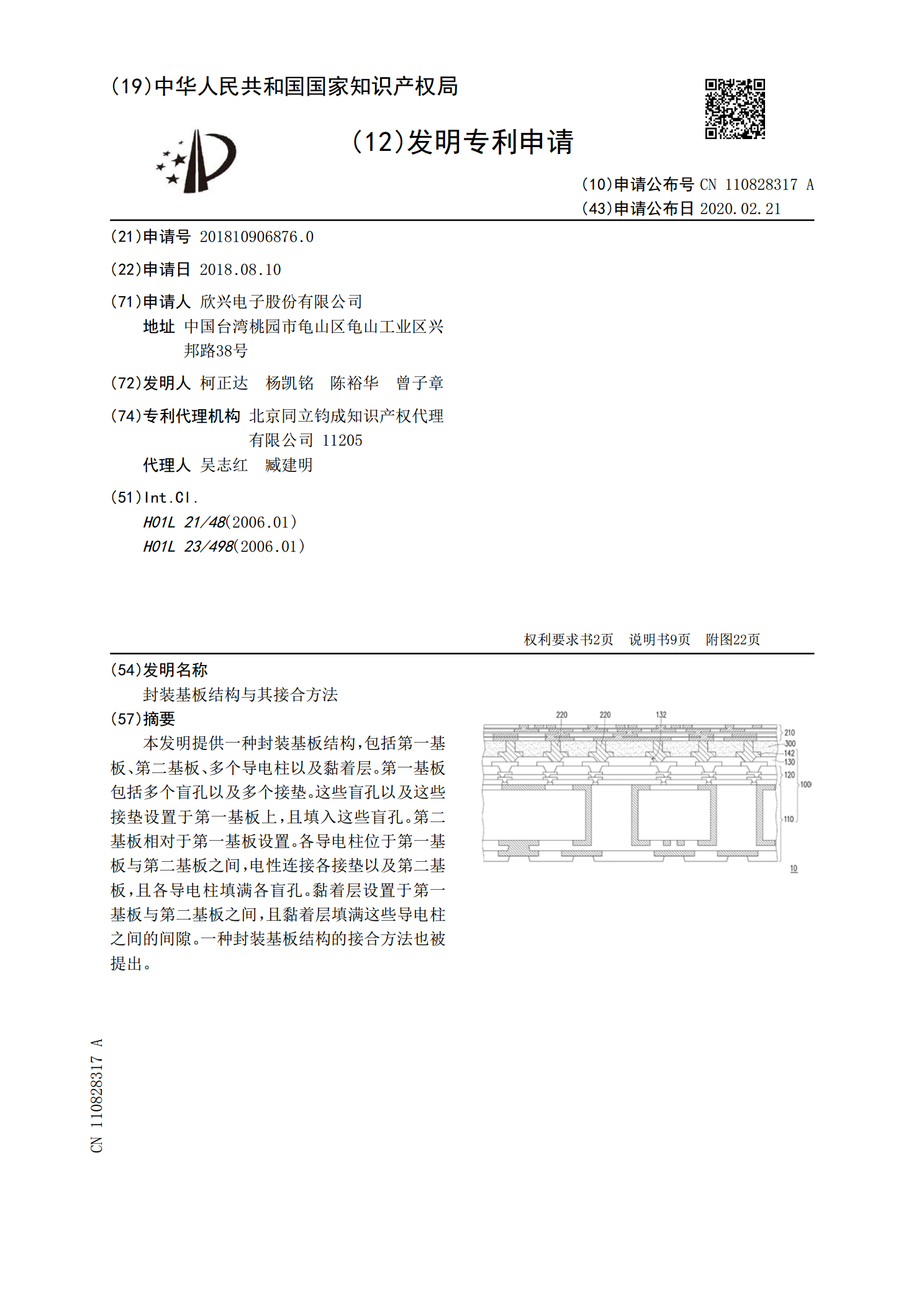

本发明提供一种封装基板结构,包括第一基板、第二基板、多个导电柱以及黏着层。第一基板包括多个盲孔以及多个接垫。这些盲孔以及这些接垫设置于第一基板上,且填入这些盲孔。第二基板相对于第一基板设置。各导电柱位于第一基板与第二基板之间,电性连接各接垫以及第二基板,且各导电柱填满各盲孔。黏着层设置于第一基板与第二基板之间,且黏着层填满这些导电柱之间的间隙。一种封装基板结构的接合方法也被提出。

封装结构与基板接合方法.pdf

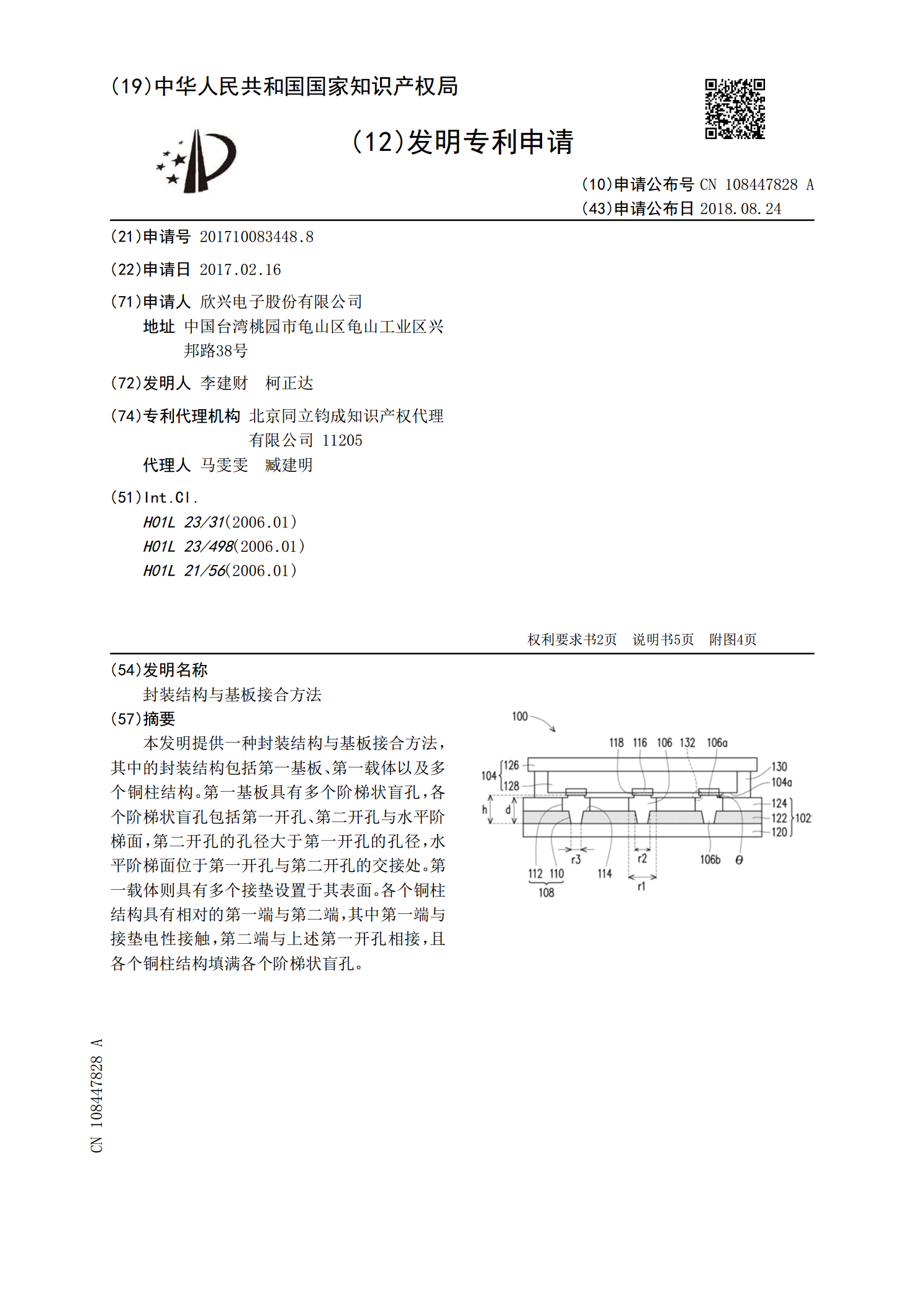

本发明提供一种封装结构与基板接合方法,其中的封装结构包括第一基板、第一载体以及多个铜柱结构。第一基板具有多个阶梯状盲孔,各个阶梯状盲孔包括第一开孔、第二开孔与水平阶梯面,第二开孔的孔径大于第一开孔的孔径,水平阶梯面位于第一开孔与第二开孔的交接处。第一载体则具有多个接垫设置于其表面。各个铜柱结构具有相对的第一端与第二端,其中第一端与接垫电性接触,第二端与上述第一开孔相接,且各个铜柱结构填满各个阶梯状盲孔。

封装基板与其制作方法.pdf

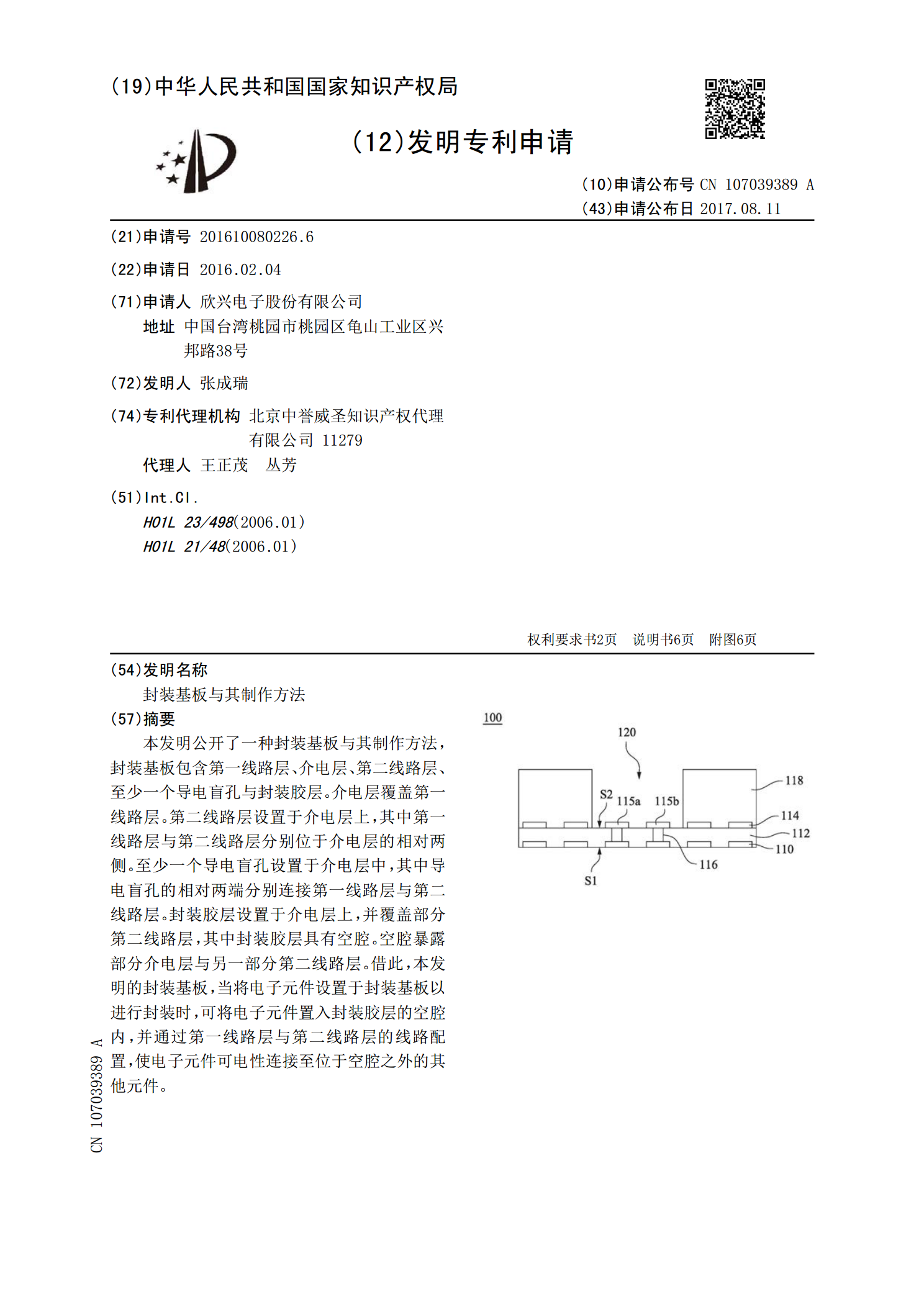

本发明公开了一种封装基板与其制作方法,封装基板包含第一线路层、介电层、第二线路层、至少一个导电盲孔与封装胶层。介电层覆盖第一线路层。第二线路层设置于介电层上,其中第一线路层与第二线路层分别位于介电层的相对两侧。至少一个导电盲孔设置于介电层中,其中导电盲孔的相对两端分别连接第一线路层与第二线路层。封装胶层设置于介电层上,并覆盖部分第二线路层,其中封装胶层具有空腔。空腔暴露部分介电层与另一部分第二线路层。借此,本发明的封装基板,当将电子元件设置于封装基板以进行封装时,可将电子元件置入封装胶层的空腔内,并通过第

基板、利用基板形成封装结构的方法和封装结构.pdf

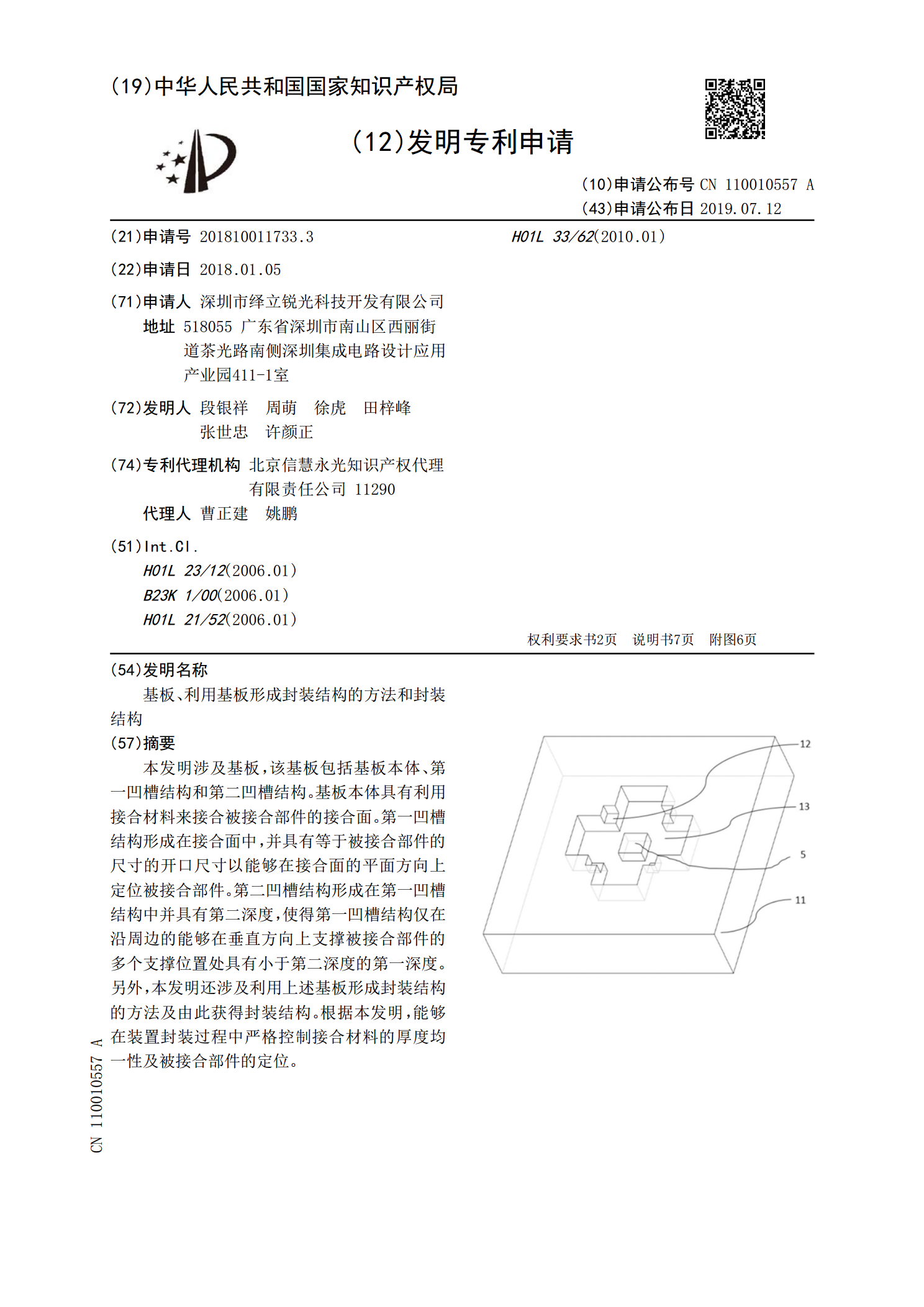

本发明涉及基板,该基板包括基板本体、第一凹槽结构和第二凹槽结构。基板本体具有利用接合材料来接合被接合部件的接合面。第一凹槽结构形成在接合面中,并具有等于被接合部件的尺寸的开口尺寸以能够在接合面的平面方向上定位被接合部件。第二凹槽结构形成在第一凹槽结构中并具有第二深度,使得第一凹槽结构仅在沿周边的能够在垂直方向上支撑被接合部件的多个支撑位置处具有小于第二深度的第一深度。另外,本发明还涉及利用上述基板形成封装结构的方法及由此获得封装结构。根据本发明,能够在装置封装过程中严格控制接合材料的厚度均一性及被接合部件

基板、利用基板形成封装结构的方法和封装结构.pdf

本发明涉及基板、利用基板形成封装结构的方法及封装结构,该基板包括基板本体、第一凹槽结构和第二凹槽结构。基板本体具有利用接合材料来接合被接合部件的接合面。第一凹槽结构形成在接合面中,并具有等于被接合部件的尺寸的开口尺寸以能够在接合面的平面方向上定位被接合部件。第二凹槽结构形成在第一凹槽结构中并具有第二深度,使得第一凹槽结构仅在沿周边的能够在垂直方向上支撑被接合部件的多个支撑位置处具有小于第二深度的第一深度。在第二凹槽结构的内部设置有用于传导来自被接合部件的热量的导热台,其顶表面至多与第一凹槽结构的底部齐平。