一种利用载板的芯片垂直集成封装结构及其制备方法.pdf

安双****文章

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种利用载板的芯片垂直集成封装结构及其制备方法.pdf

本发明公开了一种利用载板的芯片垂直集成封装结构及其制备方法,涉及集成电路三维封装技术领域,具体步骤为:在第一芯片的焊盘上制备铜柱凸点,在第二芯片的焊盘上制备锡凸点;基于第二芯片将载板任一表面的导电金属层露出;基于第一芯片在载板另一表面采用激光钻孔方法将载板内金属层露出,形成第一导电盲孔;分别将第一芯片和第二芯片按照不同的方法设置于载板的两侧,完成封装模块的制备;本发明通过载板实现对多种尺寸、不同功能芯片高度集成的可靠封装。

一种芯片封装结构及其制备方法.pdf

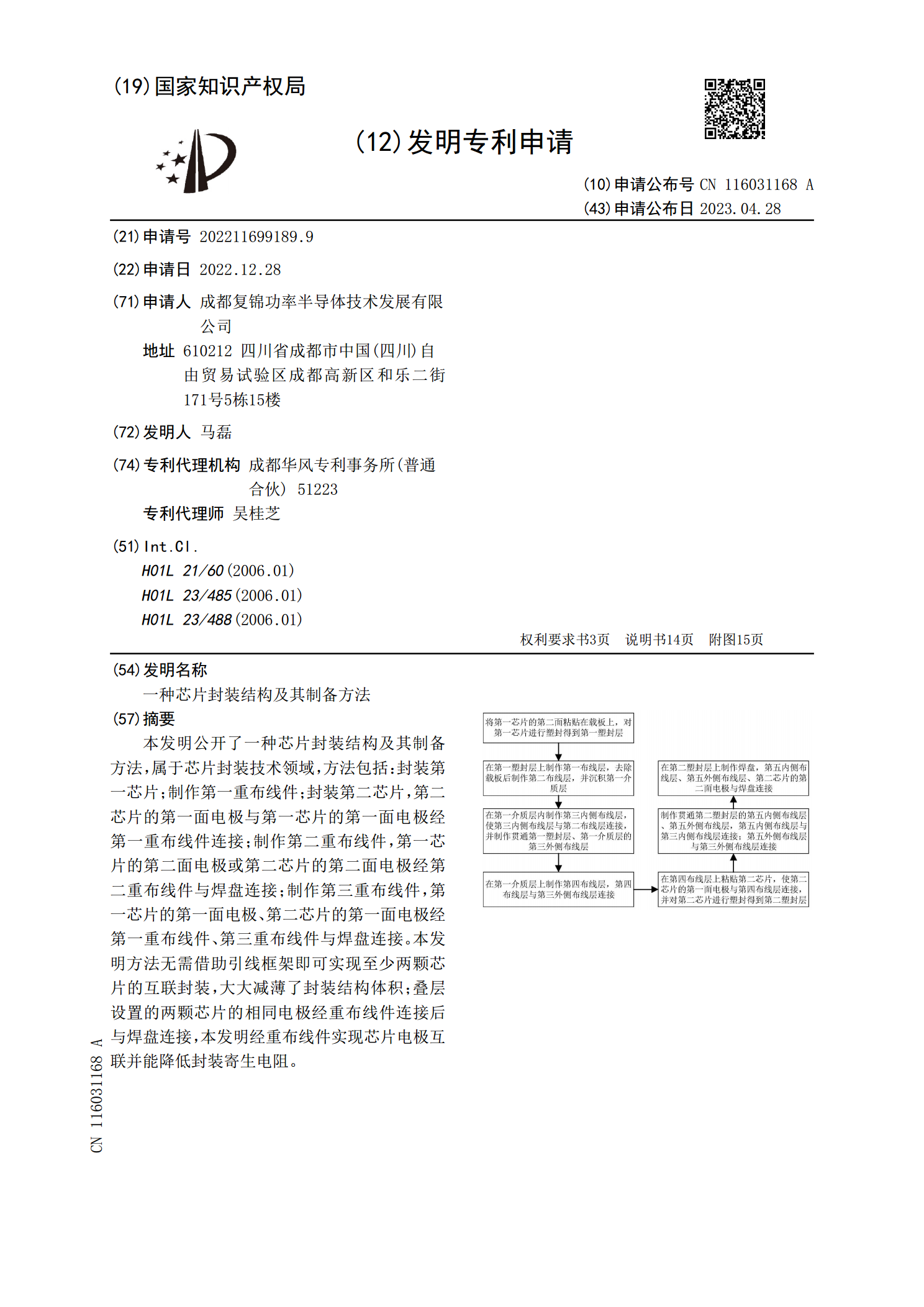

本发明公开了一种芯片封装结构及其制备方法,属于芯片封装技术领域,方法包括:封装第一芯片;制作第一重布线件;封装第二芯片,第二芯片的第一面电极与第一芯片的第一面电极经第一重布线件连接;制作第二重布线件,第一芯片的第二面电极或第二芯片的第二面电极经第二重布线件与焊盘连接;制作第三重布线件,第一芯片的第一面电极、第二芯片的第一面电极经第一重布线件、第三重布线件与焊盘连接。本发明方法无需借助引线框架即可实现至少两颗芯片的互联封装,大大减薄了封装结构体积;叠层设置的两颗芯片的相同电极经重布线件连接后与焊盘连接,本发

一种芯片的封装结构及其制备方法.pdf

本发明提供一种芯片的封装结构及其制备方法,方法包括:提供承载片;在所述承载片沿其厚度方向的第一表面形成金属盲孔;在所述承载片的所述第一表面形成第一钝化层,图形化所述第一钝化层以形成过孔;在所述图形化后的第一钝化层上形成金属凸块,所述金属凸块通过所述过孔与所述金属盲孔电连接,以制备得到封装结构。本发明通过在承载片上设计出金属盲孔、第一钝化层和金属凸块,金属凸块通过设置在第一钝化层上的过孔与金属盲孔电连接,可以使金属盲孔的厚度超过20μm,金属盲孔的厚度范围可以达到30μm~100μm,降低了对钝化层厚度的要

一种芯片封装结构及其制备方法.pdf

本发明公开了一种芯片封装结构及其制备方法,涉及芯片封装技术领域,其中,所述芯片封装结构包括:第一芯片,第一芯片的有源面设置有粘结层,所述粘结层对应第一芯片的焊盘设置有粘结层盲孔,第一芯片非有源面的其他侧面有包覆材料包封,介质层,设置在粘结层上方,介质层上设置有与粘结层盲孔对应设置的介质层盲孔,粘结层盲孔和介质层盲孔中填充有导电材料,第一重布线层,与粘结层盲孔和介质层盲孔中填充的导电材料电连接,焊球,与第一重布线层电连接。采用上述技术方案,第一芯片与第一重布线层通过介质层盲孔和粘结层盲孔中的导电材料电连接,

一种芯片封装结构及其制备方法.pdf

本发明公开了一种芯片封装结构及其制备方法,制备方法包括:提供一载板,在载板的上下表面制备双层剥离结构,在双层剥离结构上远离载板的一侧制备重布线层,在重布线层以及双层剥离结构表面制备第一介质层,在第一介质层中制备至少一个盲孔,在盲孔内填充导电材料,提供一芯片,将芯片倒装在第一介质层上,在芯片周围制备第二介质层,第二介质层覆盖第一介质层且包覆芯片,将双层剥离结构进行剥离,刻蚀双层剥离结构的上层结构,露出重布线层和第一介质层,在重布线层上远离第一介质层的一侧制备焊球,焊球与重布线层电连接。综上,制备方法简单、操