线路制作方法及其线路板.pdf

一吃****仕龙

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

线路制作方法及其线路板.pdf

本发明公开了一种线路制作方法及其线路板,其中线路制作方法包括以下步骤:制作内层芯板后,在所述芯板上压合介质层;在所述介质层上钻出导通的盲孔;在所述介质层上和所述盲孔上溅镀上钛结合层,在所述钛结合层上溅镀上铜种子层;在所述铜种子层上贴上耐电镀干膜;将线路图形转移至所述耐电镀干膜上,并显露需要进行电镀的所述线路图形和所述盲孔;电镀填满所述盲孔并加厚所述线路图形;去除所述耐电镀干膜,显露所述铜种子层;依次蚀刻所述铜种子层和所述钛结合层,以形成所述线路。利用铜种子层进行蚀刻,减少了蚀刻的时间,能够有效降低电镀的线

线路板及其制作方法.pdf

本发明提出一种线路板的制作方法,包括:提供第一主体,第一主体包括第一堆叠结构及设置于第一堆叠结构相背表面的第一导电层及第二导电层;在第一主体上开设盲孔,盲孔贯穿第一堆叠结构及第一导电层;在盲孔内壁设置第三导电层以形成导电孔;蚀刻第一导电层得到第一导电线路,蚀刻第二导电层得到第二导电线路;在导电孔中填充锡膏;去除第二导电线路及第三导电层的部分形成贯穿第一主体的导电通孔,使锡膏靠近第二导电线路一侧的部分暴露;提供第二主体,第二主体包括多个焊接间隙,使第一主体与第二主体堆叠,使导电通孔与焊接间隙连通;通过光照加

线路板及其制作方法.pdf

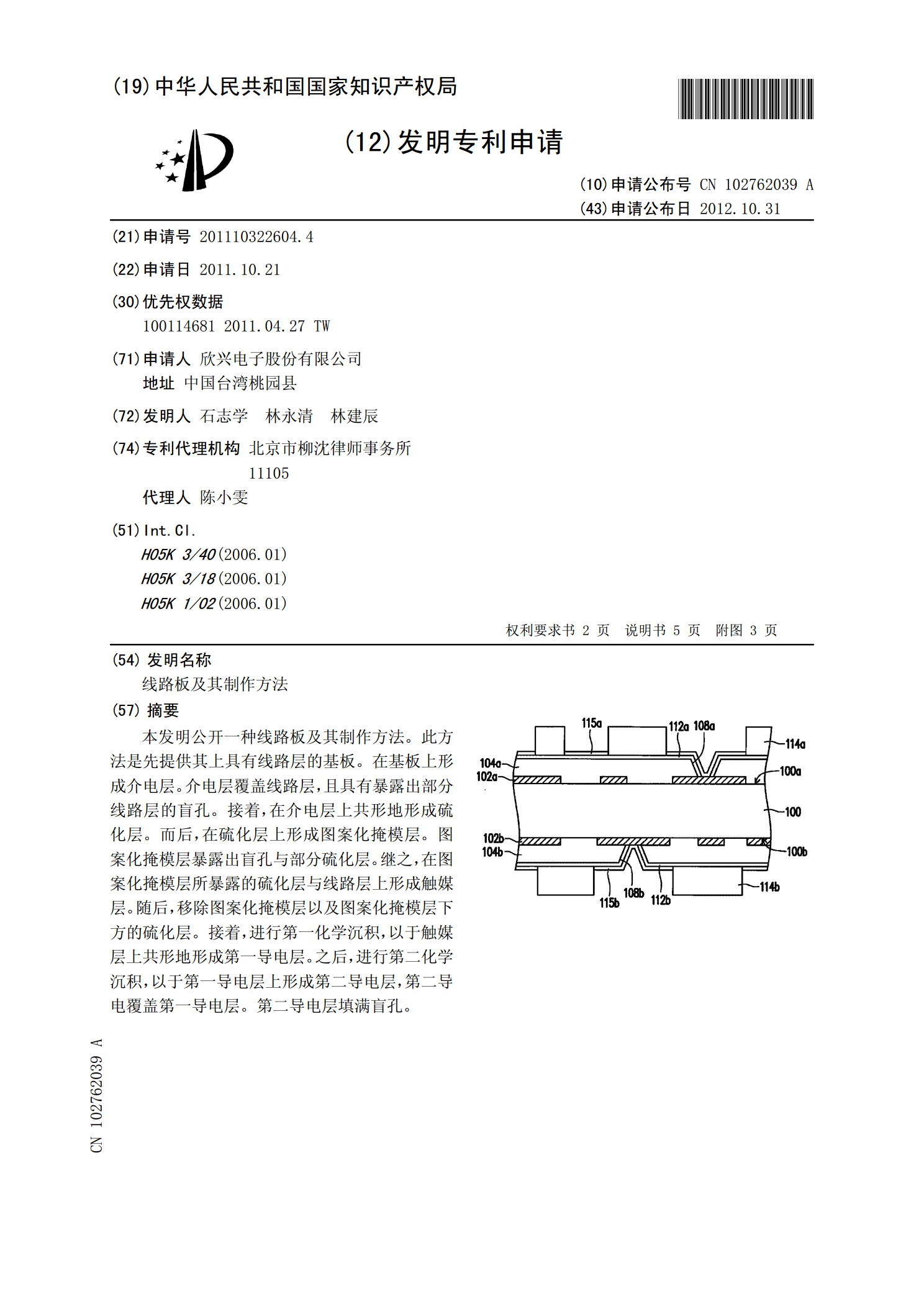

本发明公开一种线路板及其制作方法。此方法是先提供其上具有线路层的基板。在基板上形成介电层。介电层覆盖线路层,且具有暴露出部分线路层的盲孔。接着,在介电层上共形地形成硫化层。而后,在硫化层上形成图案化掩模层。图案化掩模层暴露出盲孔与部分硫化层。继之,在图案化掩模层所暴露的硫化层与线路层上形成触媒层。随后,移除图案化掩模层以及图案化掩模层下方的硫化层。接着,进行第一化学沉积,以于触媒层上共形地形成第一导电层。之后,进行第二化学沉积,以于第一导电层上形成第二导电层,第二导电覆盖第一导电层。第二导电层填满盲孔。

线路板及其制作方法.pdf

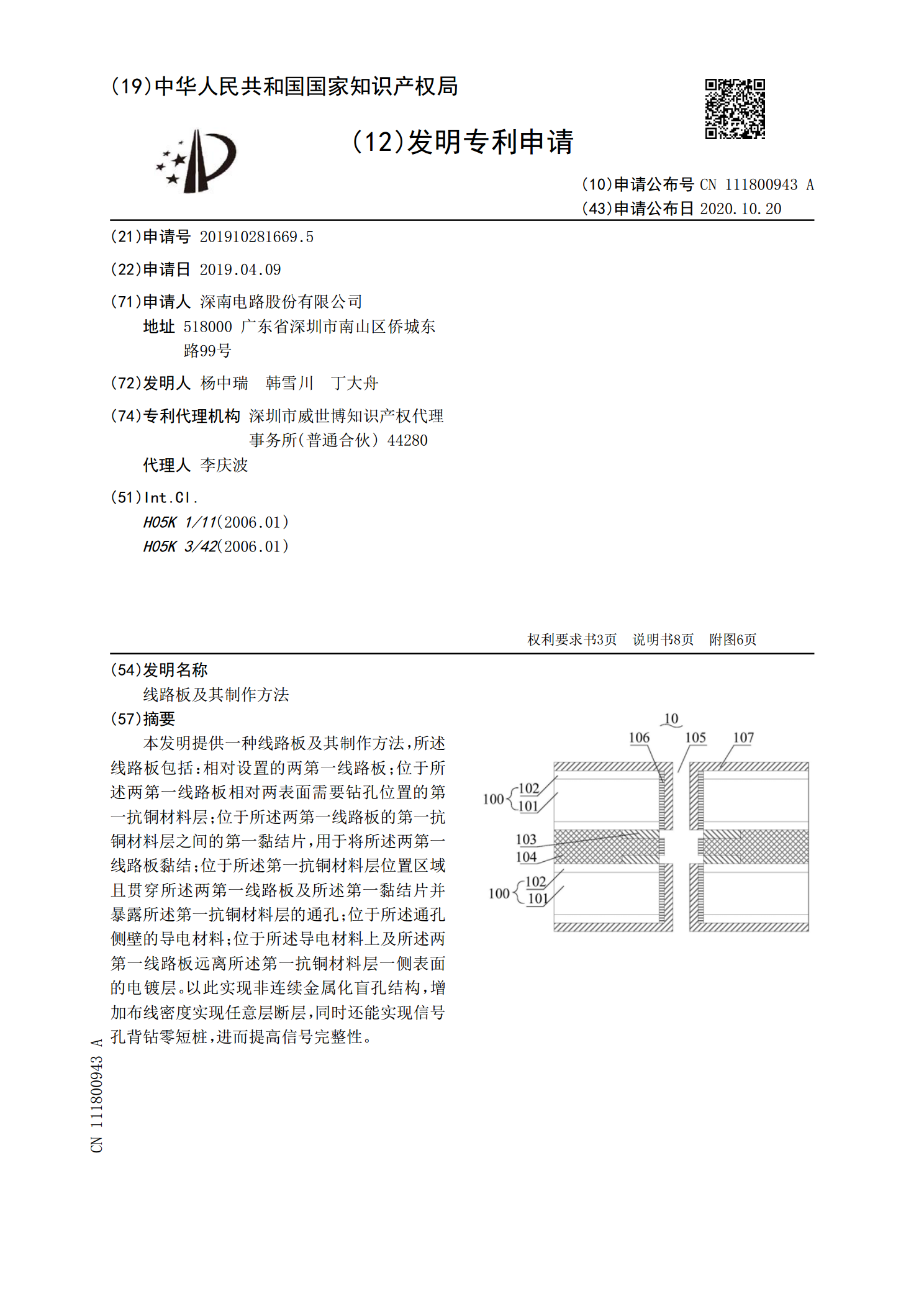

本发明提供一种线路板及其制作方法,所述线路板包括:相对设置的两第一线路板;位于所述两第一线路板相对两表面需要钻孔位置的第一抗铜材料层;位于所述两第一线路板的第一抗铜材料层之间的第一黏结片,用于将所述两第一线路板黏结;位于所述第一抗铜材料层位置区域且贯穿所述两第一线路板及所述第一黏结片并暴露所述第一抗铜材料层的通孔;位于所述通孔侧壁的导电材料;位于所述导电材料上及所述两第一线路板远离所述第一抗铜材料层一侧表面的电镀层。以此实现非连续金属化盲孔结构,增加布线密度实现任意层断层,同时还能实现信号孔背钻零短桩,进

线路板结构及其制作方法.pdf

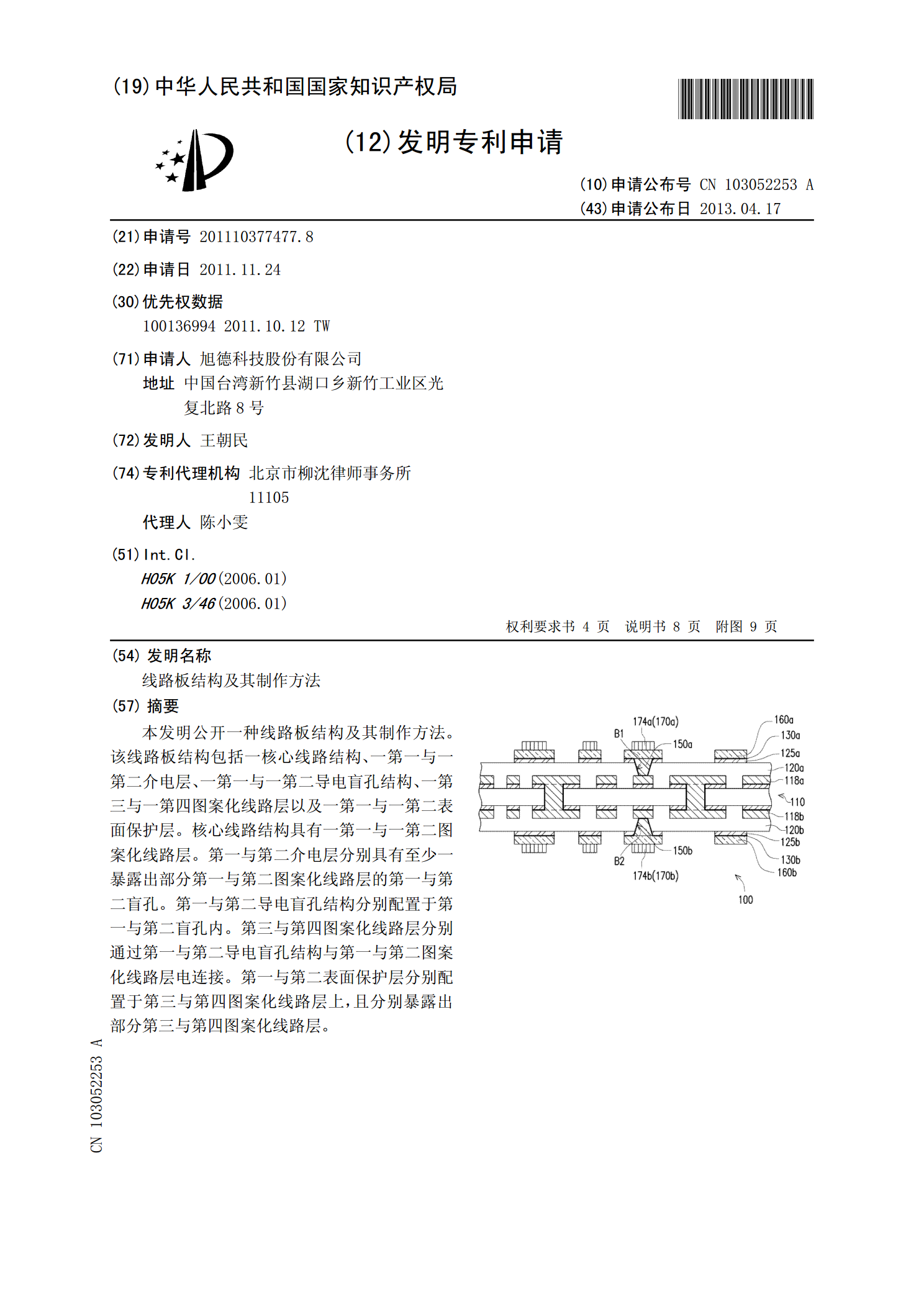

本发明公开一种线路板结构及其制作方法。该线路板结构包括一核心线路结构、一第一与一第二介电层、一第一与一第二导电盲孔结构、一第三与一第四图案化线路层以及一第一与一第二表面保护层。核心线路结构具有一第一与一第二图案化线路层。第一与第二介电层分别具有至少一暴露出部分第一与第二图案化线路层的第一与第二盲孔。第一与第二导电盲孔结构分别配置于第一与第二盲孔内。第三与第四图案化线路层分别通过第一与第二导电盲孔结构与第一与第二图案化线路层电连接。第一与第二表面保护层分别配置于第三与第四图案化线路层上,且分别暴露出部分第三