正型感光性树脂组合物.pdf

曦晨****22

1/10

2/10

3/10

4/10

5/10

6/10

7/10

8/10

9/10

10/10

亲,该文档总共25页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

正型感光性树脂组合物.pdf

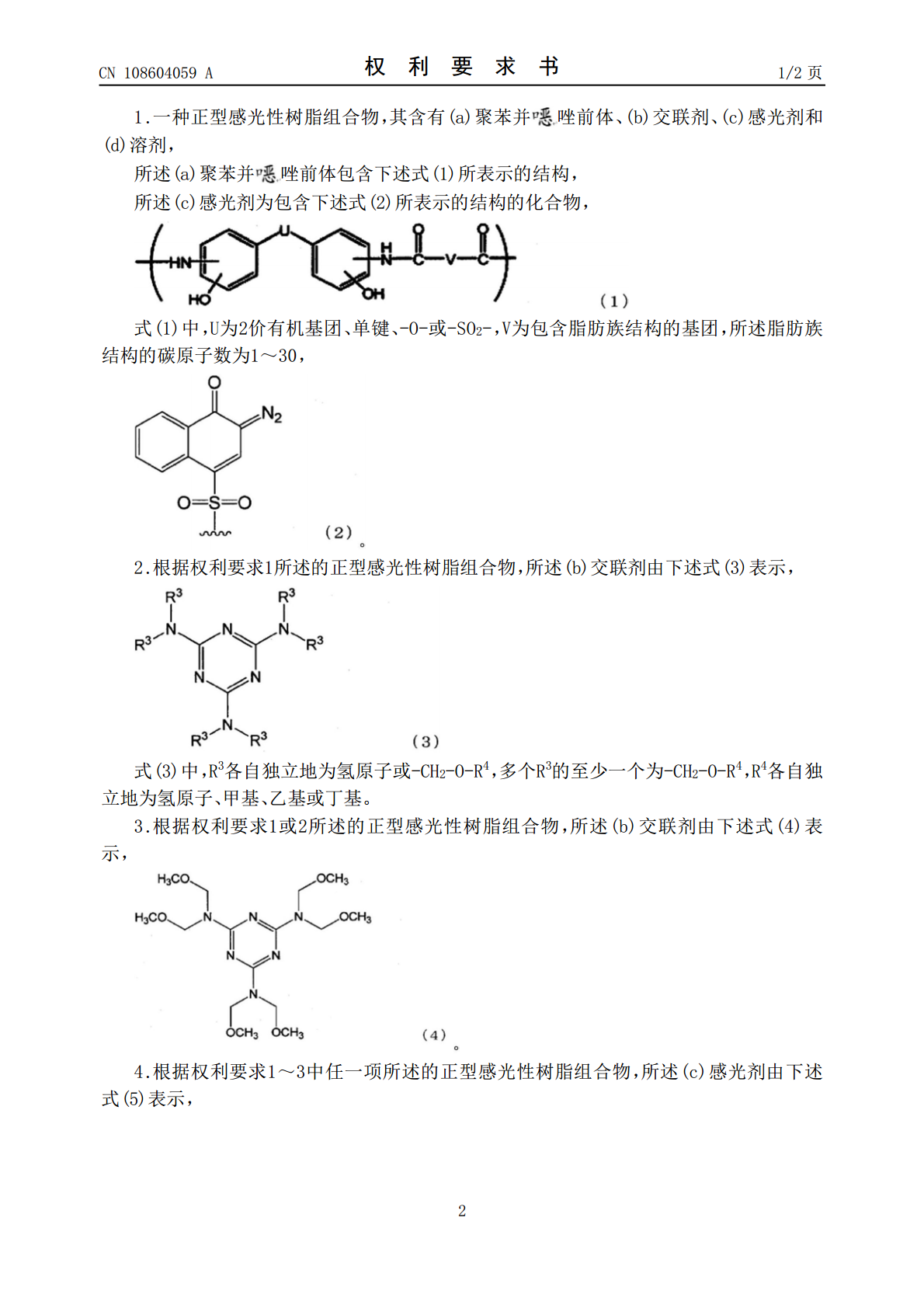

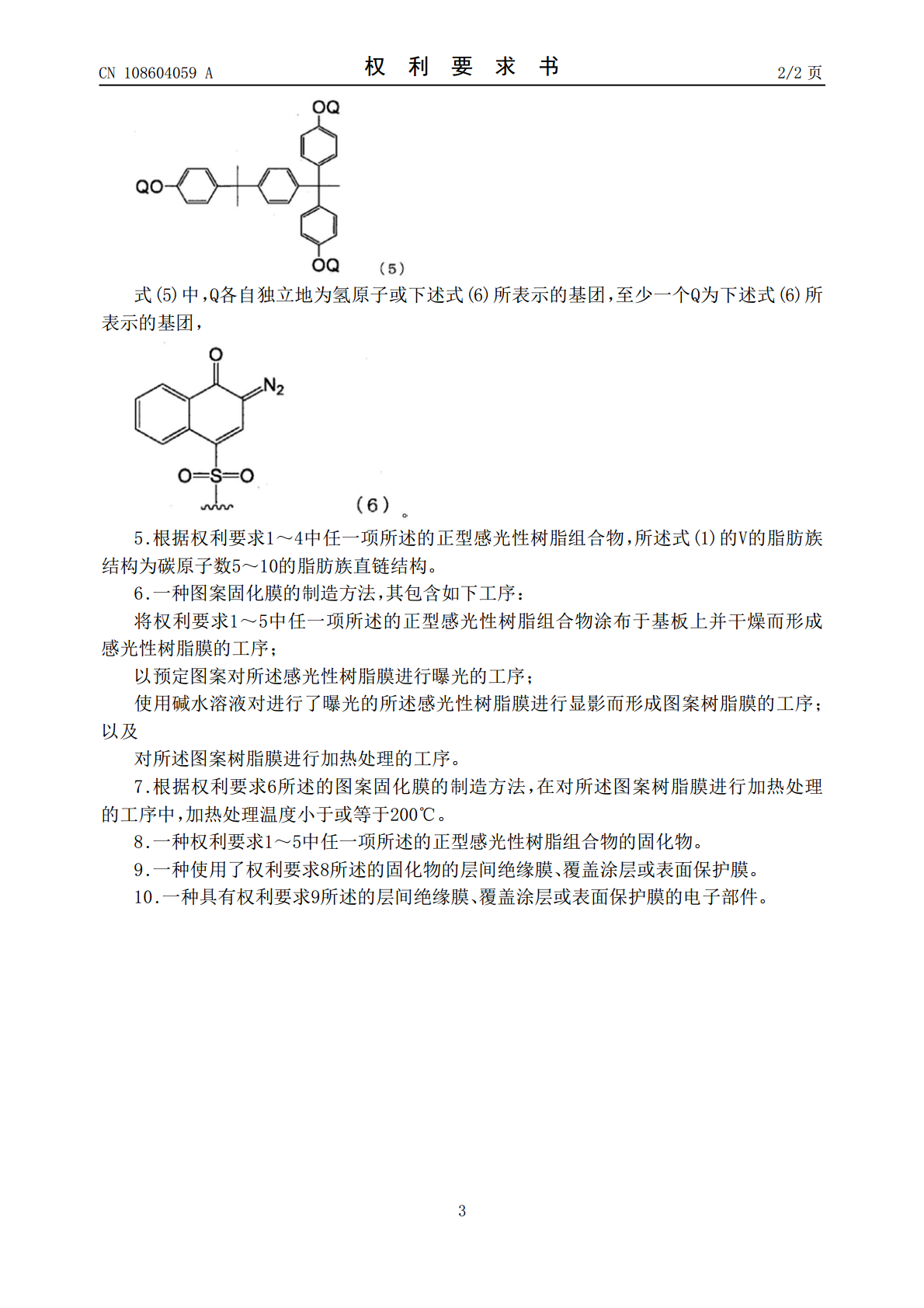

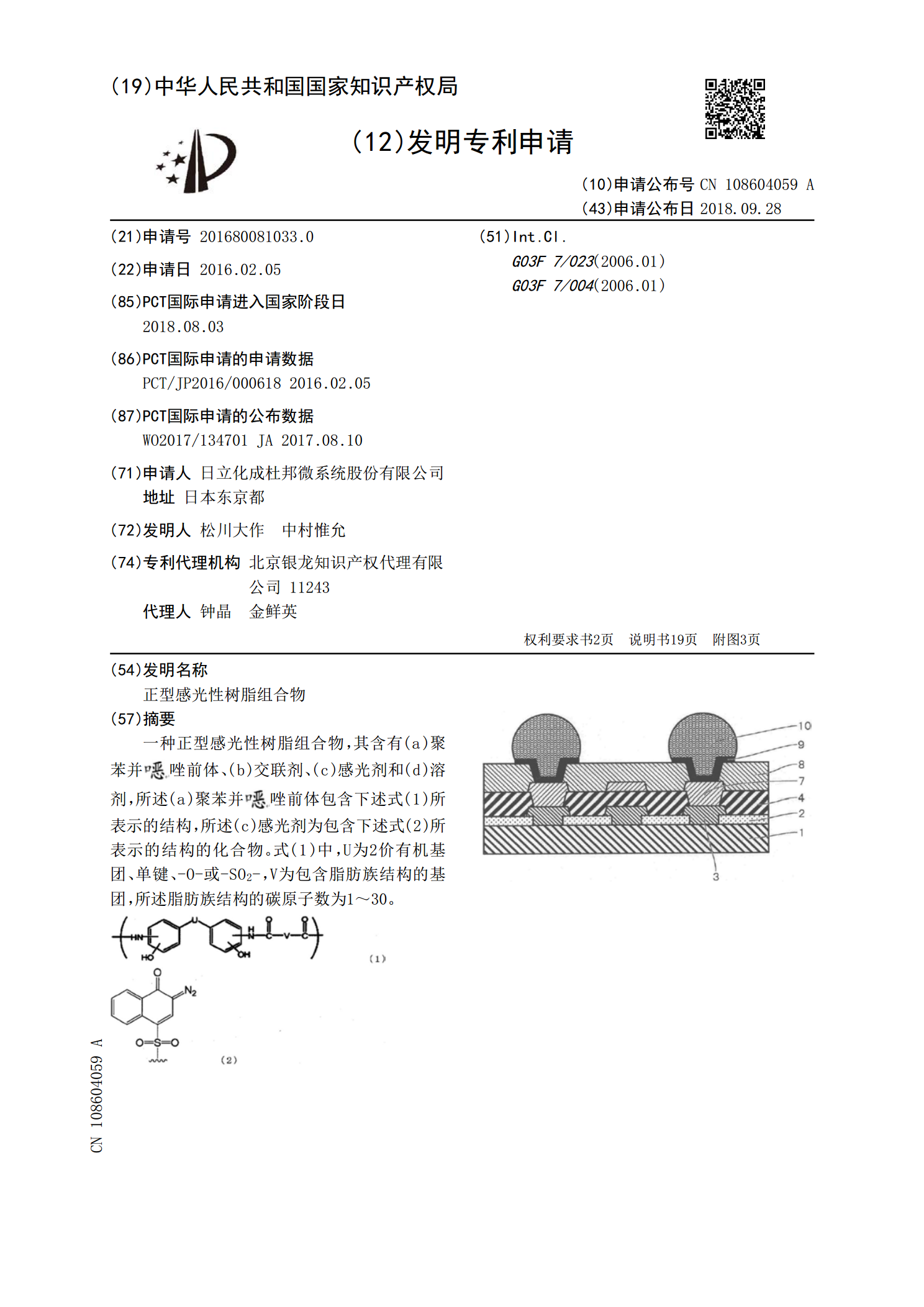

一种正型感光性树脂组合物,其含有(a)聚苯并

正型感光性树脂组合物.pdf

一种正型感光性树脂组合物,其含有(a)聚苯并

正型感光性树脂组合物.pdf

本发明涉及一种正型感光性树脂组合物,含有碱溶性树脂(A)、感光剂(B)、交联剂(C)、表面活性剂(D),上述交联剂(C)含有具有选自羧基、酚性羟基、磺基和磷酸基中的1种以上作为酸性基团的化合物,具有上述酸性基团的化合物的比例以质量比计相对于(A)+(B)+(C)+(D)的合计在5~35%的范围,上述表面活性剂(D)不具有F原子。

正型感光性树脂组合物.pdf

本发明涉及正型感光性树脂组合物,含有碱溶性树脂(A)、感光剂(B)、交联剂(C)、拒油墨剂(D),上述交联剂(C)含有具有选自羧基、酚性羟基、磺基和磷酸基中的1种以上作为酸性基团的化合物,具有上述酸性基团的化合物的比例以质量比计相对于(A)+(B)+(C)+(D)的合计在5~35%的范围,上述拒油墨剂(D)含有具有F原子的丙烯酸化合物和具有F原子的有机硅化合物中的至少一方。

正型感光性树脂组合物.pdf

本发明涉及一种正型感光性树脂组合物,含有碱溶性树脂(A)、感光剂(B)、交联剂(C)、表面活性剂(D),上述交联剂(C)含有具有选自羧基、酚性羟基、磺基和磷酸基中的1种以上作为酸性基团的化合物,具有上述酸性基团的化合物的比例以质量比计相对于(A)+(B)+(C)+(D)的合计在5~35%的范围,上述表面活性剂(D)不具有F原子。