薄膜沉积方法和半导体器件.pdf

秋花****姐姐

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

薄膜沉积方法和半导体器件.pdf

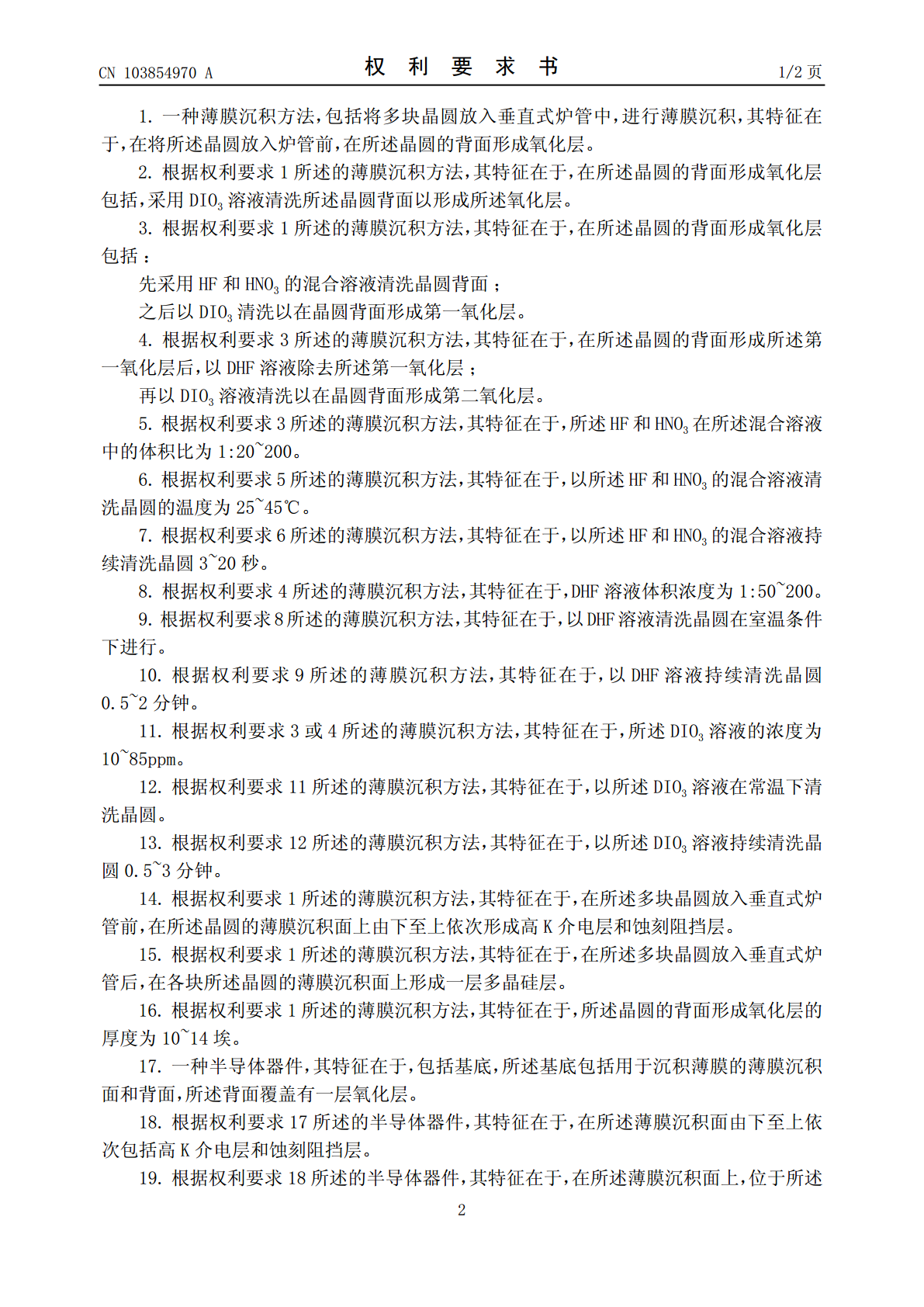

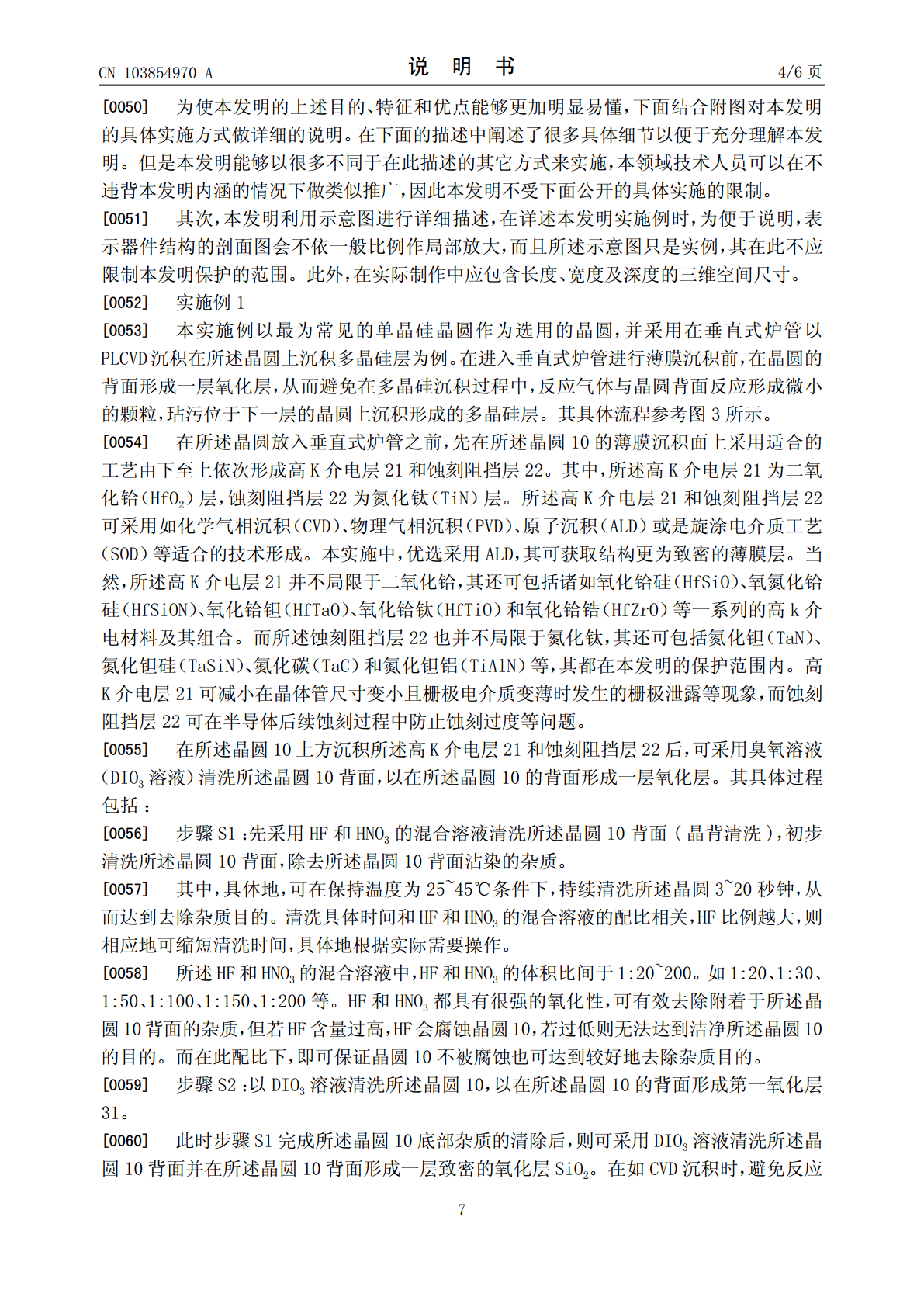

本发明公开了一种薄膜沉积方法和半导体器件。所述薄膜沉积方法中,在将多块的晶圆放入垂直式炉管之前,在所述晶圆的背面形成一层氧化层,从而在薄膜沉积过程中,避免在晶圆的背面形成细小颗粒,并脱落后掉落在下一层晶圆的薄膜沉积面上,并由此对下一层晶圆上沉积的薄膜层造成污染,降低了晶圆上形成的薄膜质量。

半导体薄膜的沉积设备和沉积方法.pdf

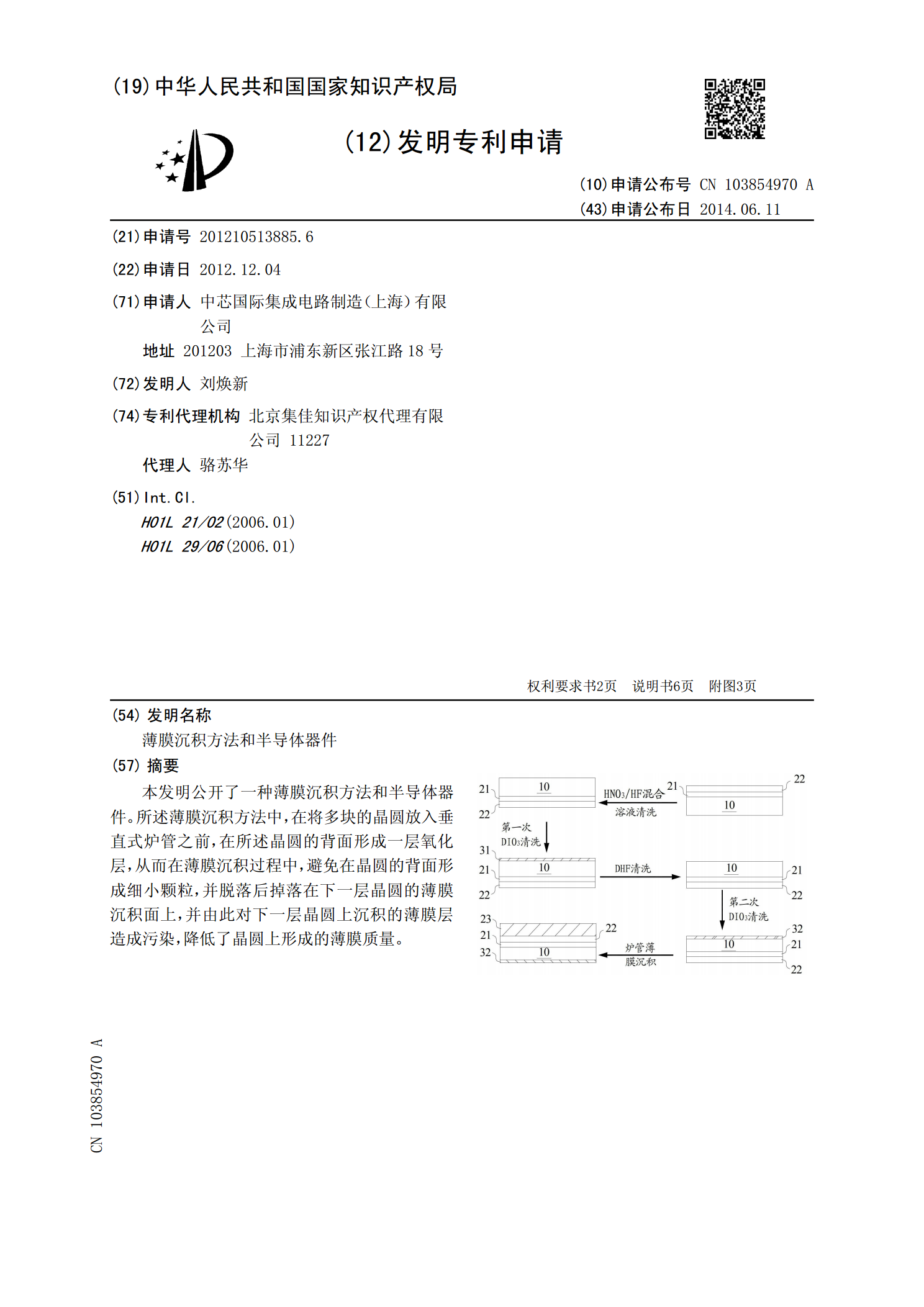

本发明是关于一种半导体薄膜的沉积设备和沉积方法,包括腔体和盖板,加热盘,加热盘通过支撑杆支撑,还包括:晶圆升降机构设置于腔体内;水平调节机构设置于腔体外;晶圆升降机构包括:同心定位盘设置于腔体内,位于加热盘的下方;同心调整手,通过板簧设置于同心定位盘的边缘上,与同心定位盘活动连接,同心调整手包括平行设置的第一横板第二横板和竖板;顶针支板,设置于加热盘和第二横板之间,均匀设有多个顶针;蓝宝石玻璃,设置于顶针支板的下方;动力单元,通过支杆与顶针支板连接,支杆贯穿腔体。保证晶圆与加热盘和喷淋板的同心设置,以及三

薄膜半导体器件以及薄膜半导体器件的制造方法.pdf

薄膜半导体器件(100)具备:栅电极(120)、沟道层(140)、第1非晶半导体层(150)、沟道保护层(160)、在沟道层(140)的两侧面形成的一对第2非晶半导体层(171、172)、和经由第2非晶半导体层(171、172)与沟道层(140)的侧面接触的一对接触层(181、182),栅电极(120)、沟道层(140)、第1非晶半导体层(150)以及沟道保护层(160)层叠成俯视时外形轮廓线一致,第1非晶半导体层(150)的局部能级密度比第2非晶半导体层(171、172)的局部能级密度高,第2非晶半导体

薄膜沉积设备及半导体工艺方法.pdf

本发明提供一种薄膜沉积设备及半导体工艺方法。薄膜沉积设备包括沉积炉管、晶圆装载区及晶圆传送装置;沉积炉管用于对晶圆进行薄膜沉积工艺;晶圆装置区设置有称量装置,称量装置用于承载放置有晶圆的晶圆盒并获得晶圆的重量;晶圆传送装置位于沉积炉管及晶圆装载区之间,用于在沉积炉管和晶圆装载区的晶圆盒之间传送晶圆。采用本发明的薄膜沉积设备可以及时掌握设备故障时晶圆所处的位置,从而为工作人员的排障作业提供参考,有助于降低晶圆被污染的风险。同时,本申请通过比较晶圆在薄膜沉积工艺前后的重量差以判断晶圆沉积的薄膜是否符合要求,相

一种薄膜沉积方法和沉积薄膜.pdf

本发明提供了一种薄膜沉积方法,包括:载入承载有晶圆的晶舟至低压化学气相沉积炉内;预先加热晶圆,对低压化学气相沉积炉进行第一升温操作,在预热升温斜率下达到第一反应温度;形成薄膜于晶圆上,包含在低压化学气相沉积炉内导入反应气体、进行化学反应并沉积在晶圆的基板表面,在沉积过程时,对低压化学气相沉积炉内的温度进行在緩升/降温斜率下至少一段的緩升/降温反应操作,以使薄膜在晶圆上的中央区域与周边区域具有一致的沉积厚度;及在冷却降温斜率下冷却晶圆。本发明通过控制沉积过程中缓升/降温斜率,可改变晶圆从中央区域到周边区域的