一种半导体结构及其制造方法.pdf

雨巷****珺琦

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种半导体结构及其制造方法.pdf

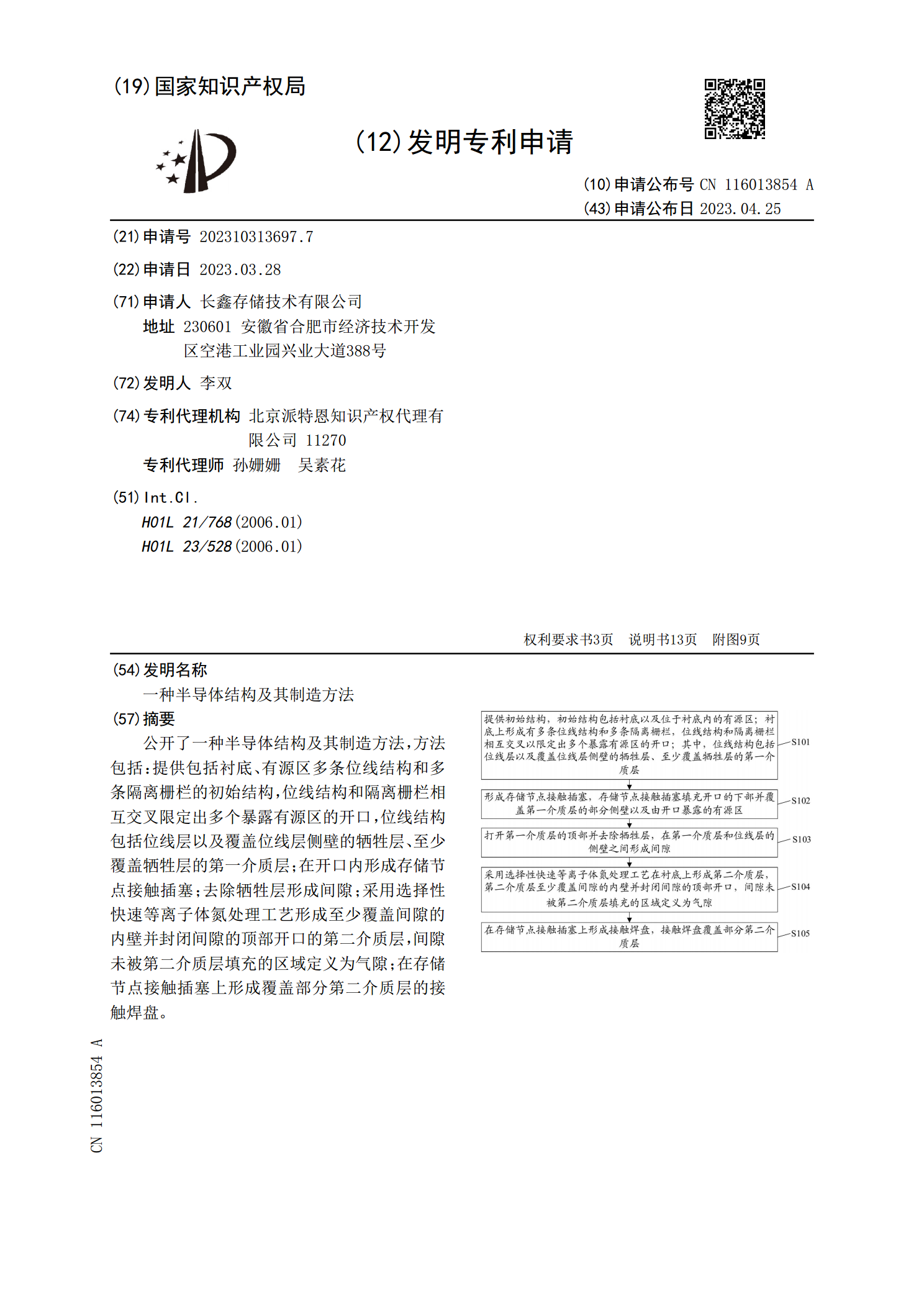

公开了一种半导体结构及其制造方法,方法包括:提供包括衬底、有源区多条位线结构和多条隔离栅栏的初始结构,位线结构和隔离栅栏相互交叉限定出多个暴露有源区的开口,位线结构包括位线层以及覆盖位线层侧壁的牺牲层、至少覆盖牺牲层的第一介质层;在开口内形成存储节点接触插塞;去除牺牲层形成间隙;采用选择性快速等离子体氮处理工艺形成至少覆盖间隙的内壁并封闭间隙的顶部开口的第二介质层,间隙未被第二介质层填充的区域定义为气隙;在存储节点接触插塞上形成覆盖部分第二介质层的接触焊盘。

一种半导体结构及其制造方法.pdf

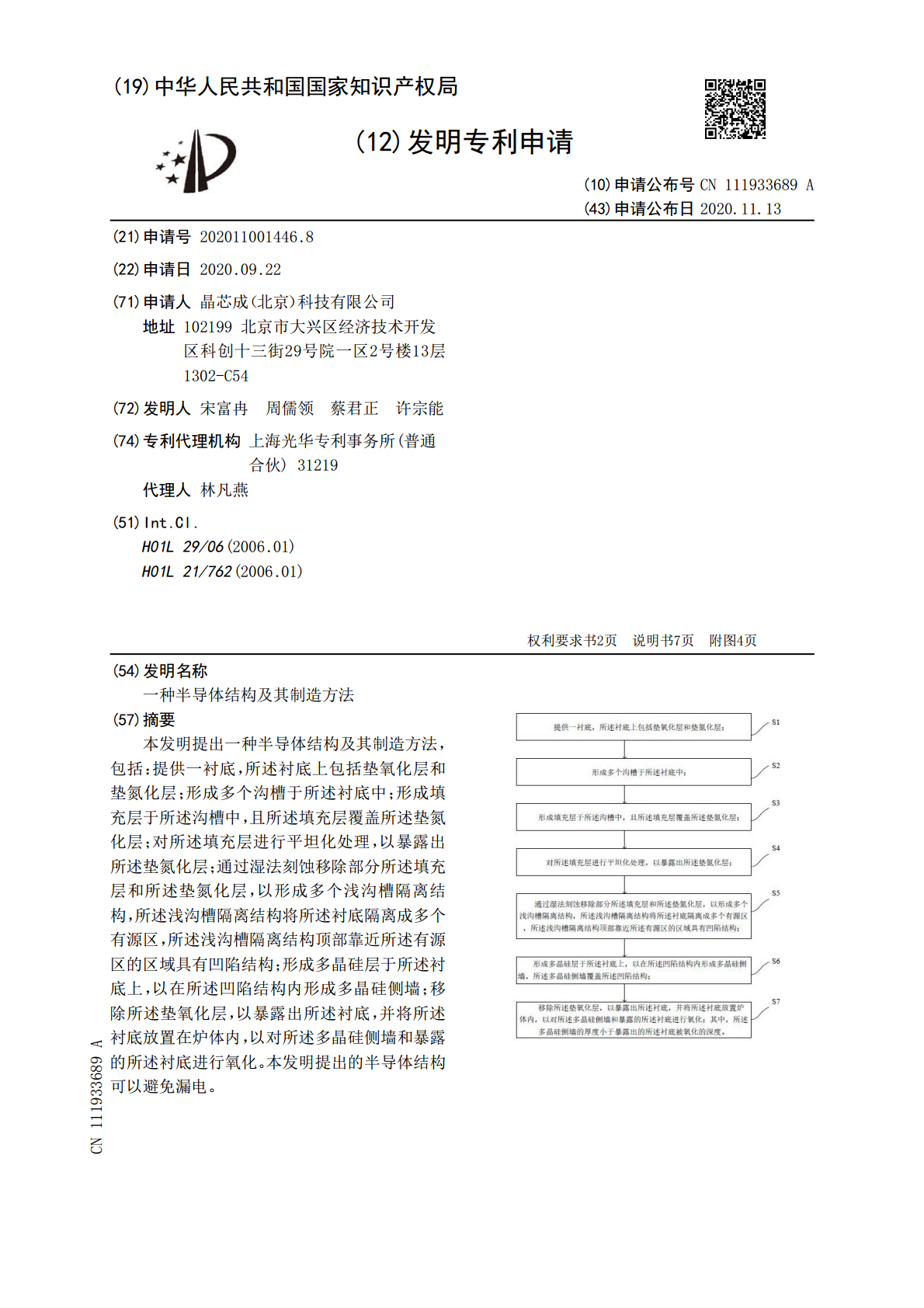

本发明提出一种半导体结构及其制造方法,包括:提供一衬底,所述衬底上包括垫氧化层和垫氮化层;形成多个沟槽于所述衬底中;形成填充层于所述沟槽中,且所述填充层覆盖所述垫氮化层;对所述填充层进行平坦化处理,以暴露出所述垫氮化层;通过湿法刻蚀移除部分所述填充层和所述垫氮化层,以形成多个浅沟槽隔离结构,所述浅沟槽隔离结构将所述衬底隔离成多个有源区,所述浅沟槽隔离结构顶部靠近所述有源区的区域具有凹陷结构;形成多晶硅层于所述衬底上,以在所述凹陷结构内形成多晶硅侧墙;移除所述垫氧化层,以暴露出所述衬底,并将所述衬底放置在炉

一种半导体结构及其制造方法.pdf

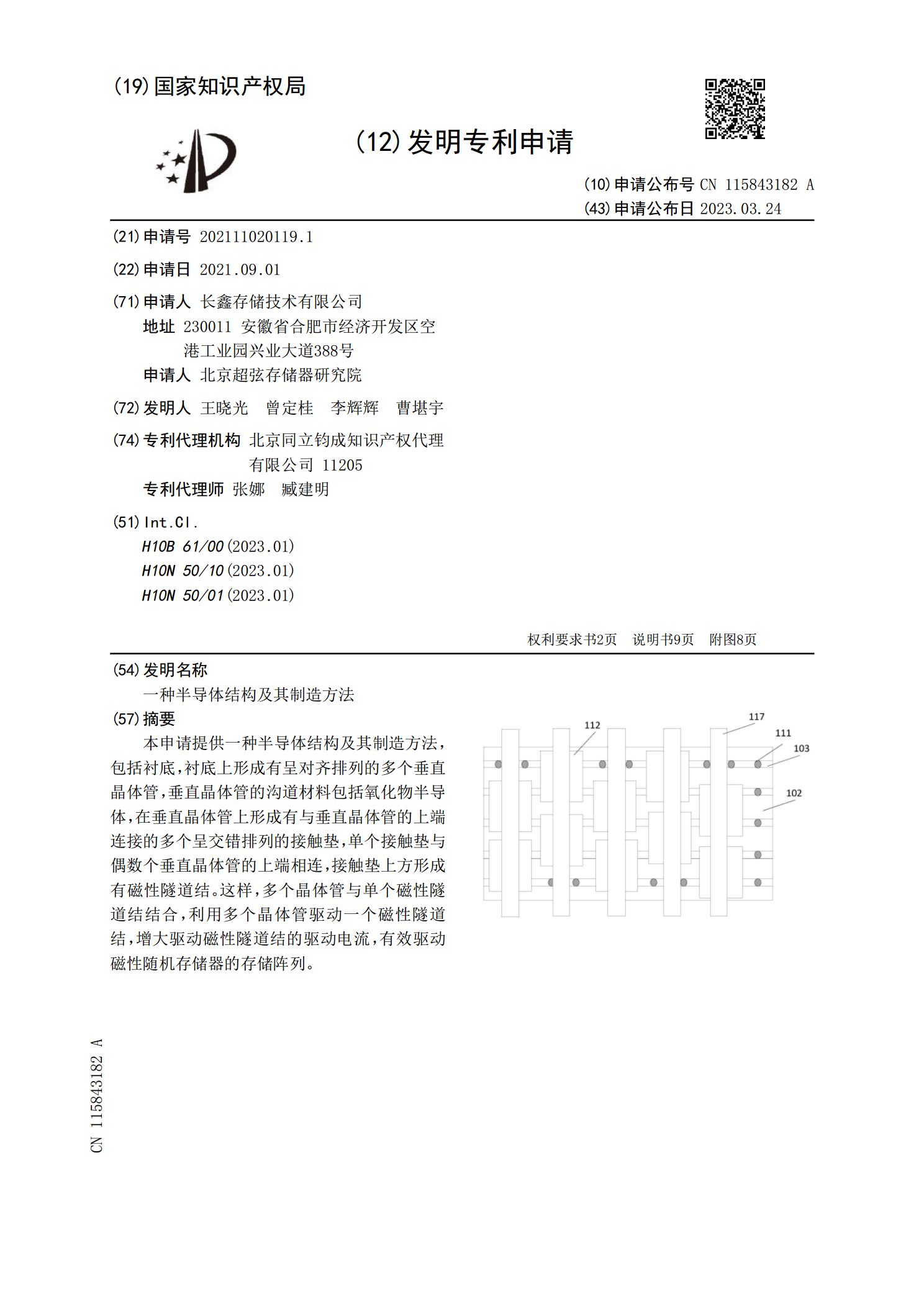

本申请提供一种半导体结构及其制造方法,包括衬底,衬底上形成有呈对齐排列的多个垂直晶体管,垂直晶体管的沟道材料包括氧化物半导体,在垂直晶体管上形成有与垂直晶体管的上端连接的多个呈交错排列的接触垫,单个接触垫与偶数个垂直晶体管的上端相连,接触垫上方形成有磁性隧道结。这样,多个晶体管与单个磁性隧道结结合,利用多个晶体管驱动一个磁性隧道结,增大驱动磁性隧道结的驱动电流,有效驱动磁性随机存储器的存储阵列。

一种半导体结构及其制造方法.pdf

本公开实施例公开了一种半导体结构及其制造方法,所述制造方法包括:提供衬底;在衬底上形成导电层,在形成导电层的过程中混入了微尘杂质颗粒,使得导电层的上表面包括第一凸起和其他平坦区域,第一凸起在衬底上的投影与微尘杂质颗粒在衬底上的投影至少部分重合;形成覆盖导电层的第一绝缘层,第一绝缘层的厚度不大于第一凸起相对于其他平坦区域的高度差;在第一绝缘层上形成第二绝缘层;去除第二绝缘层,包括:对第二绝缘层执行刻蚀工艺以暴露第一绝缘层,且第一绝缘层至少还覆盖第一凸起;其中,第二绝缘层的刻蚀速率大于第一绝缘层的刻蚀速率;采

一种半导体结构及其制造方法.pdf

本发明公开了一种半导体结构及其制造方法,包括:提供一衬底,所述衬底上包括一层叠结构;刻蚀所述层叠结构,并以所述衬底作为停止层,用以在所述层叠结构中形成至少一个沟槽;形成钝化层于所述沟槽及所述层叠结构上,其中,所述第一氧化层至少包括第一部分,第二部分和第三部分,所述第一部分,所述第二部分和所述第三部分的厚度不同;形成第二氧化层于所述第一氧化层上,所述第二氧化层的厚度大于所述第一氧化层的厚度;对所述第二氧化层进行平坦化处理,且在所述沟槽两侧的所述第一氧化层上保留预设高度的所述第二氧化层。本发明能够避免由于产生