栅氧化层的形成方法.pdf

闪闪****魔王

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

栅氧化层的形成方法.pdf

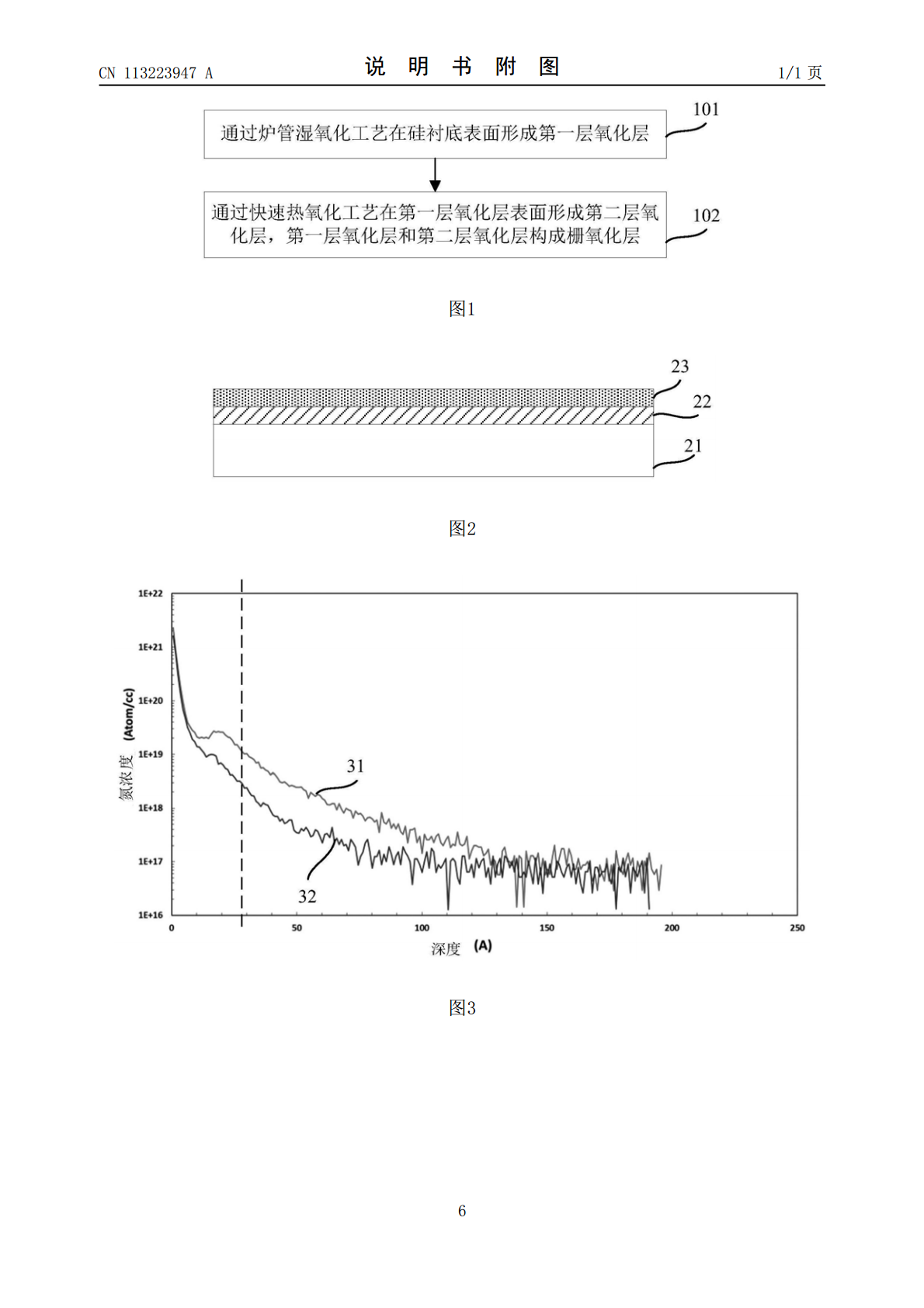

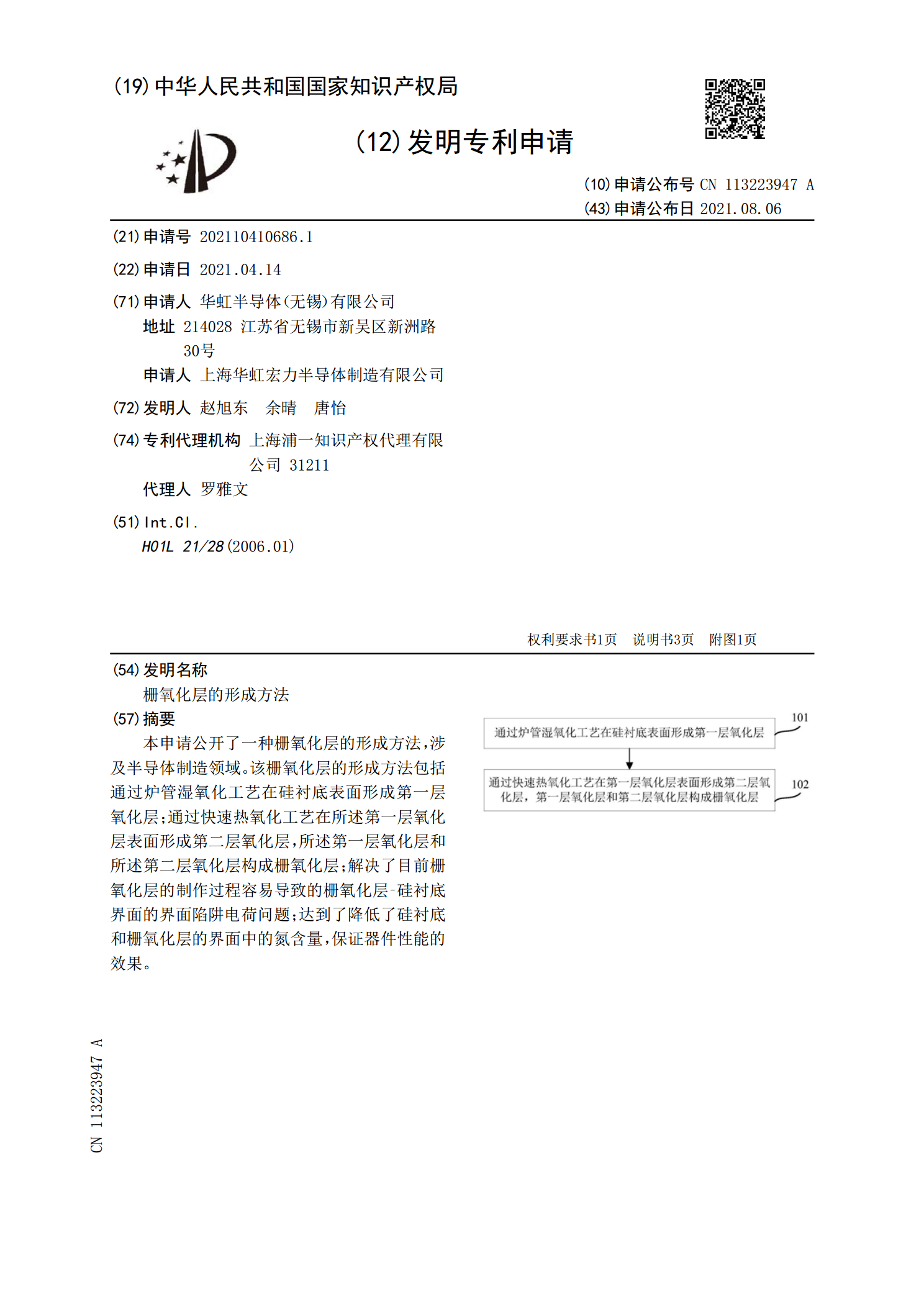

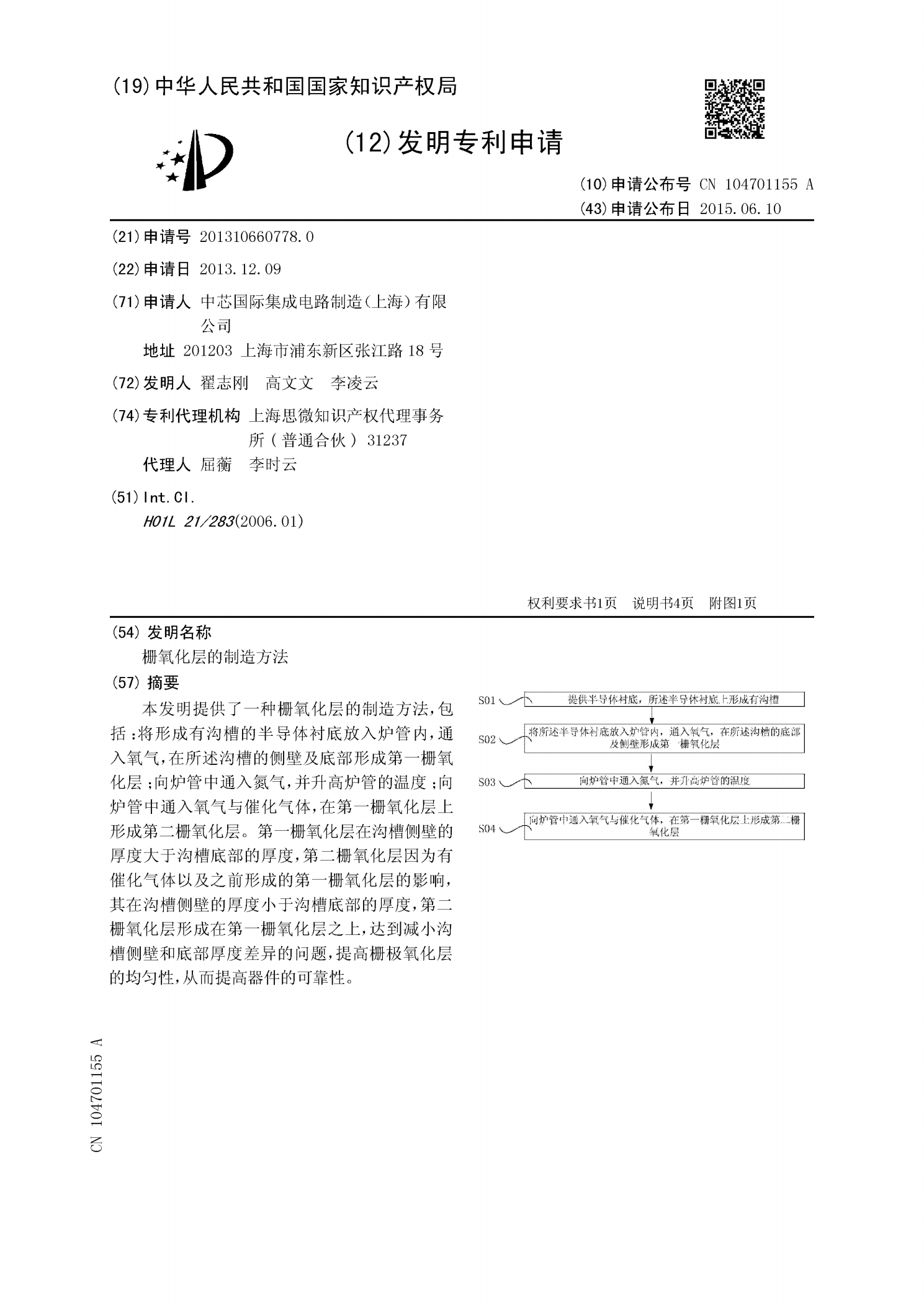

本申请公开了一种栅氧化层的形成方法,涉及半导体制造领域。该栅氧化层的形成方法包括通过炉管湿氧化工艺在硅衬底表面形成第一层氧化层;通过快速热氧化工艺在所述第一层氧化层表面形成第二层氧化层,所述第一层氧化层和所述第二层氧化层构成栅氧化层;解决了目前栅氧化层的制作过程容易导致的栅氧化层‑硅衬底界面的界面陷阱电荷问题;达到了降低了硅衬底和栅氧化层的界面中的氮含量,保证器件性能的效果。

栅氧化层的制造方法.pdf

本发明提供了一种栅氧化层的制造方法,包括:将形成有沟槽的半导体衬底放入炉管内,通入氧气,在所述沟槽的侧壁及底部形成第一栅氧化层;向炉管中通入氮气,并升高炉管的温度;向炉管中通入氧气与催化气体,在第一栅氧化层上形成第二栅氧化层。第一栅氧化层在沟槽侧壁的厚度大于沟槽底部的厚度,第二栅氧化层因为有催化气体以及之前形成的第一栅氧化层的影响,其在沟槽侧壁的厚度小于沟槽底部的厚度,第二栅氧化层形成在第一栅氧化层之上,达到减小沟槽侧壁和底部厚度差异的问题,提高栅极氧化层的均匀性,从而提高器件的可靠性。

栅氧化层的制造方法.pdf

本发明公开了一种栅氧化层的制造方法,包括步骤:步骤一、提供表面形成有第一介质层的半导体衬底并形成光刻胶图形。步骤二、以光刻胶图形为掩膜对第一介质层进行刻蚀。步骤三、在去胶机台中进行去胶,在去胶的同时在第一介质层的保留区域外形成栅氧化层。本发明能提高栅氧化层的生长速率,降低工艺成本。

高压栅氧化层制作方法、高压栅氧化层和终端设备.pdf

本发明公开了一种高压栅氧化层制作方法,包括:提供衬底,在衬底上形成浅沟槽隔离;淀积第一厚度的氮化层;淀积第二厚度的氧化层;旋涂光刻胶,将高压栅氧化层区域打开,刻蚀去除高压栅氧化层区域的氧化层,去除光刻胶;将氧化层作为掩蔽层,刻蚀去除高压栅氧化层区域的氮化层;刻蚀去除剩余氧化层,同时刻蚀去除高压栅氧化层区域的浅沟槽隔离台阶;制作高压栅氧化层,刻蚀去除剩余的氮化层。本发明能避免形成氮化物刻蚀残留,提高器件综合性能。

CMOS器件栅氧化层的制造方法.pdf

本发明公开了一种CMOS器件栅氧化层的制造方法,包括在硅衬底上制备浅沟道隔离区、衬垫氧化层和硬掩膜,通过刻蚀两个浅沟道隔离区之间的场区以露出有源区及有源区边缘的部分浅沟道隔离区;通过炉管工艺,在有源区表面生长一层氧化层,使得有源区的边缘圆化;通过湿法刻蚀,去除有源区表面的氧化层;通过炉管工艺,在有源区表面生长栅氧化层。本发明利用炉管工艺在有源区表面生成一层氧化层,随后利用湿法刻蚀将其去除,通过这两步工艺可以改善有源区的边缘尖角,改善栅氧化层的形貌,从而提高器件的性能。