改善晶圆翘曲的方法.pdf

悠柔****找我

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

改善晶圆翘曲的方法.pdf

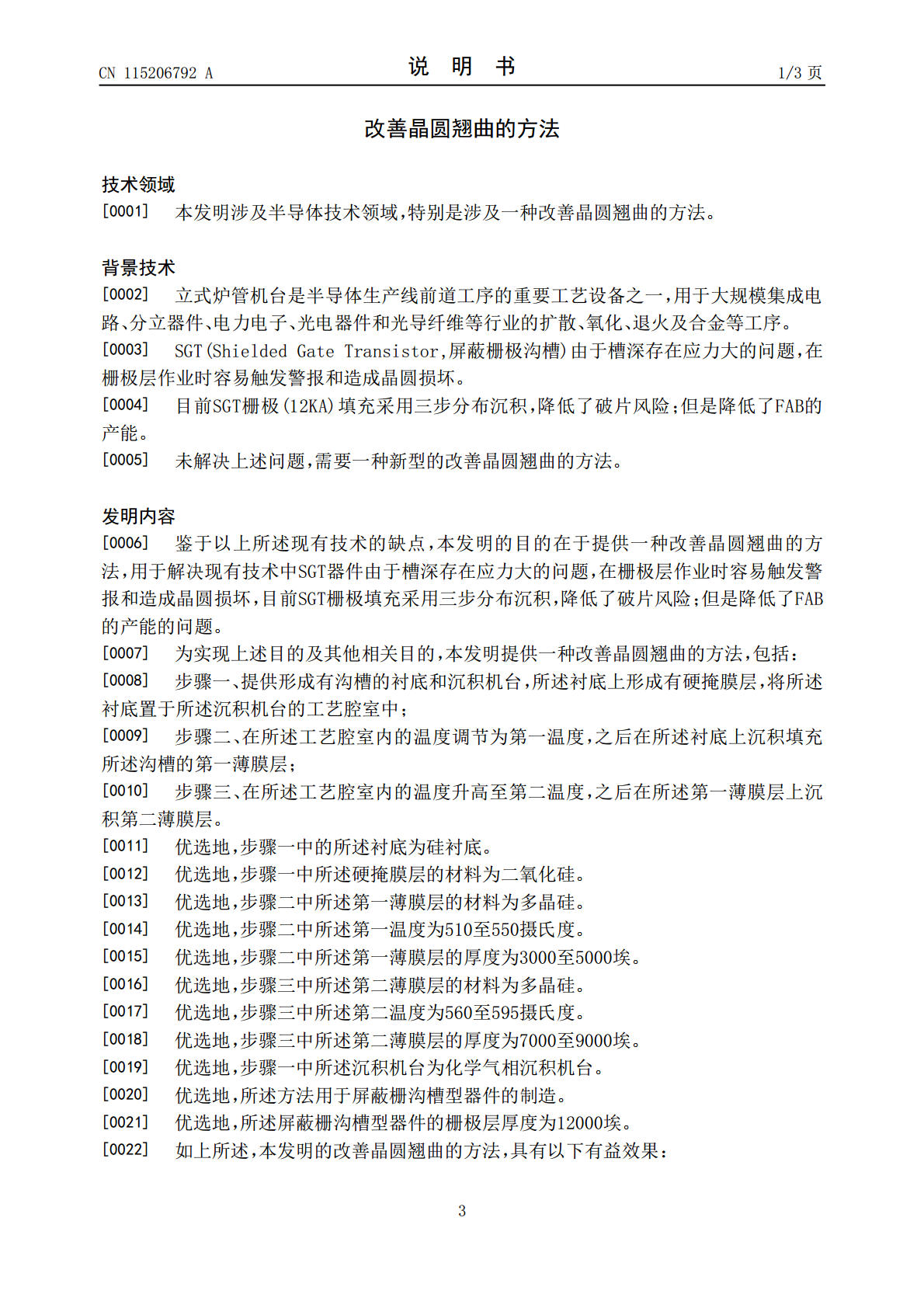

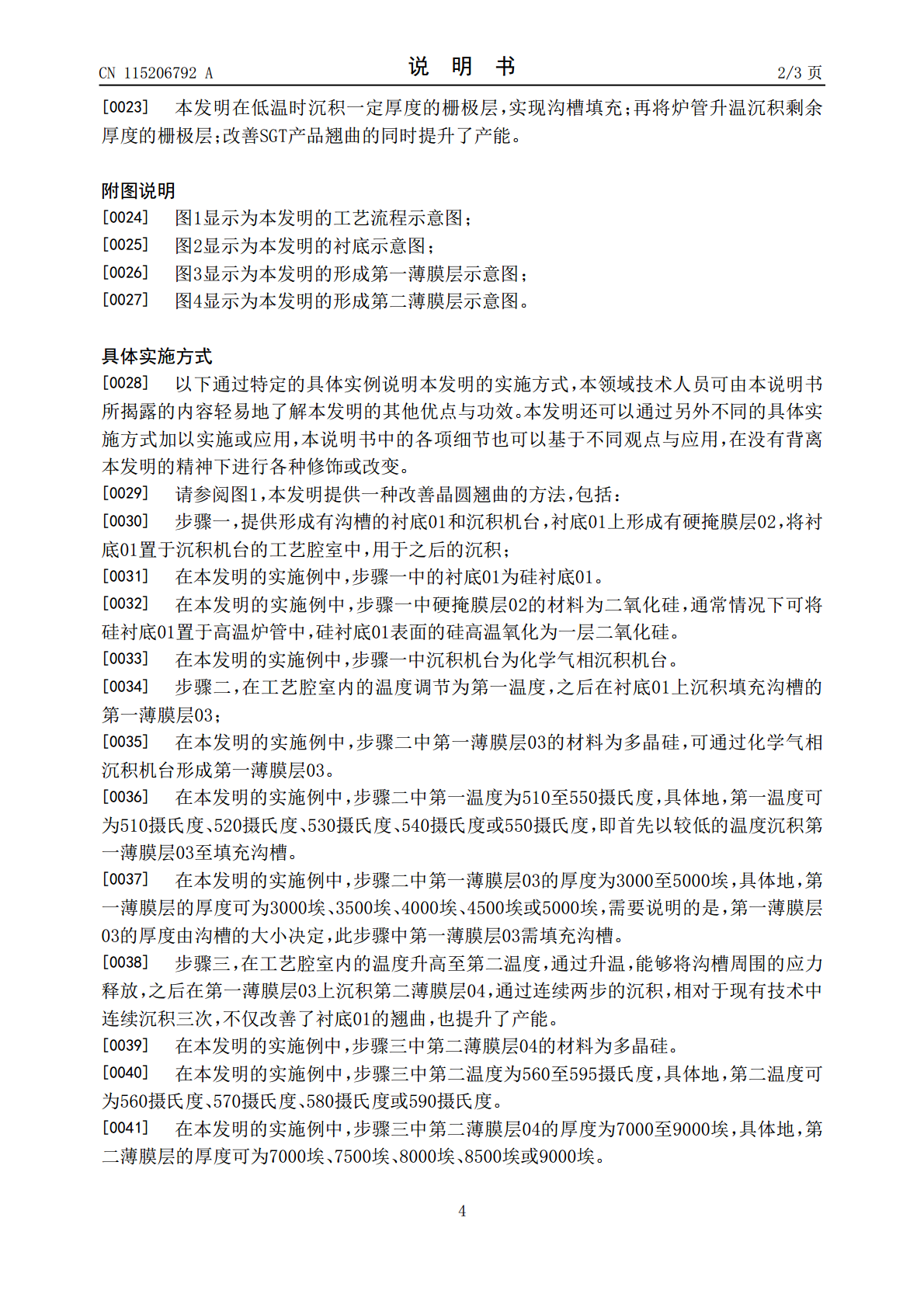

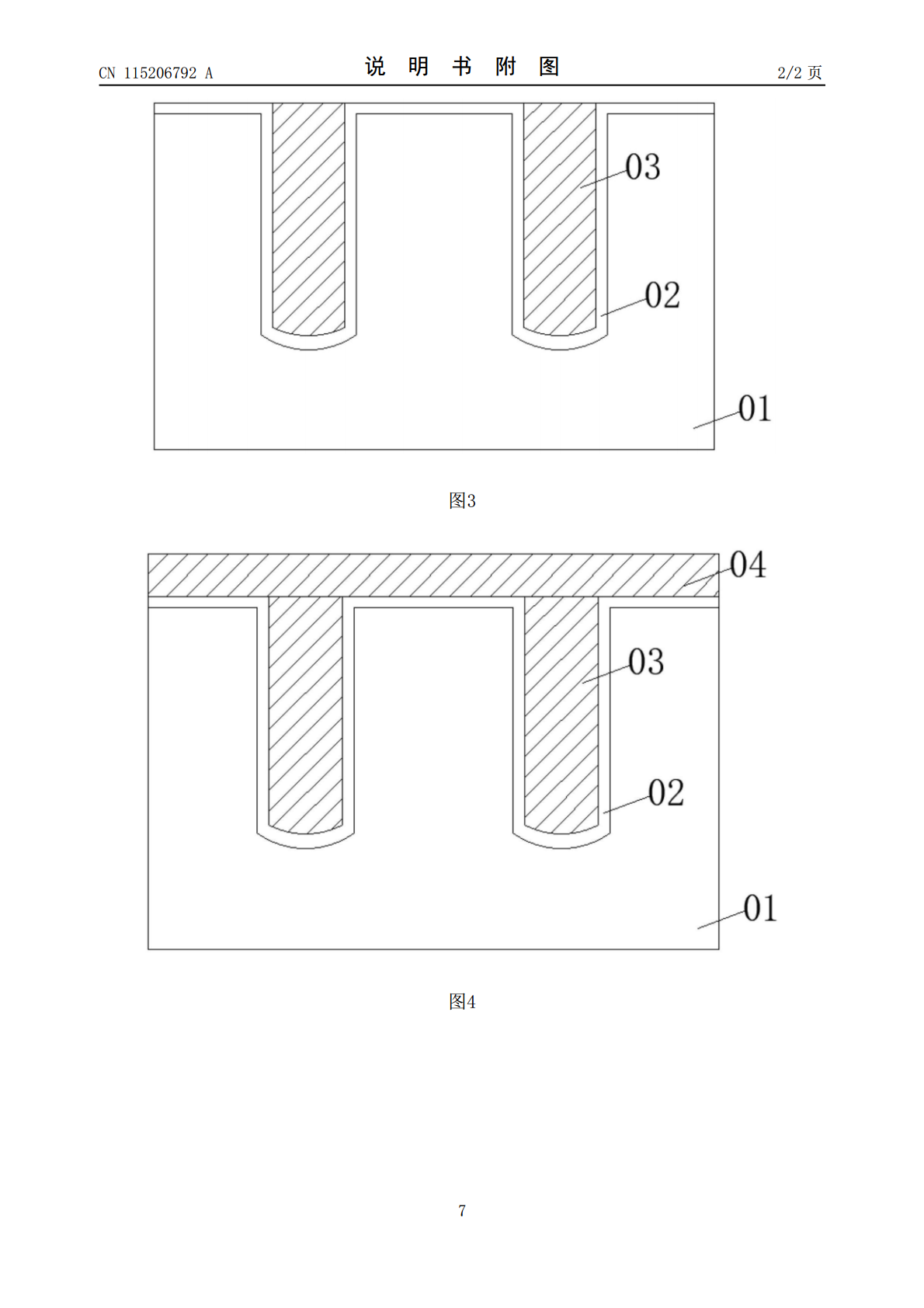

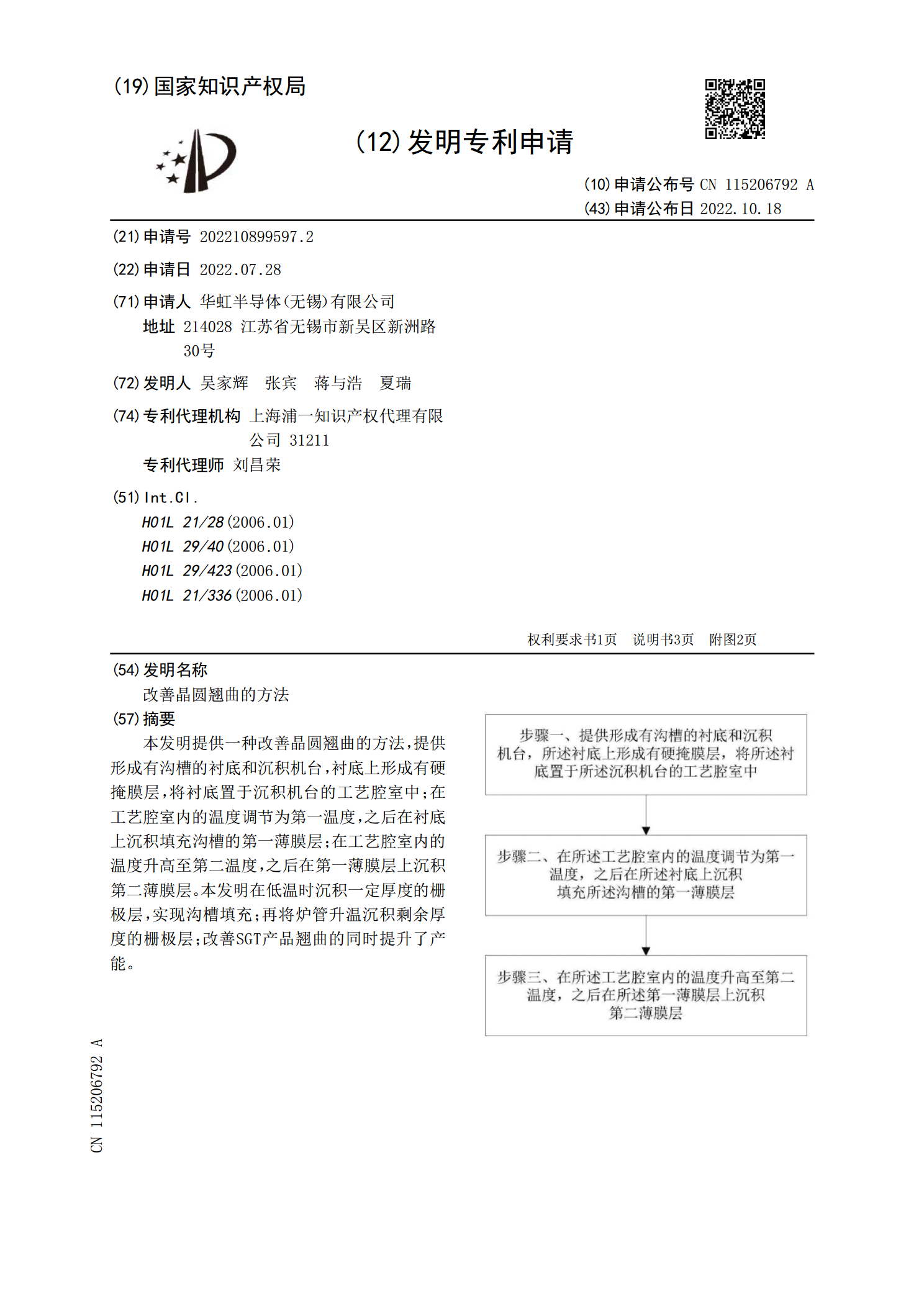

本发明提供一种改善晶圆翘曲的方法,提供形成有沟槽的衬底和沉积机台,衬底上形成有硬掩膜层,将衬底置于沉积机台的工艺腔室中;在工艺腔室内的温度调节为第一温度,之后在衬底上沉积填充沟槽的第一薄膜层;在工艺腔室内的温度升高至第二温度,之后在第一薄膜层上沉积第二薄膜层。本发明在低温时沉积一定厚度的栅极层,实现沟槽填充;再将炉管升温沉积剩余厚度的栅极层;改善SGT产品翘曲的同时提升了产能。

改善晶圆翘曲的方法.pdf

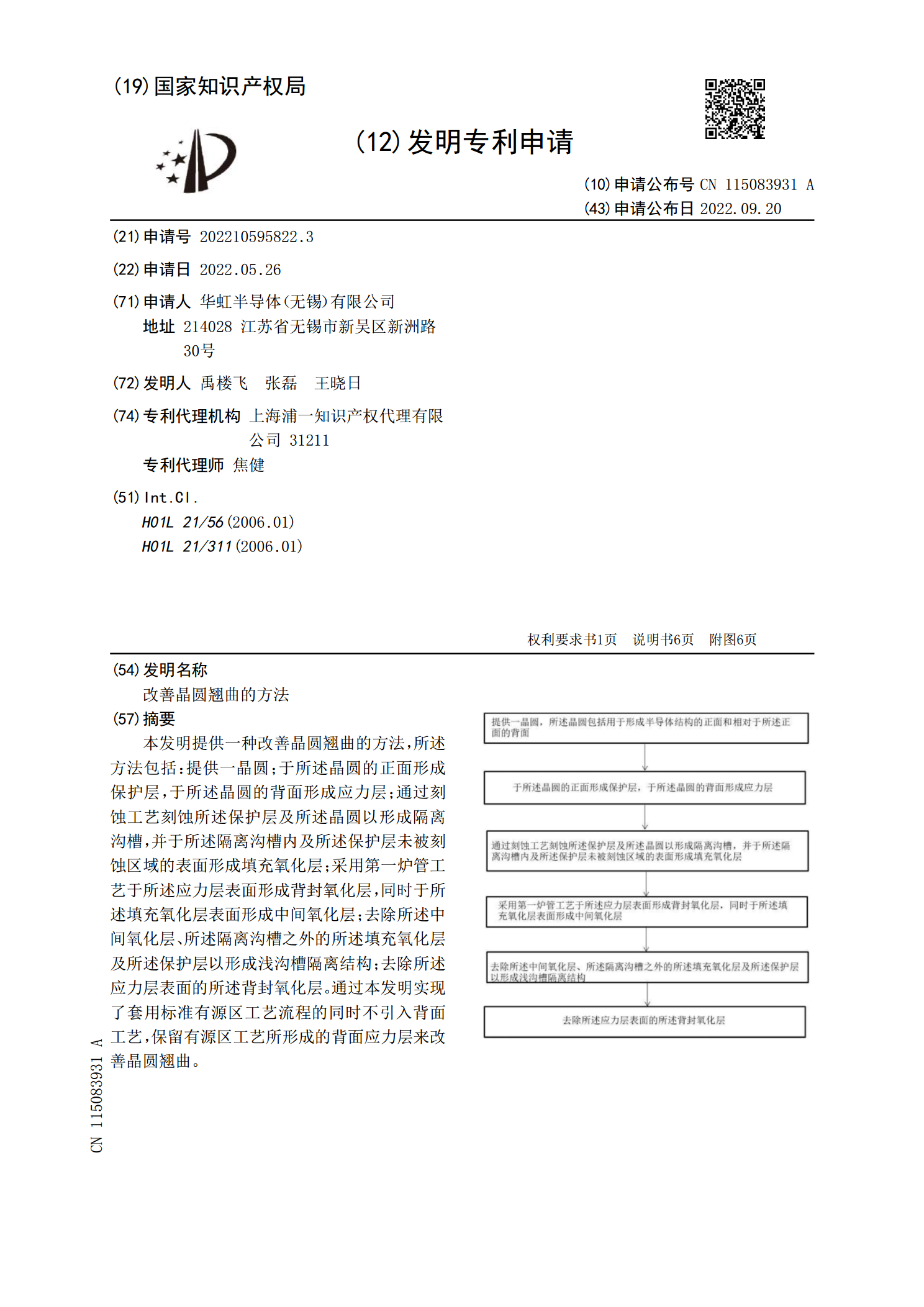

本发明提供一种改善晶圆翘曲的方法,所述方法包括:提供一晶圆;于所述晶圆的正面形成保护层,于所述晶圆的背面形成应力层;通过刻蚀工艺刻蚀所述保护层及所述晶圆以形成隔离沟槽,并于所述隔离沟槽内及所述保护层未被刻蚀区域的表面形成填充氧化层;采用第一炉管工艺于所述应力层表面形成背封氧化层,同时于所述填充氧化层表面形成中间氧化层;去除所述中间氧化层、所述隔离沟槽之外的所述填充氧化层及所述保护层以形成浅沟槽隔离结构;去除所述应力层表面的所述背封氧化层。通过本发明实现了套用标准有源区工艺流程的同时不引入背面工艺,保留有源

一种改善TAIKO减薄剥膜前晶圆翘曲的方法.pdf

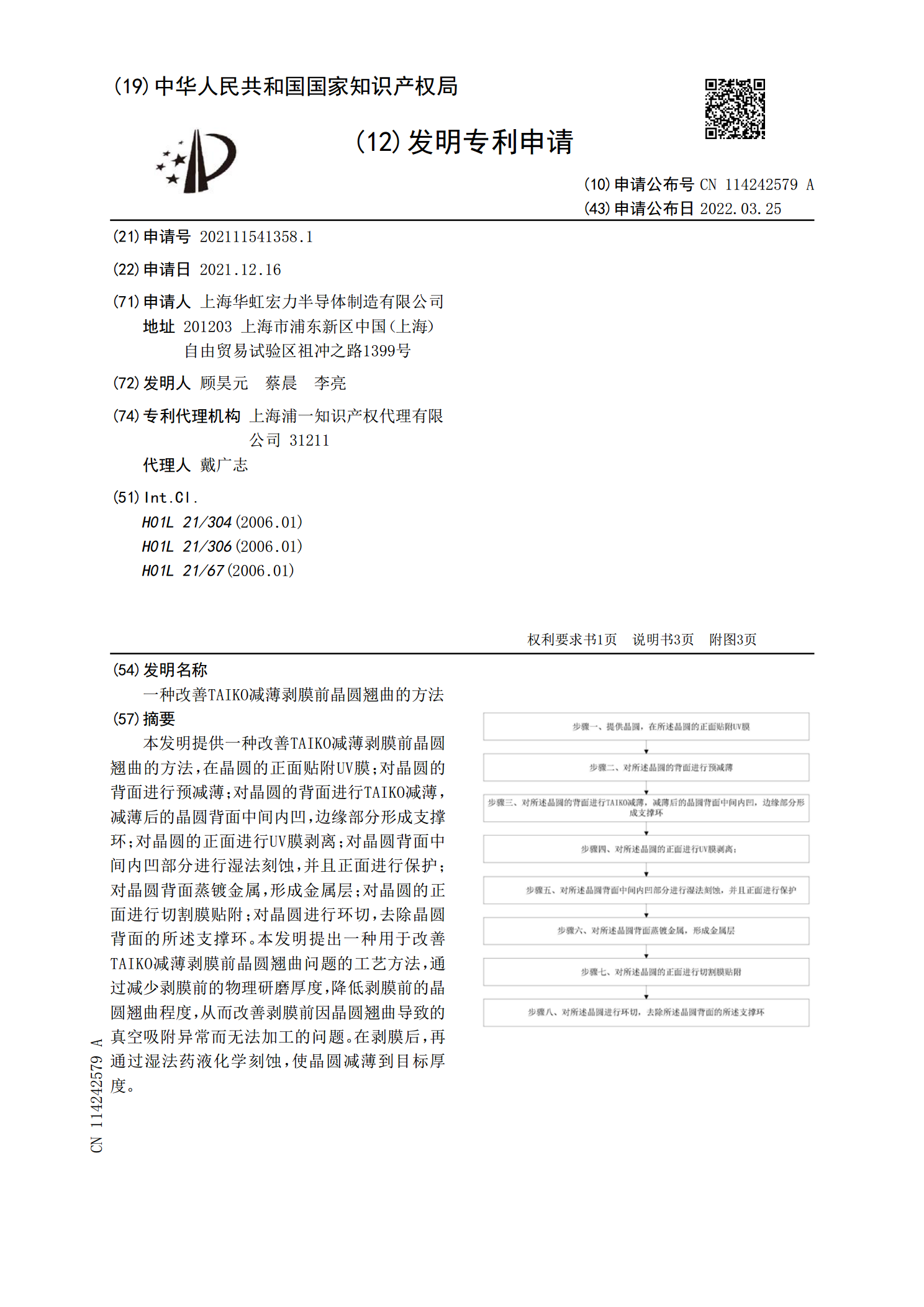

本发明提供一种改善TAIKO减薄剥膜前晶圆翘曲的方法,在晶圆的正面贴附UV膜;对晶圆的背面进行预减薄;对晶圆的背面进行TAIKO减薄,减薄后的晶圆背面中间内凹,边缘部分形成支撑环;对晶圆的正面进行UV膜剥离;对晶圆背面中间内凹部分进行湿法刻蚀,并且正面进行保护;对晶圆背面蒸镀金属,形成金属层;对晶圆的正面进行切割膜贴附;对晶圆进行环切,去除晶圆背面的所述支撑环。本发明提出一种用于改善TAIKO减薄剥膜前晶圆翘曲问题的工艺方法,通过减少剥膜前的物理研磨厚度,降低剥膜前的晶圆翘曲程度,从而改善剥膜前因晶圆翘曲

翘曲晶圆对位标记设置方法.pdf

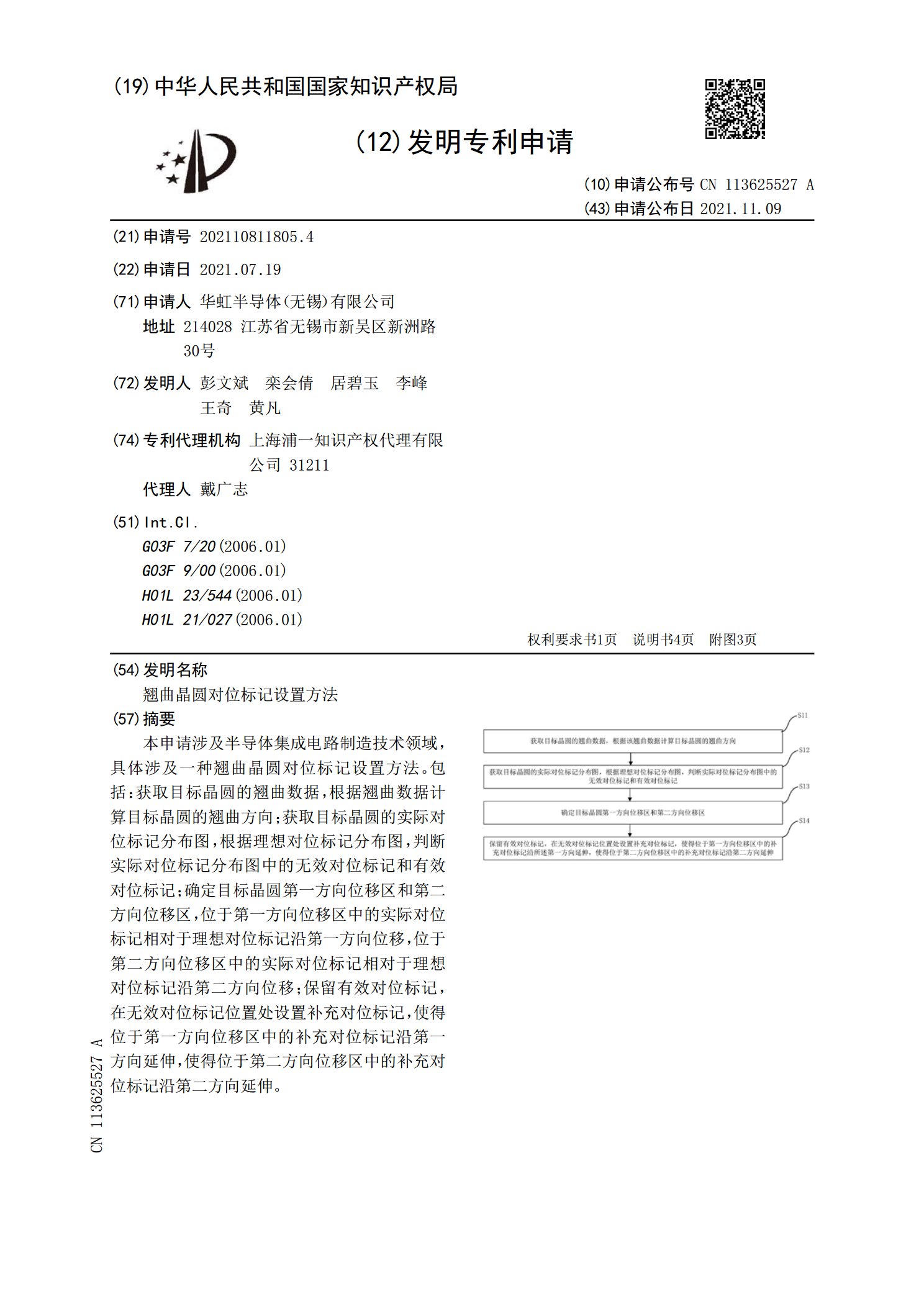

本申请涉及半导体集成电路制造技术领域,具体涉及一种翘曲晶圆对位标记设置方法。包括:获取目标晶圆的翘曲数据,根据翘曲数据计算目标晶圆的翘曲方向;获取目标晶圆的实际对位标记分布图,根据理想对位标记分布图,判断实际对位标记分布图中的无效对位标记和有效对位标记;确定目标晶圆第一方向位移区和第二方向位移区,位于第一方向位移区中的实际对位标记相对于理想对位标记沿第一方向位移,位于第二方向位移区中的实际对位标记相对于理想对位标记沿第二方向位移;保留有效对位标记,在无效对位标记位置处设置补充对位标记,使得位于第一方向位移

WLCSP封装晶圆翘曲成因与控制方法研究.docx

WLCSP封装晶圆翘曲成因与控制方法研究WLCSP封装晶圆翘曲成因与控制方法研究摘要:WLCSP(WaferLevelChipScalePackage)封装技术是一种先进的半导体器件封装技术,其具有封装尺寸小、重量轻、成本低等优势,被广泛应用于移动通信、消费电子等领域。然而,WLCSP封装晶圆翘曲问题一直困扰着封装工艺的稳定性和可靠性。本文通过对WLCSP封装晶圆翘曲的成因进行分析,提出了相应的控制方法,以期改善封装技术的质量,推动WLCSP应用的发展。1.引言WLCSP封装技术具有封装尺寸小、重量轻、成