基于锗的量子阱器件.pdf

一吃****海逸

亲,该文档总共29页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于锗的量子阱器件.pdf

一种量子阱晶体管具有锗量子阱沟道区。含硅的蚀刻停止层提供栅电介质接近沟道的容易放置。III-V族势垒层对沟道增加应变。沟道区之上和之下的缓变硅锗层改进了性能。多种栅电介质材料允许使用高k值栅电介质。

非平面锗量子阱装置.pdf

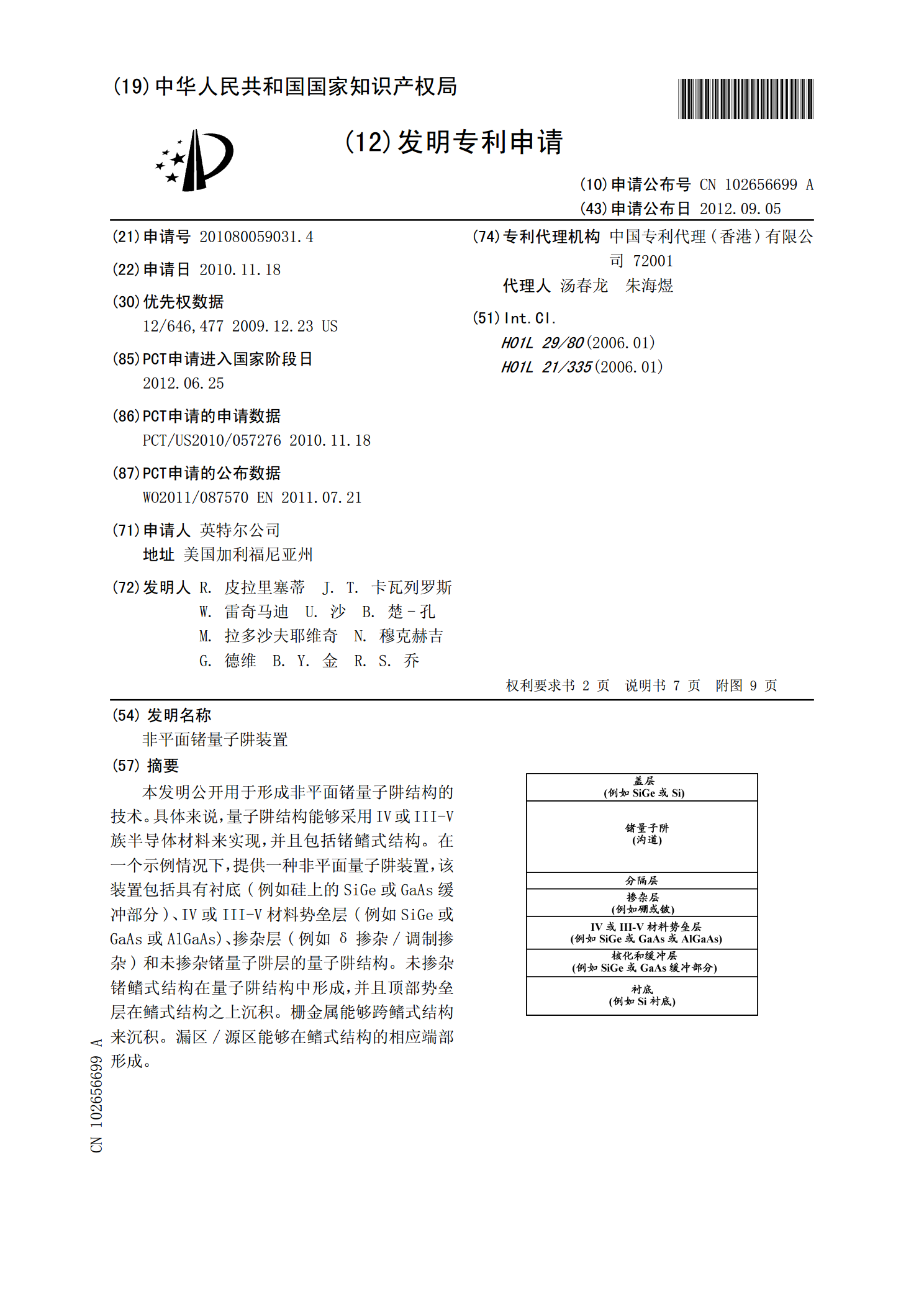

本发明公开用于形成非平面锗量子阱结构的技术。具体来说,量子阱结构能够采用IV或III-V族半导体材料来实现,并且包括锗鳍式结构。在一个示例情况下,提供一种非平面量子阱装置,该装置包括具有衬底(例如硅上的SiGe或GaAs缓冲部分)、IV或III-V材料势垒层(例如SiGe或GaAs或AlGaAs)、掺杂层(例如δ掺杂/调制掺杂)和未掺杂锗量子阱层的量子阱结构。未掺杂锗鳍式结构在量子阱结构中形成,并且顶部势垒层在鳍式结构之上沉积。栅金属能够跨鳍式结构来沉积。漏区/源区能够在鳍式结构的相应端部形成。

非平面锗量子阱装置.pdf

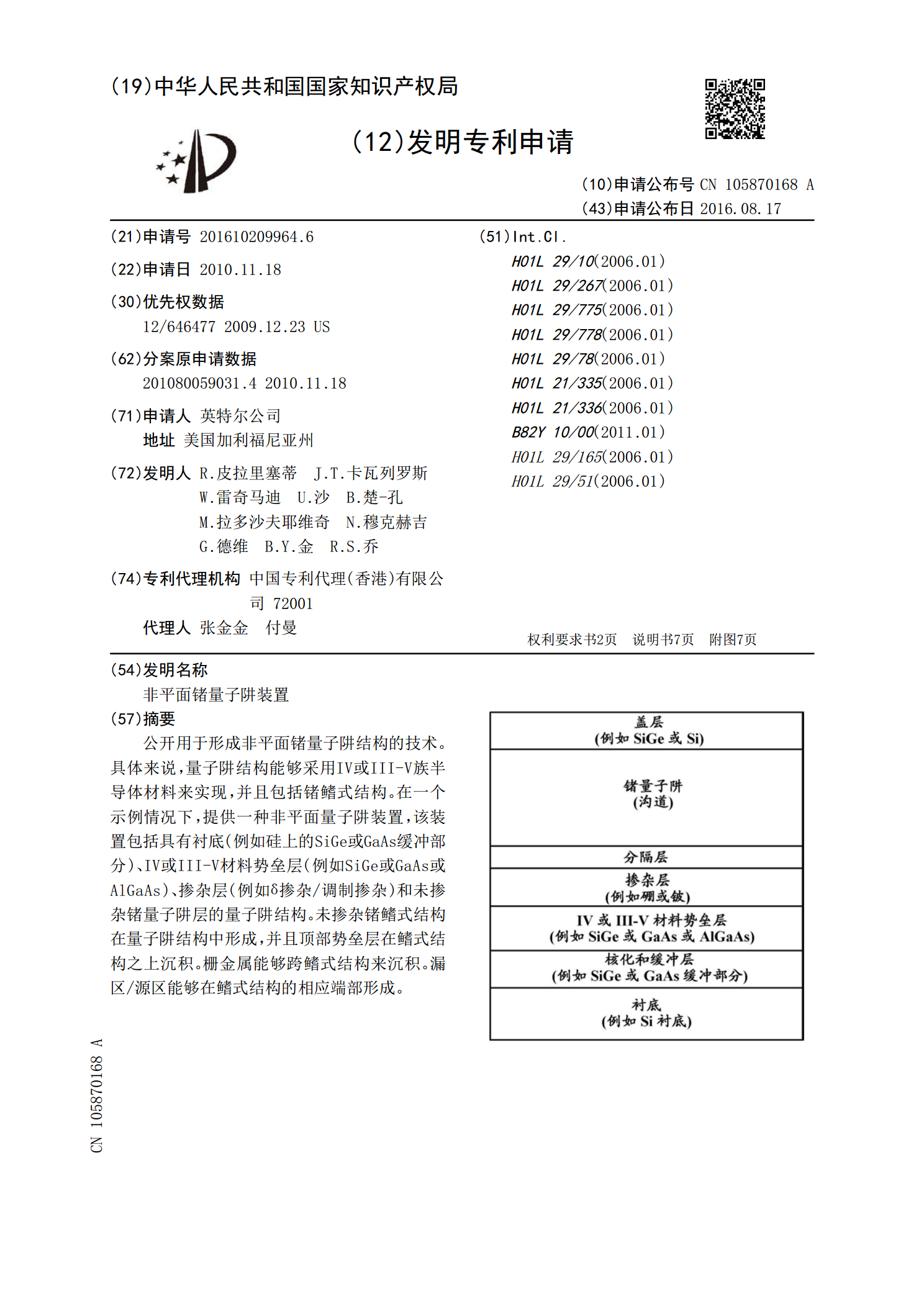

公开用于形成非平面锗量子阱结构的技术。具体来说,量子阱结构能够采用IV或III‑V族半导体材料来实现,并且包括锗鳍式结构。在一个示例情况下,提供一种非平面量子阱装置,该装置包括具有衬底(例如硅上的SiGe或GaAs缓冲部分)、IV或III‑V材料势垒层(例如SiGe或GaAs或AlGaAs)、掺杂层(例如δ掺杂/调制掺杂)和未掺杂锗量子阱层的量子阱结构。未掺杂锗鳍式结构在量子阱结构中形成,并且顶部势垒层在鳍式结构之上沉积。栅金属能够跨鳍式结构来沉积。漏区/源区能够在鳍式结构的相应端部形成。

非平面锗量子阱装置.pdf

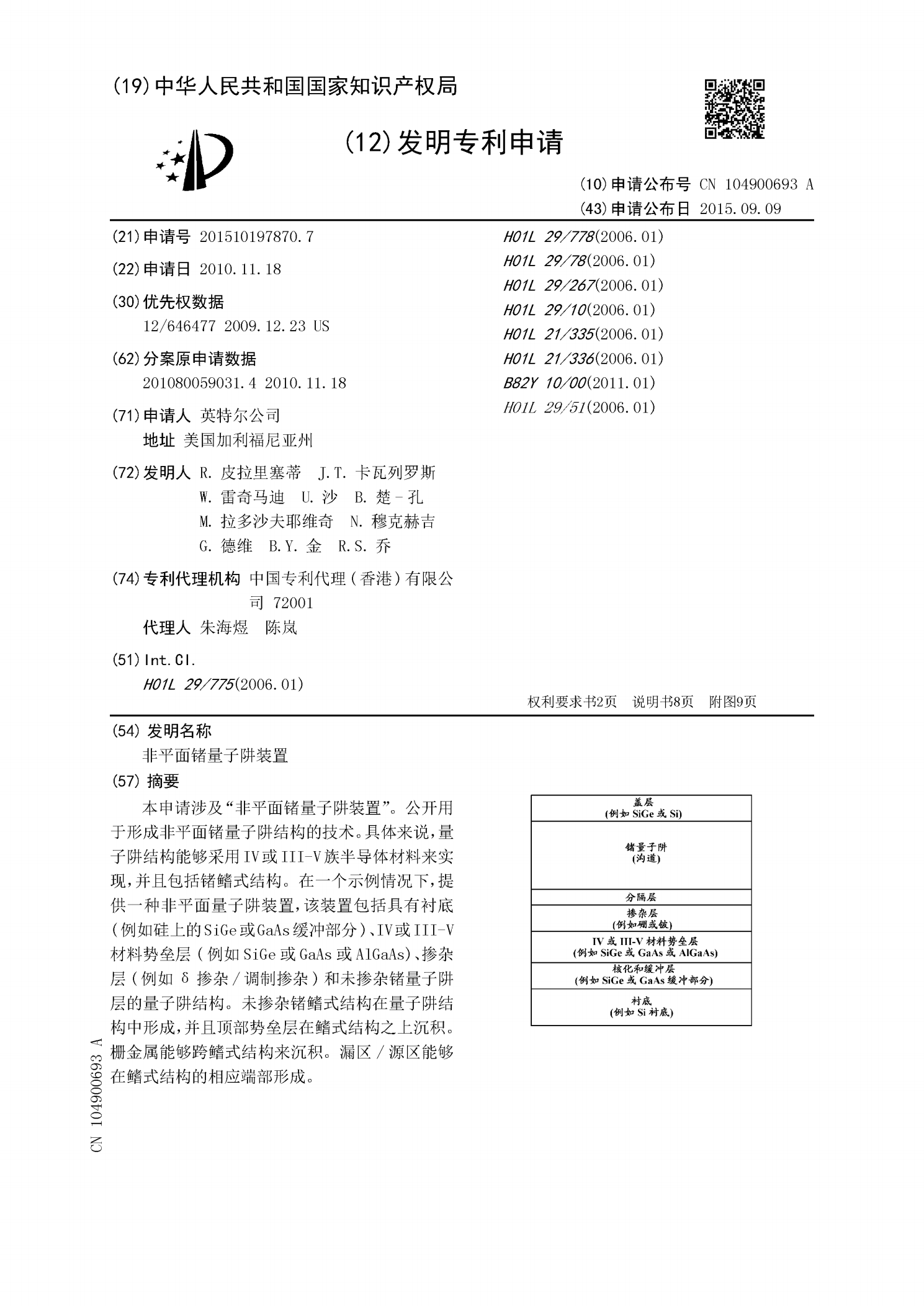

本申请涉及“非平面锗量子阱装置”。公开用于形成非平面锗量子阱结构的技术。具体来说,量子阱结构能够采用IV或III-V族半导体材料来实现,并且包括锗鳍式结构。在一个示例情况下,提供一种非平面量子阱装置,该装置包括具有衬底(例如硅上的SiGe或GaAs缓冲部分)、IV或III-V材料势垒层(例如SiGe或GaAs或AlGaAs)、掺杂层(例如δ掺杂/调制掺杂)和未掺杂锗量子阱层的量子阱结构。未掺杂锗鳍式结构在量子阱结构中形成,并且顶部势垒层在鳍式结构之上沉积。栅金属能够跨鳍式结构来沉积。漏区/源区能够在鳍式结

基于锗量子点的硅基发光器件.docx

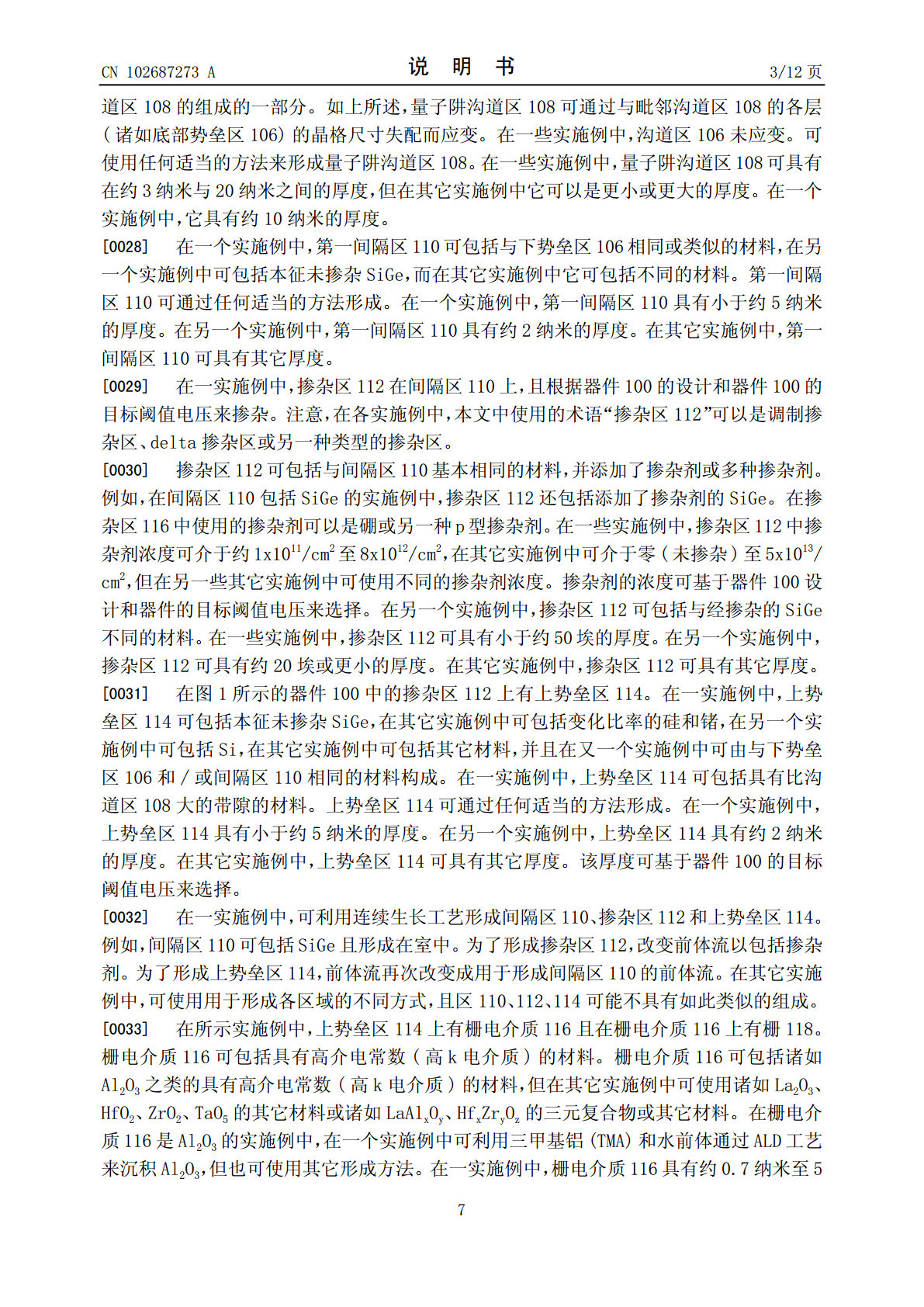

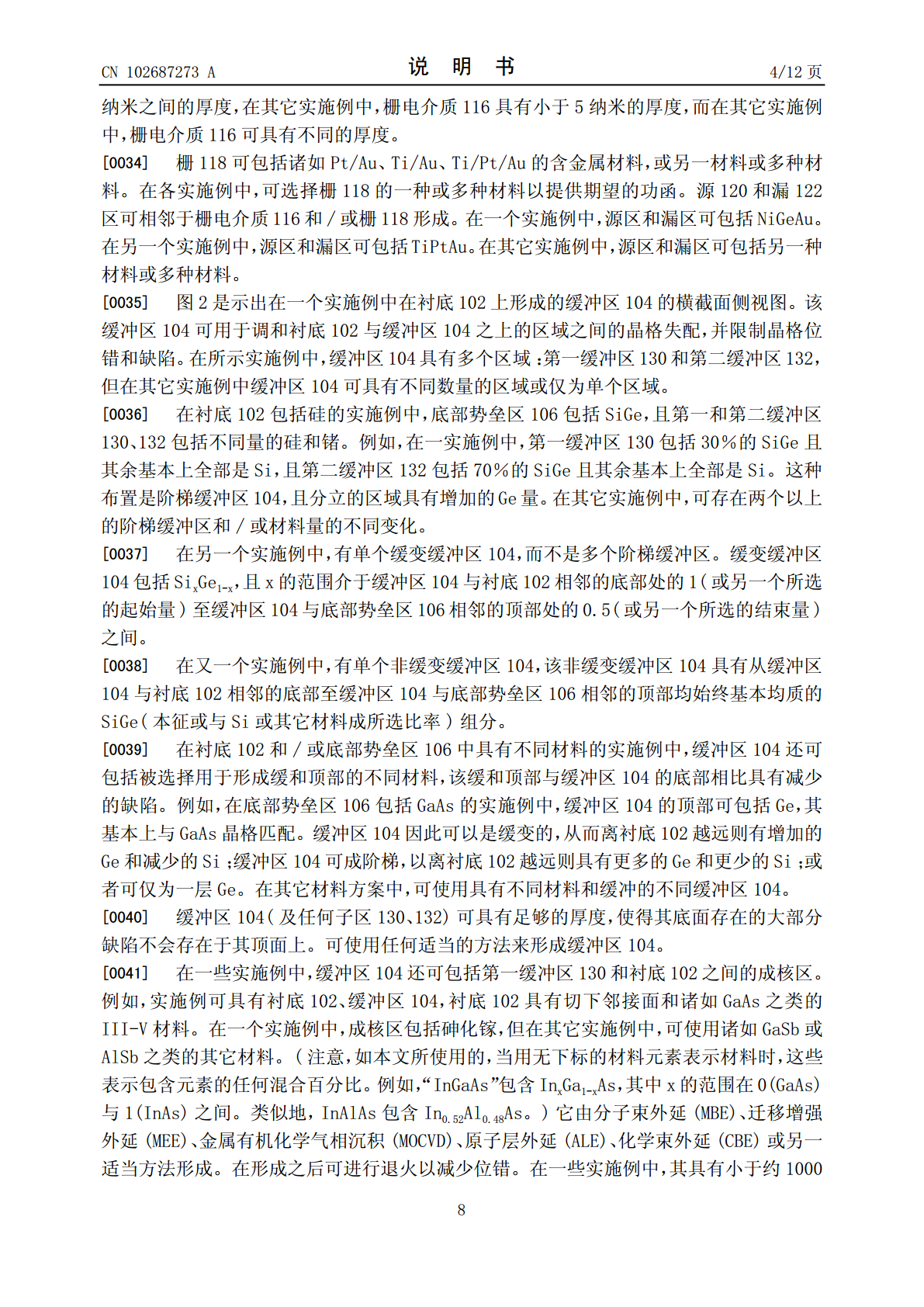

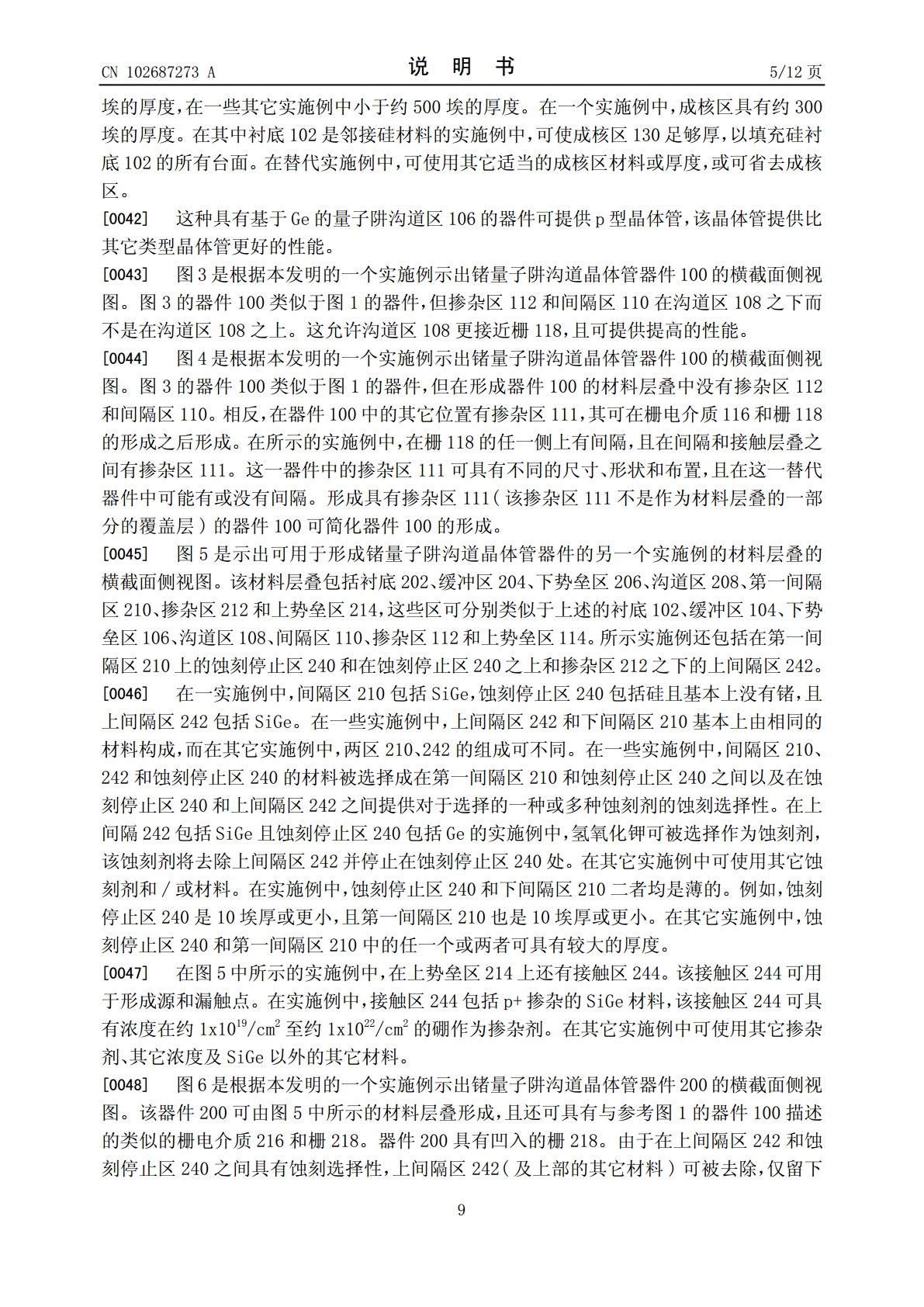

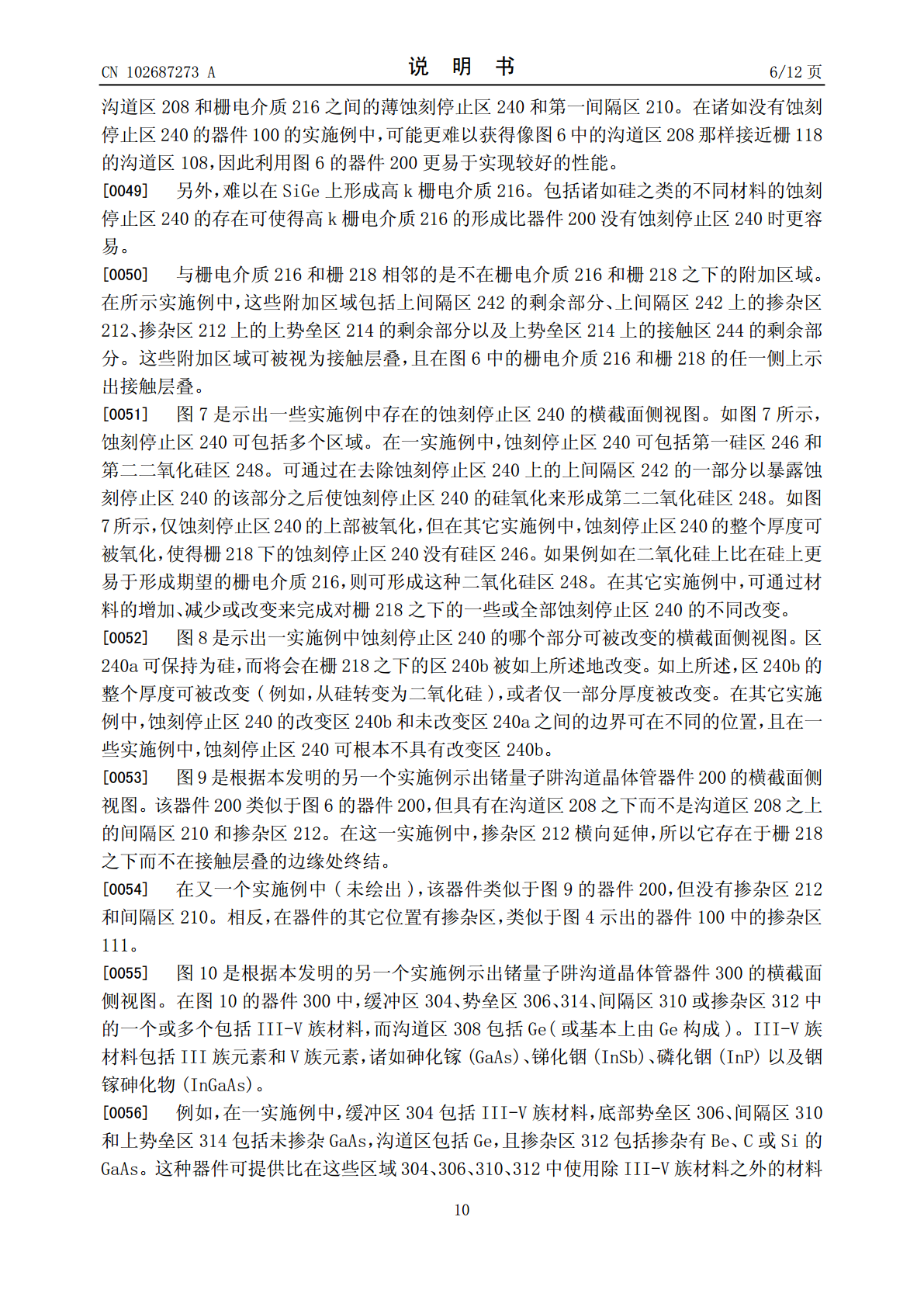

基于锗量子点的硅基发光器件锗量子点(GeQDs)是一种具有吸引力的纳米材料,它们具有高量子效率、可调控的光谱特性以及高生物相容性,因此在生物医学成像、量子点光电器件等领域中具有广泛应用。本文将介绍基于锗量子点的硅基发光器件及其关键性能参数和应用。一、锗量子点的制备方法当前,制备锗量子点主要有两种主要方法:一种是溶液化学方法,另一种是气相法。其中溶液化学方法包括热分解法、微乳液法、溶剂热法、水热法等。这些方法都可以通过不同的实验条件和反应物来实现对成键和颗粒尺寸的控制。气相法则包括简单的热蒸发法、气相反应法