用于硅衬底上的III-V族氮化物层的梯度氮化铝镓和超晶格缓冲层.pdf

小琛****82

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

用于硅衬底上的III-V族氮化物层的梯度氮化铝镓和超晶格缓冲层.pdf

本发明涉及集成电路以及用于制造集成电路的方法。集成电路包括晶格匹配结构。晶格匹配结构可以包括第一缓冲区、第二缓冲区和由AlxGa1-xN/AlyGa1-yN层对形成的超晶格结构。本发明提供了用于硅衬底上的III-V族氮化物层的梯度氮化铝镓和超晶格缓冲层。

用于硅衬底上的III族氮化物的扩散阻挡层.pdf

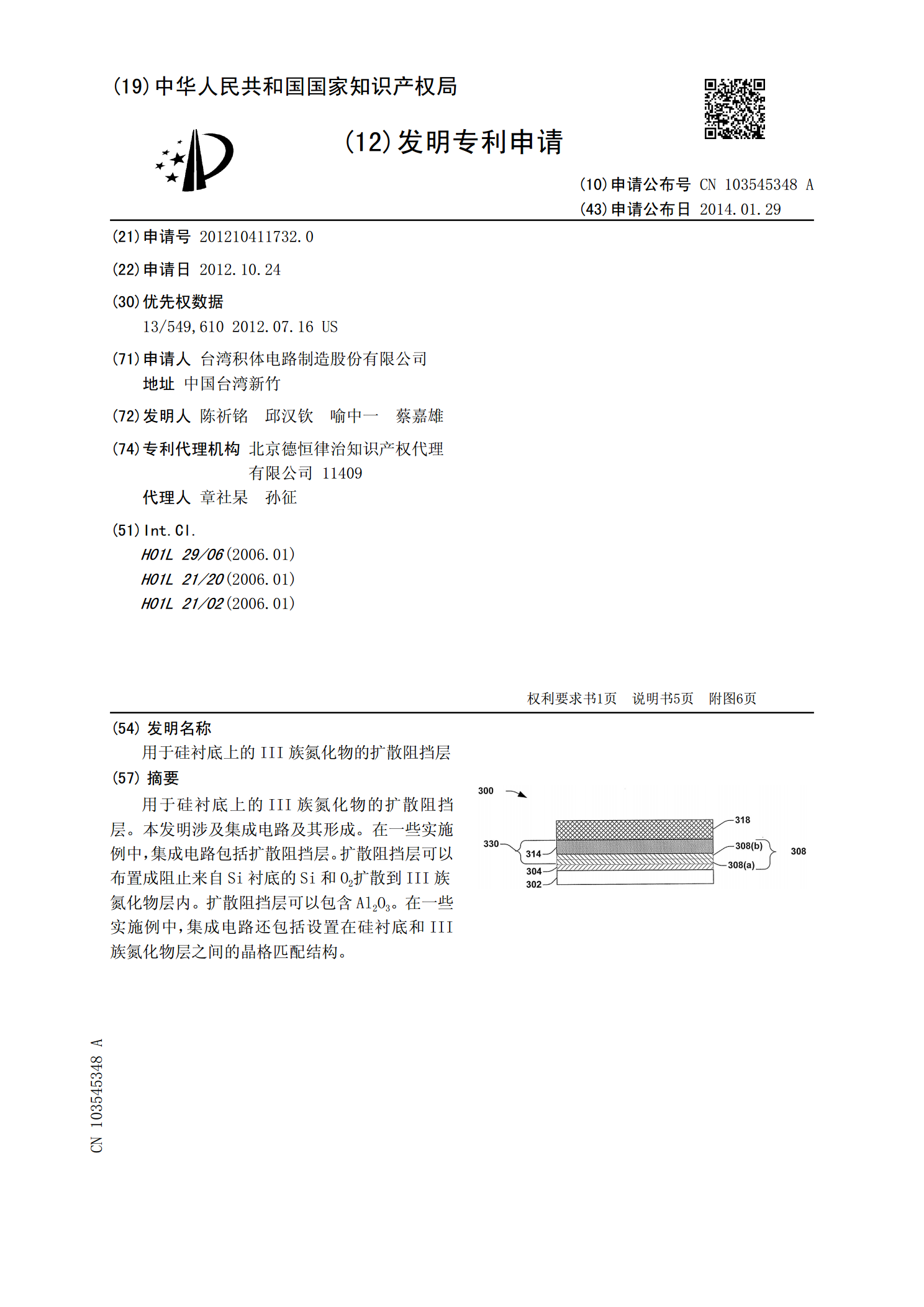

用于硅衬底上的III族氮化物的扩散阻挡层。本发明涉及集成电路及其形成。在一些实施例中,集成电路包括扩散阻挡层。扩散阻挡层可以布置成阻止来自Si衬底的Si和O2扩散到III族氮化物层内。扩散阻挡层可以包含Al2O3。在一些实施例中,集成电路还包括设置在硅衬底和III族氮化物层之间的晶格匹配结构。

硅衬底上缓冲层研究.docx

硅衬底上缓冲层研究硅衬底上缓冲层研究摘要:在半导体器件制造过程中,硅衬底上缓冲层扮演着至关重要的角色,能够有效地提高半导体器件的性能。本文综述了硅衬底上缓冲层的研究现状,并对不同类型的缓冲层进行了详细的分析和比较。其中包括了氮化硅、氮化铝和氮化钛等材料的缓冲层。此外,本文还讨论了缓冲层在不同半导体器件中的应用,并对未来硅衬底上缓冲层研究的发展方向进行了展望。关键词:硅衬底、缓冲层、半导体器件、性能提升、氮化硅、氮化铝、氮化钛引言:半导体器件是现代高科技业的核心,其性能的提升对实现智能化和信息技术发展具有重

适用于具有异质衬底的III族氮化物器件的缓冲层结构.pdf

本公开内容的实施例包括适用于具有异质衬底的III-N器件的缓冲结构。缓冲结构可以包括具有第一铝组分的第一缓冲层以及形成在第一缓冲层上的第二缓冲层,第二缓冲层具有第二铝组分。缓冲结构进一步包括在第二界面处形成在第二缓冲层上的第三缓冲层,第三缓冲层具有第三铝组分。第一铝组分在第一缓冲层中朝向界面降低且第二铝组分贯穿第二缓冲层大于界面处的第一铝组分。

GaAs衬底采用AlGaInN缓冲层生长三族氮化物的方法.pdf

本发明公开了一种GaAs衬底采用AlGaInN缓冲层生长三族氮化物的方法,涉及制造半导体器件的方法。该方法应用于制作GaN基异质结场效应晶体管(HFET)、发光二极管(LED)和激光器(LD)材料与器件,其采用金属有机化学气相沉积(MOCVD)、分子束外延(MBE)或者氢化物气相外延(HVPE)生长系统在GaAs衬底采用AlGaInN缓冲层外延生长三族氮化物,进而开展GaN基微电子和光电子器件结构的外延生长。利用本发明方法制作的GaAs衬底三族氮化物外延材料位错密度大大降低,提高了外延材料的晶体质量,同时