用于硅衬底上的III族氮化物的扩散阻挡层.pdf

Jo****31

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

用于硅衬底上的III族氮化物的扩散阻挡层.pdf

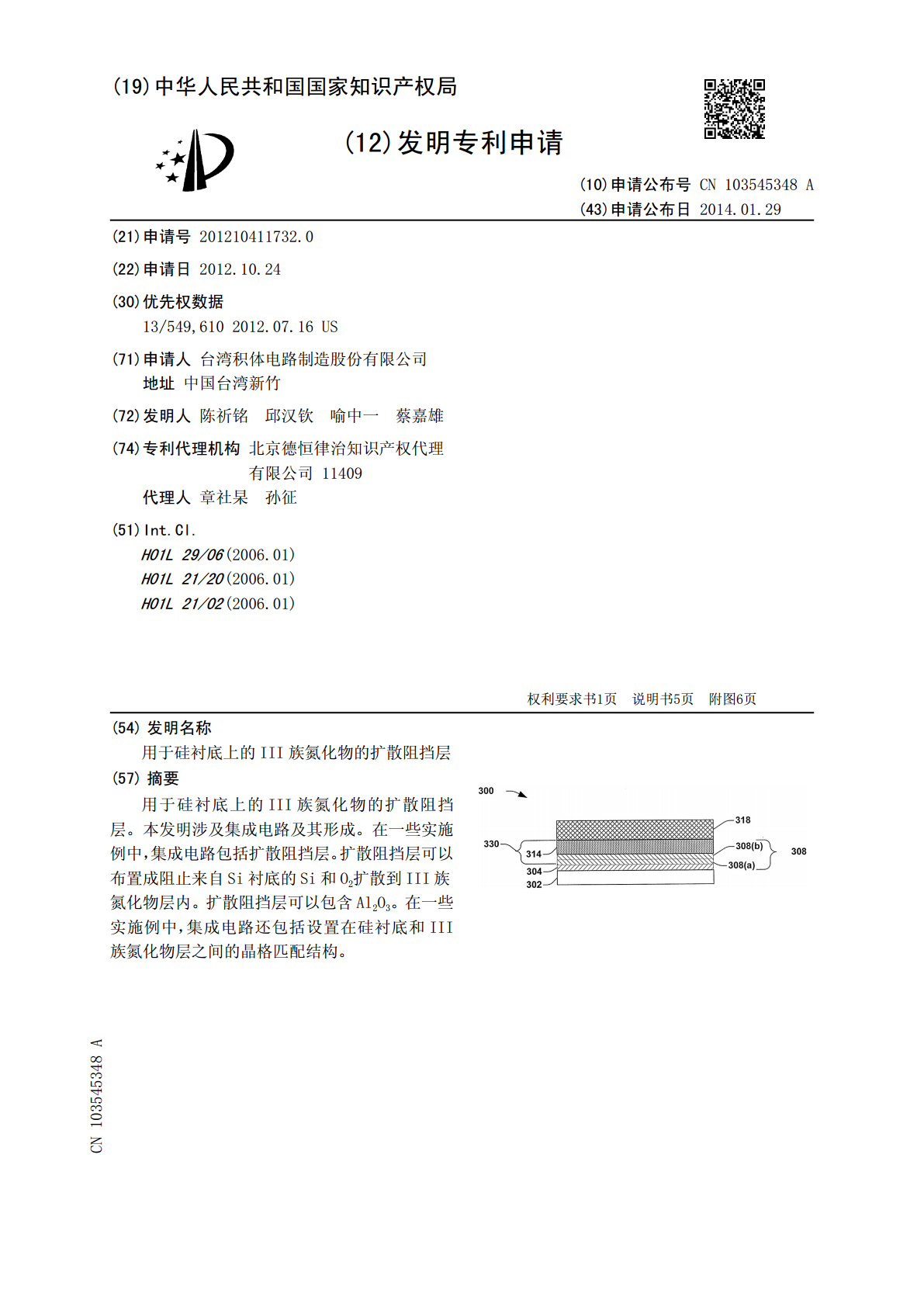

用于硅衬底上的III族氮化物的扩散阻挡层。本发明涉及集成电路及其形成。在一些实施例中,集成电路包括扩散阻挡层。扩散阻挡层可以布置成阻止来自Si衬底的Si和O2扩散到III族氮化物层内。扩散阻挡层可以包含Al2O3。在一些实施例中,集成电路还包括设置在硅衬底和III族氮化物层之间的晶格匹配结构。

对硅衬底上的III族氮化物的衬底击穿电压的改进.pdf

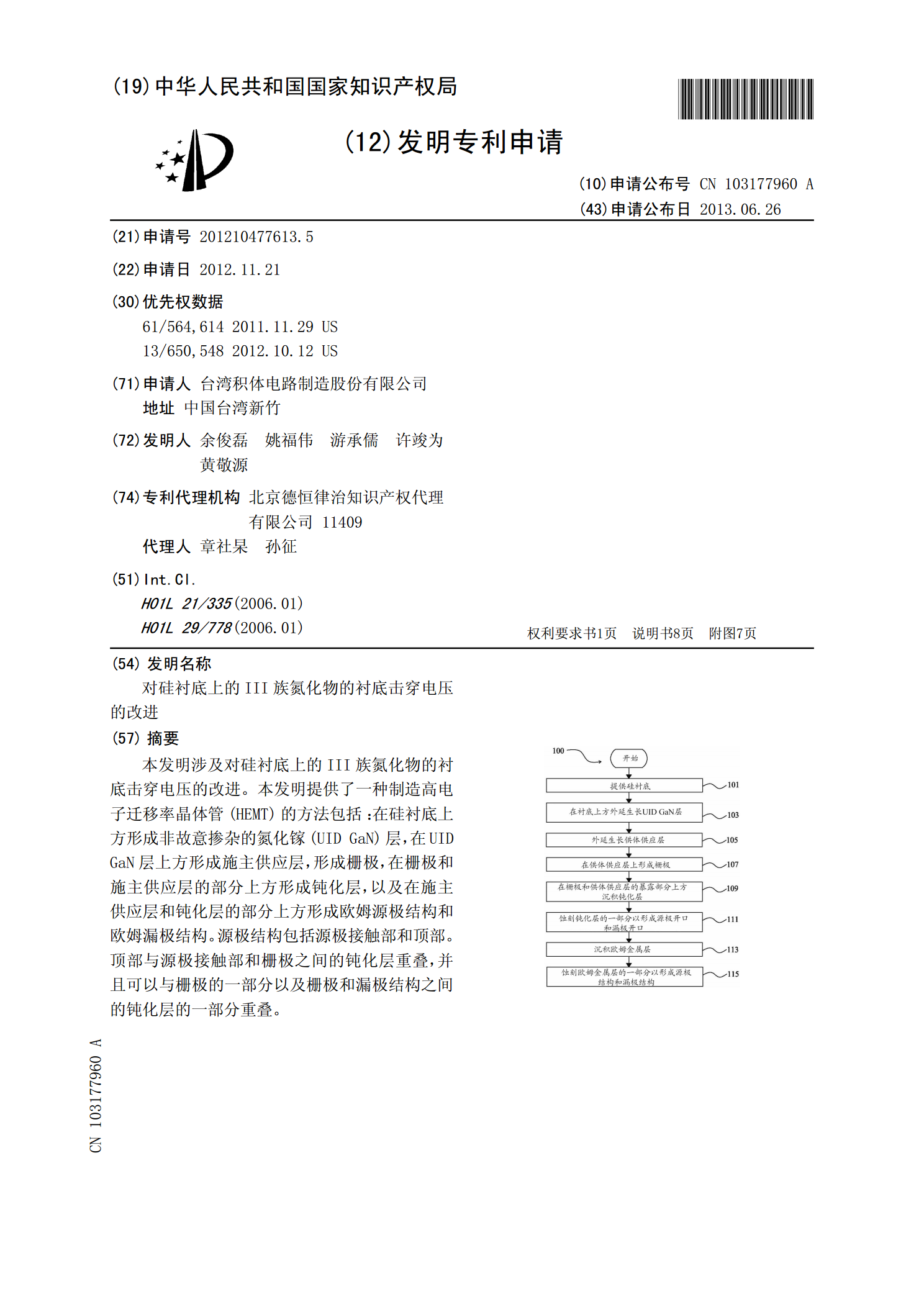

本发明涉及对硅衬底上的III族氮化物的衬底击穿电压的改进。本发明提供了一种制造高电子迁移率晶体管(HEMT)的方法包括:在硅衬底上方形成非故意掺杂的氮化镓(UID?GaN)层,在UID?GaN层上方形成施主供应层,形成栅极,在栅极和施主供应层的部分上方形成钝化层,以及在施主供应层和钝化层的部分上方形成欧姆源极结构和欧姆漏极结构。源极结构包括源极接触部和顶部。顶部与源极接触部和栅极之间的钝化层重叠,并且可以与栅极的一部分以及栅极和漏极结构之间的钝化层的一部分重叠。

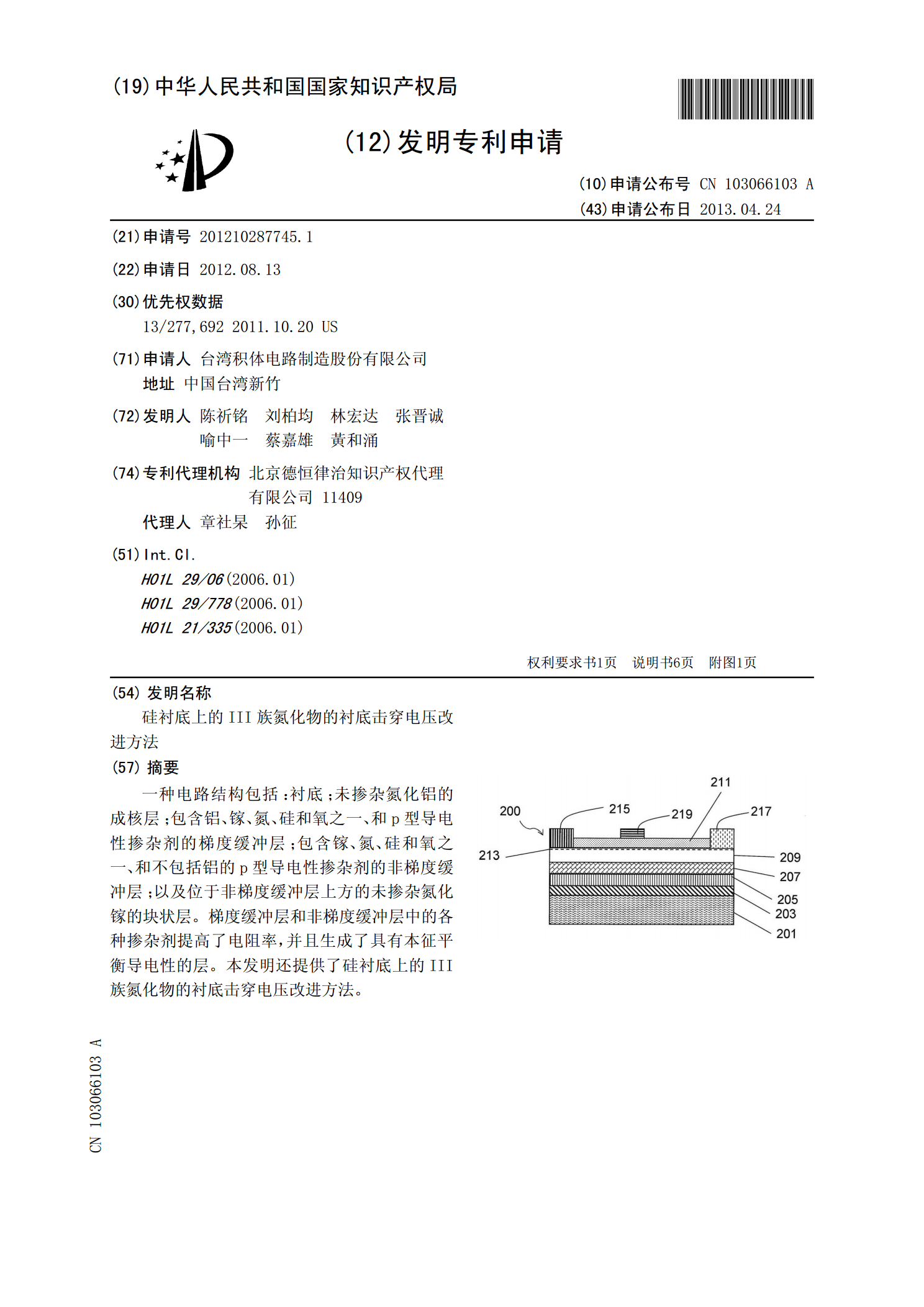

硅衬底上的III族氮化物的衬底击穿电压改进方法.pdf

一种电路结构包括:衬底;未掺杂氮化铝的成核层;包含铝、镓、氮、硅和氧之一、和p型导电性掺杂剂的梯度缓冲层;包含镓、氮、硅和氧之一、和不包括铝的p型导电性掺杂剂的非梯度缓冲层;以及位于非梯度缓冲层上方的未掺杂氮化镓的块状层。梯度缓冲层和非梯度缓冲层中的各种掺杂剂提高了电阻率,并且生成了具有本征平衡导电性的层。本发明还提供了硅衬底上的III族氮化物的衬底击穿电压改进方法。

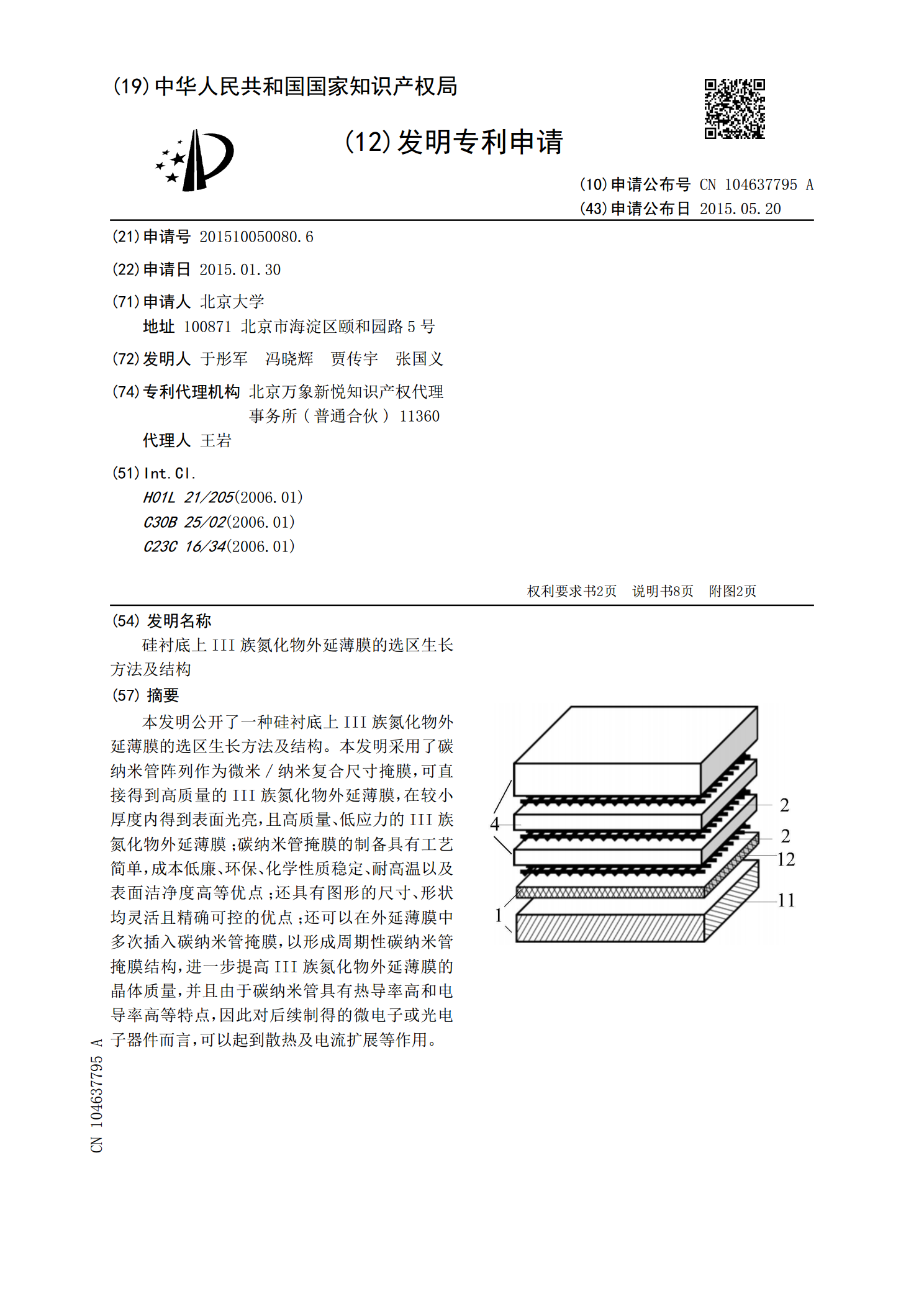

硅衬底上III族氮化物外延薄膜的选区生长方法及结构.pdf

本发明公开了一种硅衬底上III族氮化物外延薄膜的选区生长方法及结构。本发明采用了碳纳米管阵列作为微米/纳米复合尺寸掩膜,可直接得到高质量的III族氮化物外延薄膜,在较小厚度内得到表面光亮,且高质量、低应力的III族氮化物外延薄膜;碳纳米管掩膜的制备具有工艺简单,成本低廉、环保、化学性质稳定、耐高温以及表面洁净度高等优点;还具有图形的尺寸、形状均灵活且精确可控的优点;还可以在外延薄膜中多次插入碳纳米管掩膜,以形成周期性碳纳米管掩膜结构,进一步提高III族氮化物外延薄膜的晶体质量,并且由于碳纳米管具有热导率高

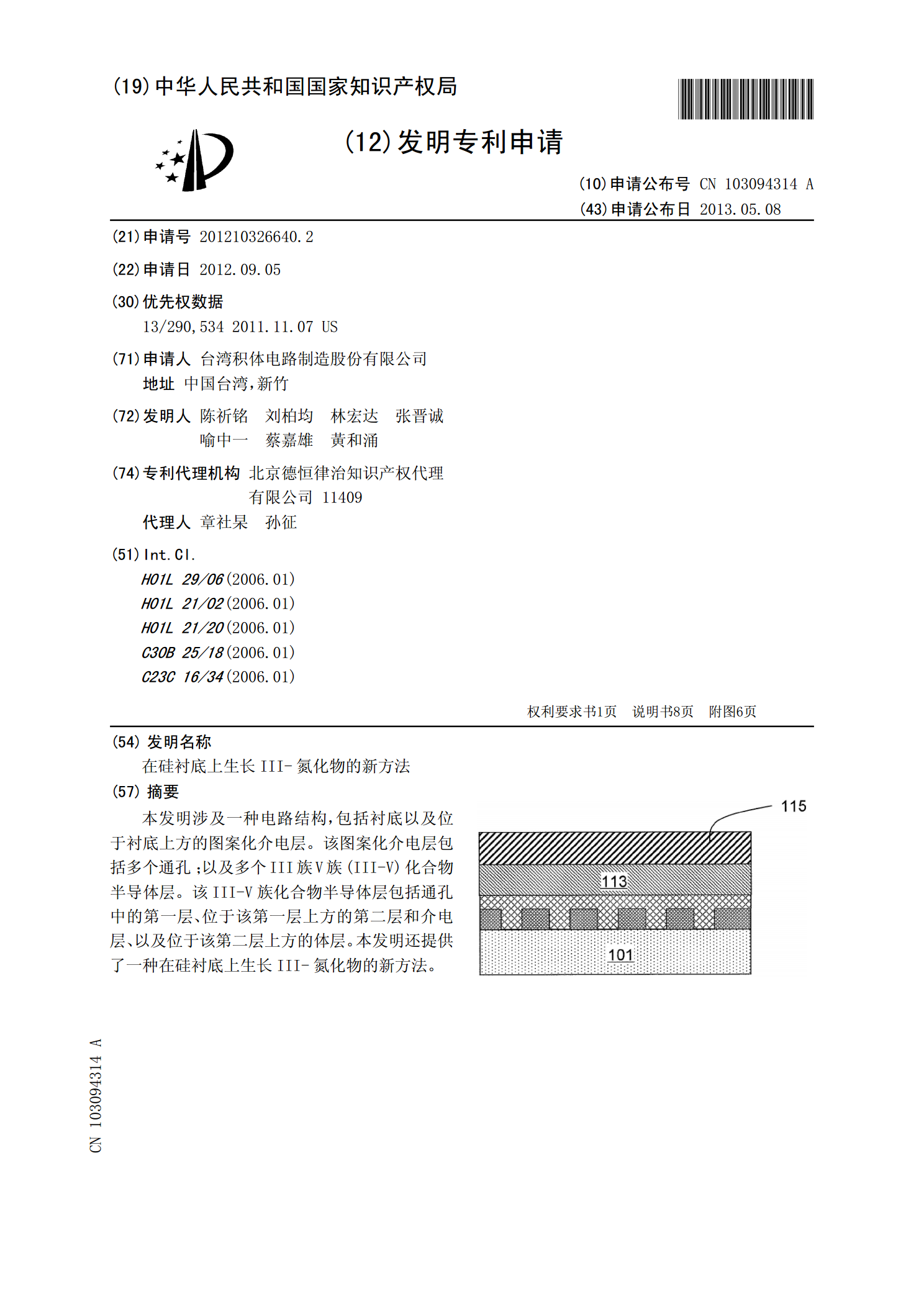

在硅衬底上生长III-氮化物的新方法.pdf

本发明涉及一种电路结构,包括衬底以及位于衬底上方的图案化介电层。该图案化介电层包括多个通孔;以及多个III族V族(III-V)化合物半导体层。该III-V族化合物半导体层包括通孔中的第一层、位于该第一层上方的第二层和介电层、以及位于该第二层上方的体层。本发明还提供了一种在硅衬底上生长III-氮化物的新方法。