外延结构、半导体器件及制备方法.pdf

努力****亚捷

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

外延结构、半导体器件及制备方法.pdf

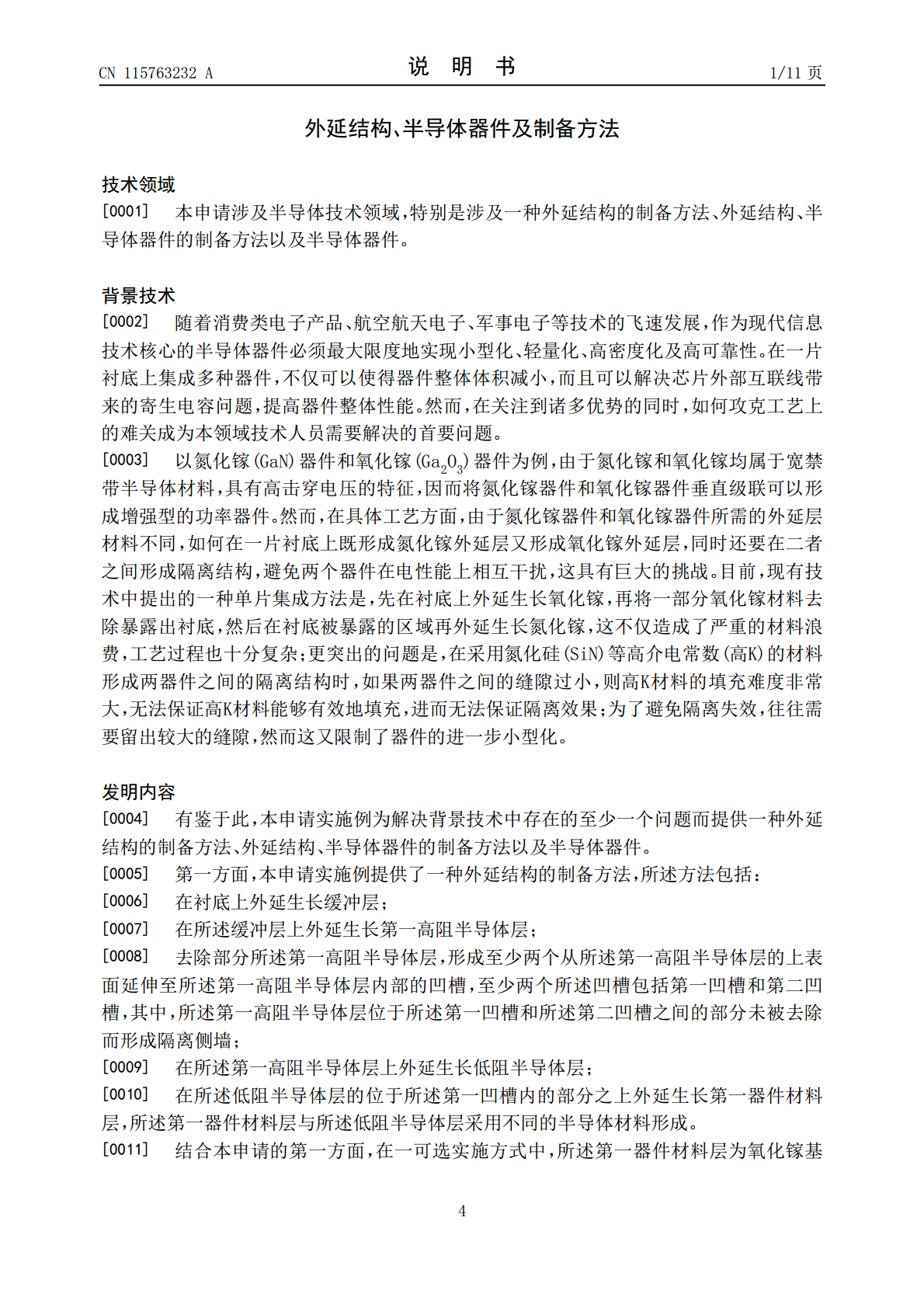

本申请实施例涉及一种外延结构的制备方法、外延结构、半导体器件的制备方法以及半导体器件,通过在衬底上外延生长缓冲层;在缓冲层上外延生长第一高阻半导体层;去除部分第一高阻半导体层,形成至少两个从第一高阻半导体层的上表面延伸至第一高阻半导体层内部的凹槽,至少两个凹槽包括第一凹槽和第二凹槽,其中,第一高阻半导体层位于第一凹槽和第二凹槽之间的部分未被去除而形成隔离侧墙;在第一高阻半导体层上外延生长低阻半导体层;在低阻半导体层的位于第一凹槽内的部分之上外延生长第一器件材料层,第一器件材料层与低阻半导体层采用不同的半导

外延结构及其制备方法、半导体器件及其制备方法.pdf

本发明实施例公开了一种外延结构及其制备方法、半导体器件及其制备方法,该外延结构包括:衬底;半导体层,位于衬底一侧,半导体层远离衬底一侧的表面为金属极性面;氮极性面帽层,位于半导体层远离衬底的一侧。具有金属极性面的半导体层和氮极性面帽层形成复合极性外延结构,形成半导体器件时,具有强负电性的氮极性面帽层,在常温下即可与源极和漏极形成良好的欧姆接触,无需高温处理,能够降低工艺难度,半导体层可作为氮极性面帽层的湿法腐蚀自停止层,稳定阈值电压同时可提高跨导,从而提高器件性能。

异质外延半导体器件和制造异质外延半导体器件的方法.pdf

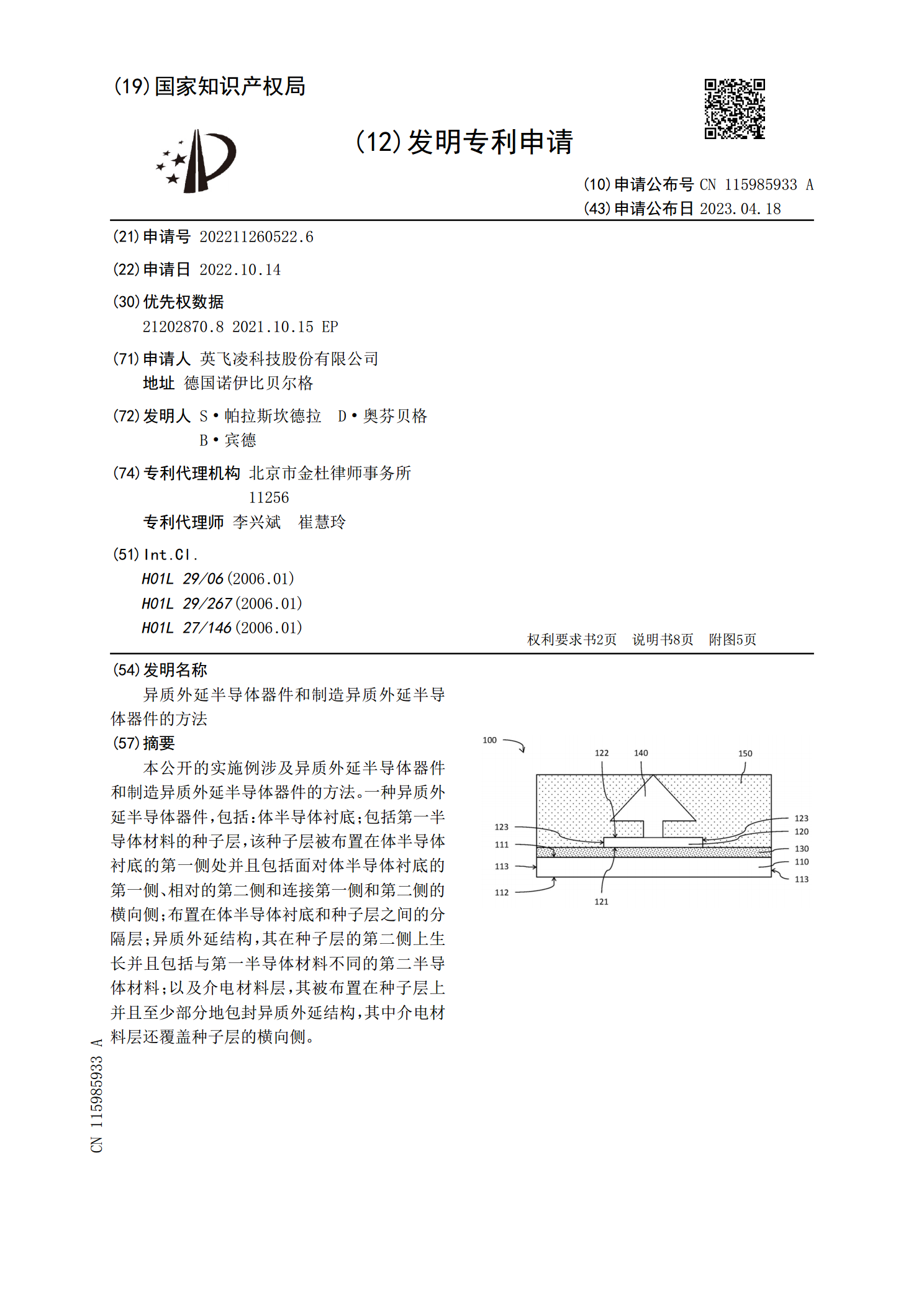

本公开的实施例涉及异质外延半导体器件和制造异质外延半导体器件的方法。一种异质外延半导体器件,包括:体半导体衬底;包括第一半导体材料的种子层,该种子层被布置在体半导体衬底的第一侧处并且包括面对体半导体衬底的第一侧、相对的第二侧和连接第一侧和第二侧的横向侧;布置在体半导体衬底和种子层之间的分隔层;异质外延结构,其在种子层的第二侧上生长并且包括与第一半导体材料不同的第二半导体材料;以及介电材料层,其被布置在种子层上并且至少部分地包封异质外延结构,其中介电材料层还覆盖种子层的横向侧。

异质外延半导体器件和制造异质外延半导体器件的方法.pdf

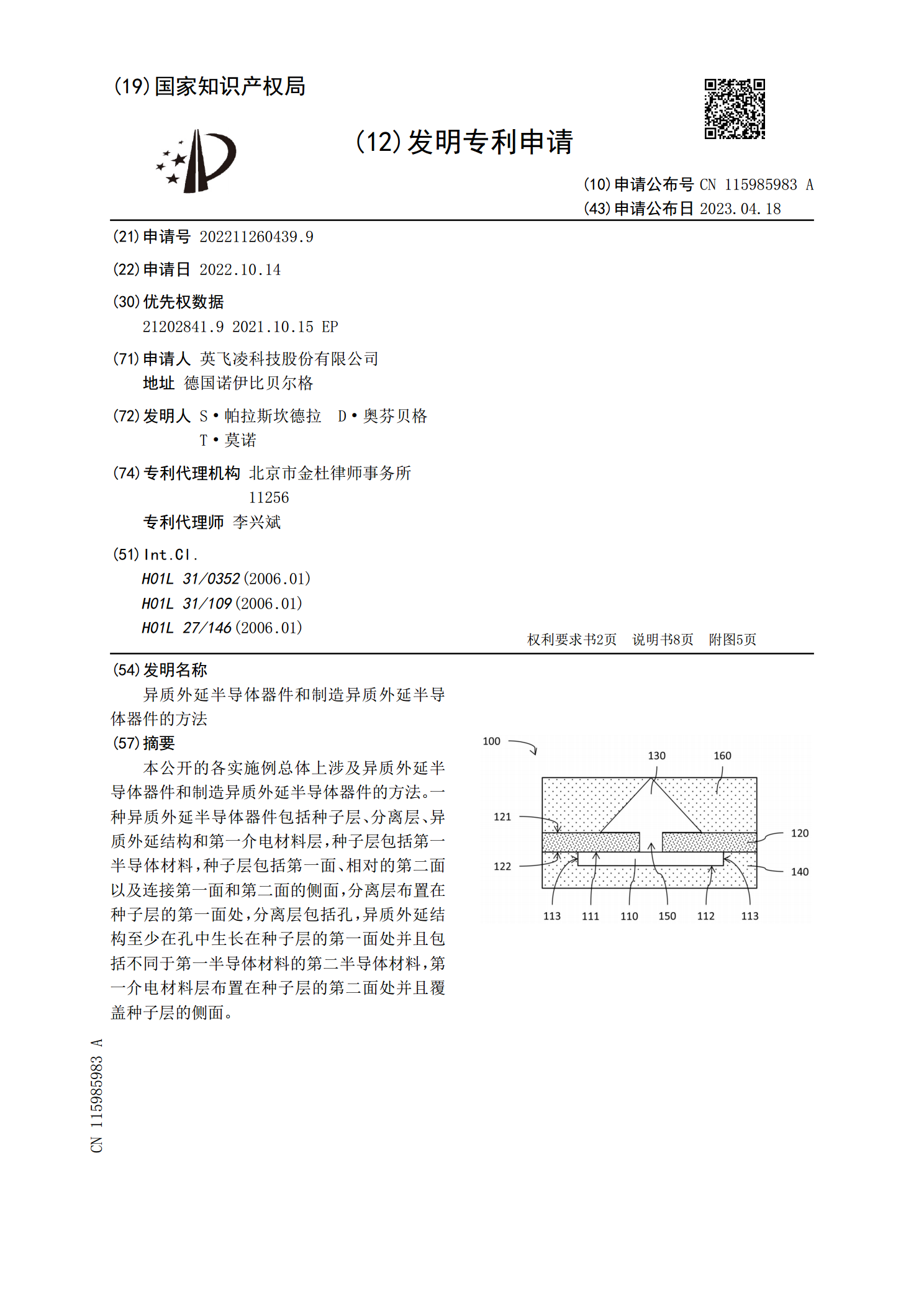

本公开的各实施例总体上涉及异质外延半导体器件和制造异质外延半导体器件的方法。一种异质外延半导体器件包括种子层、分离层、异质外延结构和第一介电材料层,种子层包括第一半导体材料,种子层包括第一面、相对的第二面以及连接第一面和第二面的侧面,分离层布置在种子层的第一面处,分离层包括孔,异质外延结构至少在孔中生长在种子层的第一面处并且包括不同于第一半导体材料的第二半导体材料,第一介电材料层布置在种子层的第二面处并且覆盖种子层的侧面。

一种半导体外延结构及其制备方法、光电器件.pdf

本发明提供一种半导体外延结构及其制备方法、光电器件。所述半导体外延结构包括第一半导体层、有源层、抗静电层及第二半导体层。第一半导体层具有第一导电类型;有源层设于所述第一半导体层的一侧;抗静电层设于所述有源层背离所述第一半导体层的一侧,抗静电层包括AlN层及设于所述AlN层上的AlxInyGa1?x?yN(0≦x,y≦1)层;所述AlN层更靠近所述有源层设置;第二半导体层设于抗静电层背离所述有源层的一侧,所述第二导电层具有第二导电类型。上述半导体外延结构,抗静电层中的AlN层能够有效抑制有源层中电子溢流的同