远程供电的非接触式卡.pdf

含秀****66

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

远程供电的非接触式卡.pdf

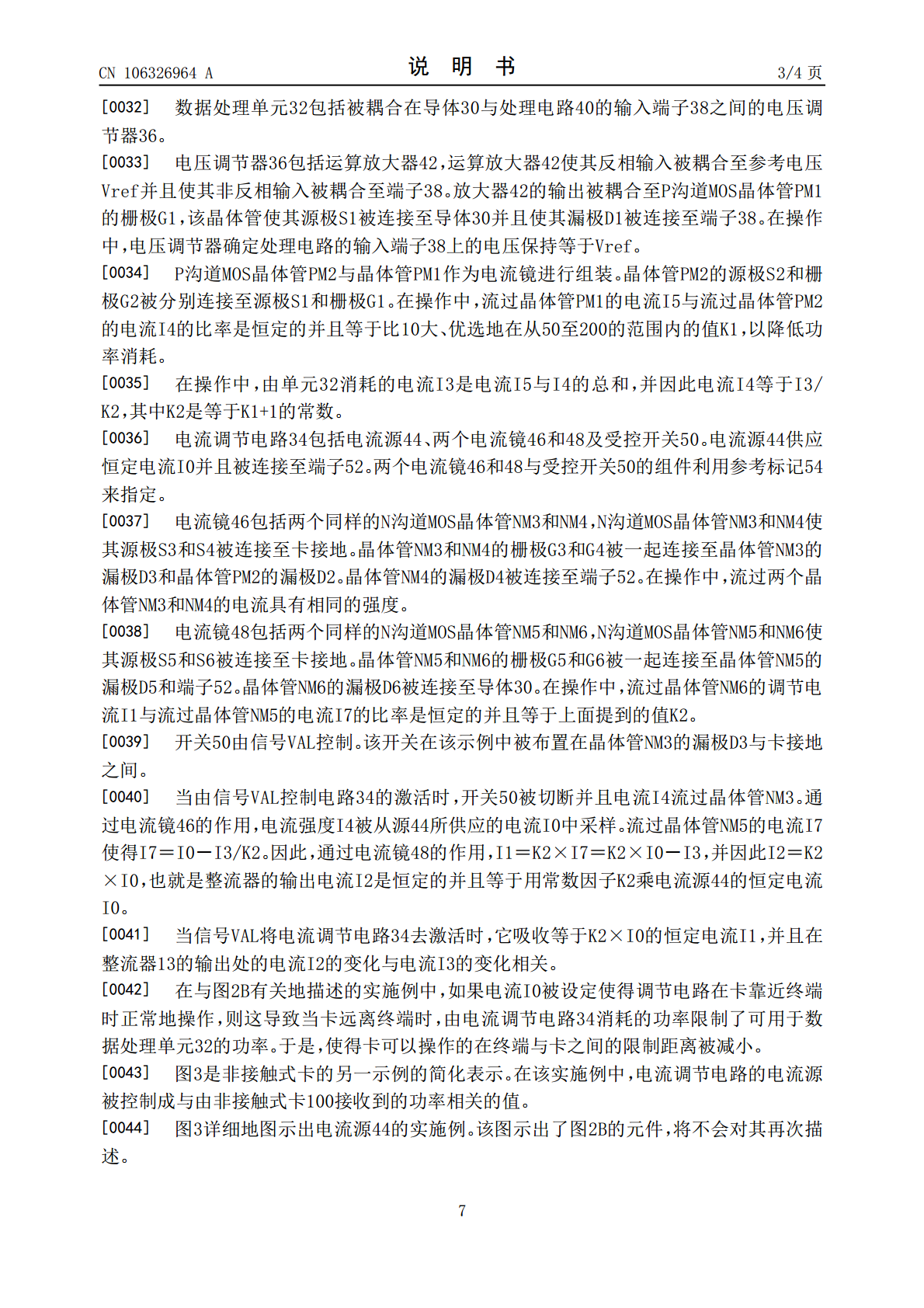

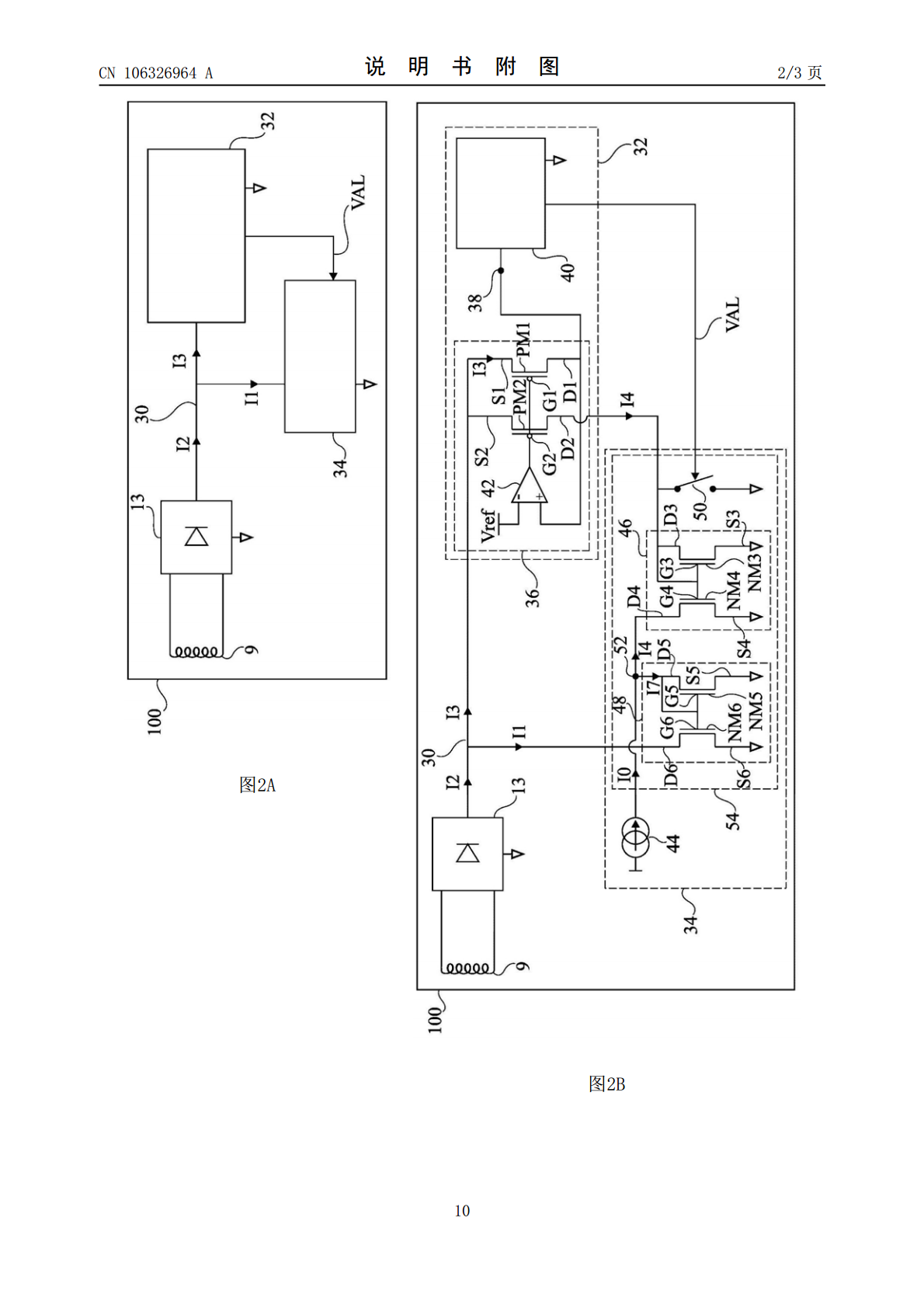

本公开涉及远程供电的非接触式卡。该非接触式卡由被连接至整流器的输入的天线供电。整流器的输出被耦合至消耗输出自整流器的第一电流的处理单元。电流调节电路被连接至整流器的输出。电流调节电路操作以吸收来自整流器的输出的第二电流使得第一电流和第二电流的总和是恒定电流。

非接触式供电方法和非接触式供电系统.pdf

本发明涉及非接触式供电方法和非接触式供电系统。旨在于提供一种安全的非接触式充电环境,使得能够在开始充电之前找到遗留在车辆中的电子装置并防止电子装置由于在借助于电磁耦合的充电期间产生的电磁波而损坏的麻烦。预先执行以下处理:基于由留在车辆内的电子装置发出的无线通信信息进行检查以查看到电子装置遗留在车辆内。当检测到电子装置遗留时,根据所检测到的电子装置的可允许电流来控制充电电流值,或者产生报警以通知电子装置遗留。

非接触式IC卡技术.pptx

非接触式IC卡技术提纲为什么要使用非接触式IC卡?什么是非接触式IC卡?ContactlessICC非接触式IC卡系统构成非接触式IC卡的基本构成非接触式IC卡读写器的构成非接触式IC卡的特点非接触式IC卡的分类EMID厚卡特点频段非接触式IC卡的国际标准ISO/IEC14443国际标准现阶段ISO/IEC14443(草案)主要有两个体系并存:ISO/IEC14443-TypeA、ISO/IEC14443-TypeB。TypeA:以PHILIPS公司为代表,包括SIEMENS、HITACHI、GEMPLU

非接触式IC卡参数.docx

非接触式IC卡又称射频卡,由IC芯片、感应天线组成,封装在一个标准的PVC卡片内,芯片及天线无任何外露部分。是世界上最近几年发展起来的一项新技术,它成功的将射频识别技术和IC卡技术结合起来,结束了无源(卡中无电源)和免接触这一难题,是电子器件领域的一大突破.卡片在一定距离范围(通常为5—10mm)靠近读写器表面,通过无线电波的传递来完成数据的读写操作。1.非接触性IC卡与读卡器之间通过无线电波来完成读写操作。二者之间的通讯频为13.56MHZ。非接触性IC卡本身是无源卡,当读写器对卡进行读写操作是,读写器

磁浮列车非接触式供电技术.pptx

磁浮列车非接触式供电技术目录添加章节标题磁浮列车非接触式供电技术的原理磁浮列车的定义非接触式供电技术的定义磁浮列车非接触式供电技术的原理磁浮列车非接触式供电技术的优势减少接触摩擦,提高列车运行稳定性降低维护成本提高列车的运行效率节能环保磁浮列车非接触式供电技术的应用场景城市轨道交通高速铁路旅游景区交通其他应用场景磁浮列车非接触式供电技术的发展趋势技术创新与突破降低成本,提高经济效益拓展应用领域,扩大市场规模加强国际合作与交流,推动技术进步磁浮列车非接触式供电技术的挑战与对策技术成熟度与可靠性问题基础设施建