半导体封装件及其形成方法.pdf

子璇****君淑

亲,该文档总共37页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体封装件及其形成方法.pdf

本发明的实施例提供了半导体封装件及其形成方法。该半导体封装件包括具有第一衬底的第一中介层、在第一衬底的第一侧上方的第一再分布结构、以及在第一再分布结构上方并且靠近第一中介层的第一侧的第一波导,其中第一再分布结构位于第一衬底与第一波导之间。半导体封装件还包括附接到第一中介层的第一侧的光子封装件,其中光子封装件包括:电子管芯,以及具有多个介电层和在多个介电层中的一个中的第二波导的光子管芯,其中光子管芯的第一侧附接到电子管芯,并且光子管芯的相对的第二侧附接到第一中介层的第一侧,其中第二波导靠近光子管芯的第二侧。

半导体封装件及其形成方法.pdf

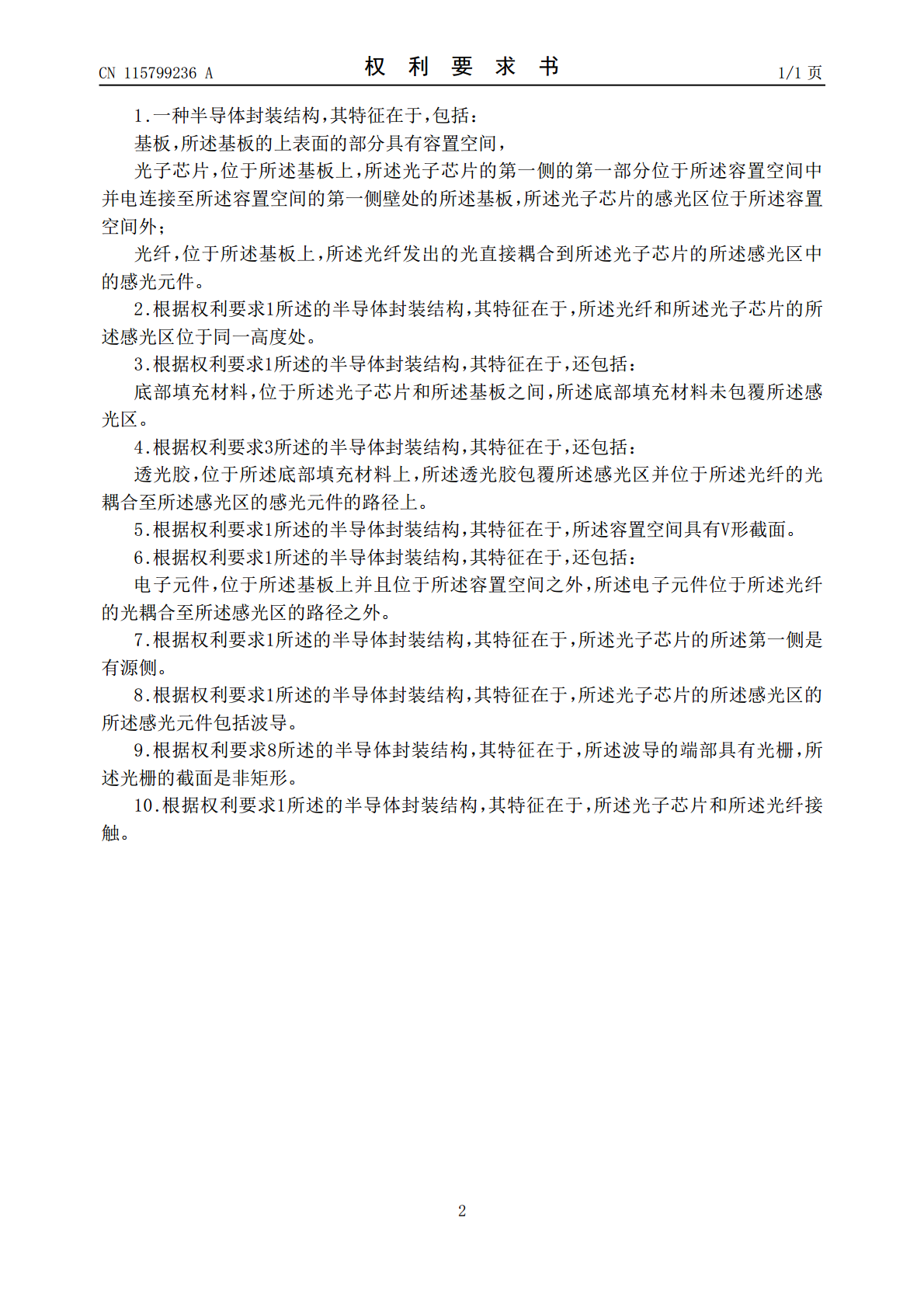

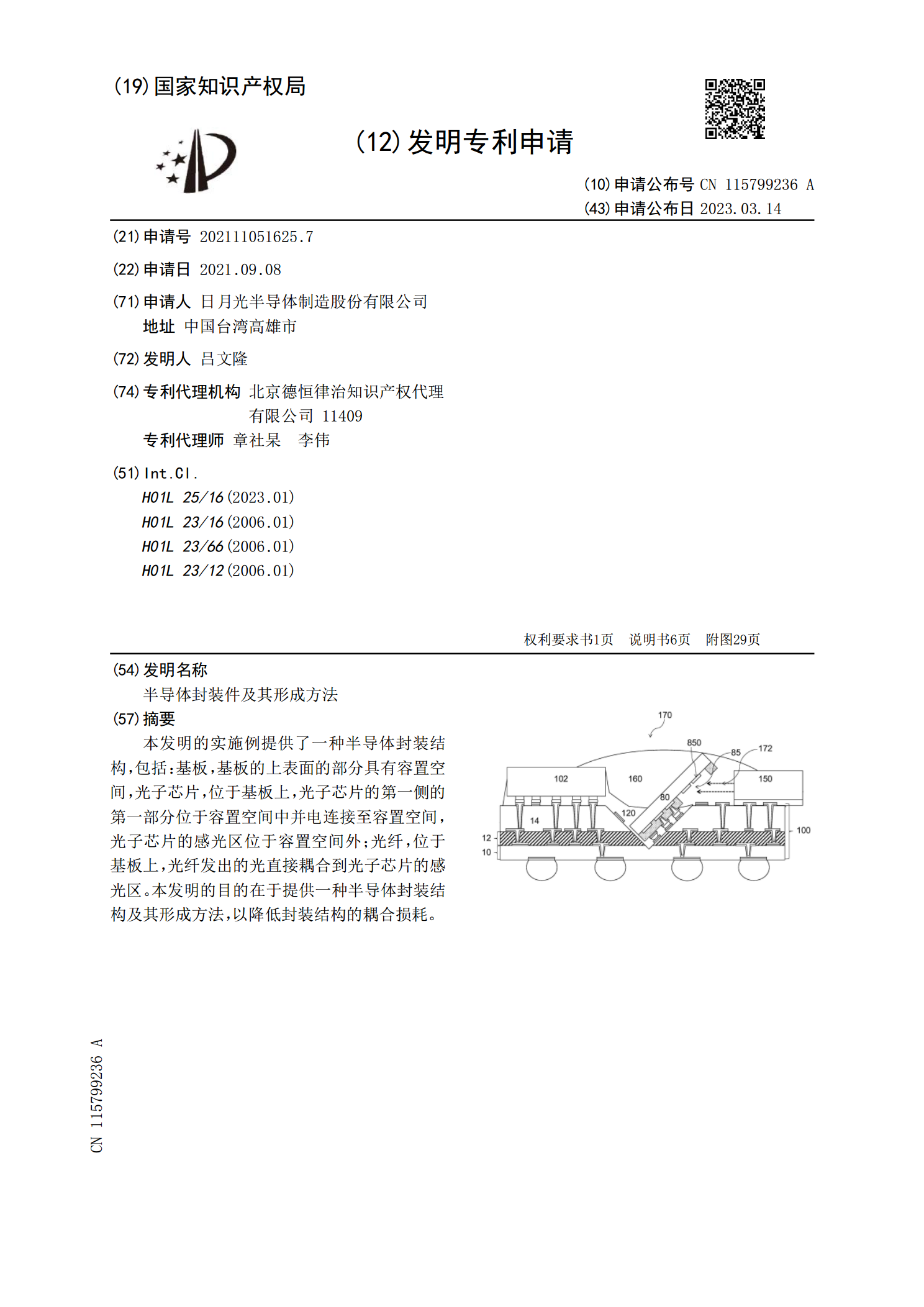

本发明的实施例提供了一种半导体封装结构,包括:基板,基板的上表面的部分具有容置空间,光子芯片,位于基板上,光子芯片的第一侧的第一部分位于容置空间中并电连接至容置空间,光子芯片的感光区位于容置空间外;光纤,位于基板上,光纤发出的光直接耦合到光子芯片的感光区。本发明的目的在于提供一种半导体封装结构及其形成方法,以降低封装结构的耦合损耗。

半导体封装件及其形成方法.pdf

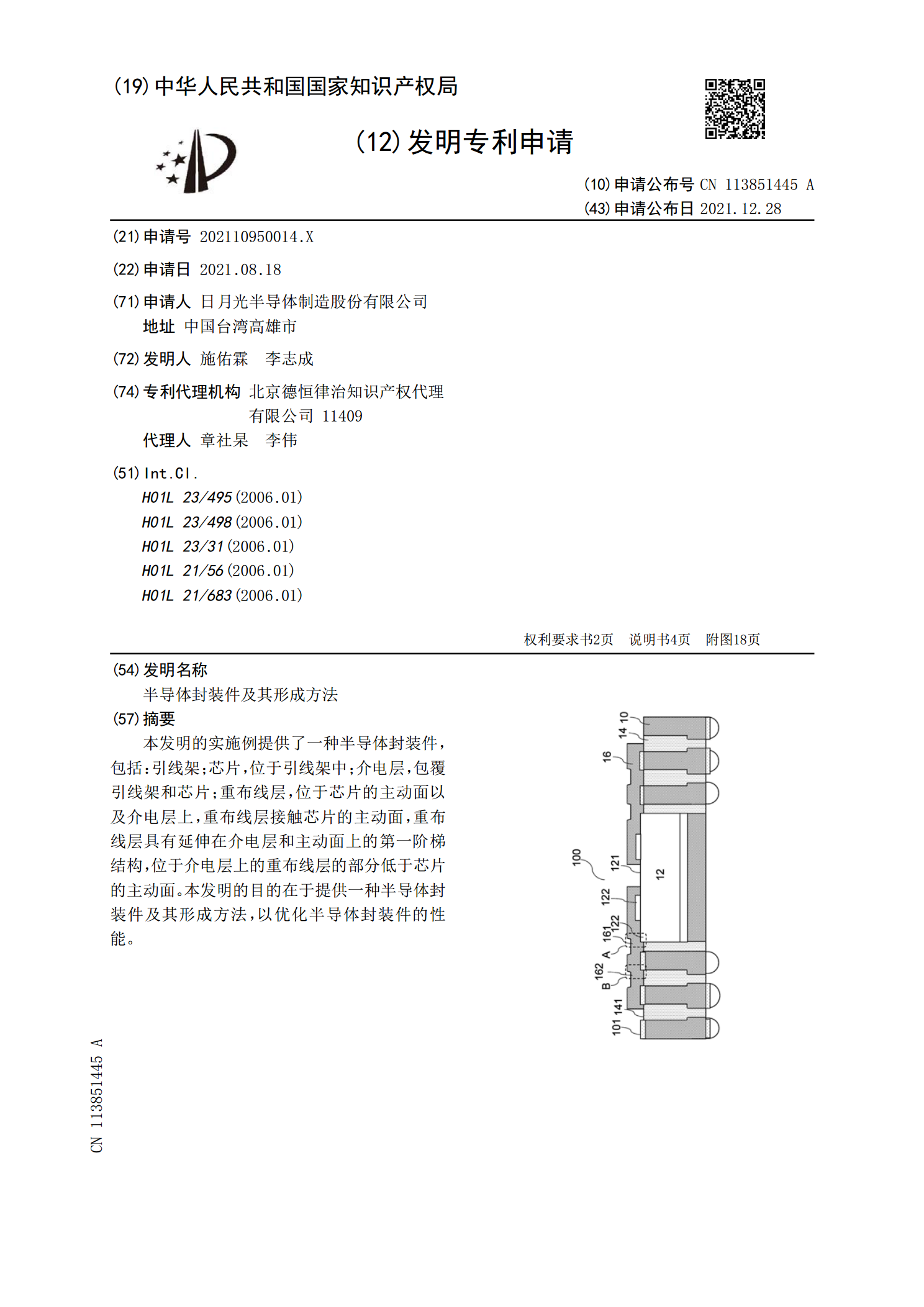

本发明的实施例提供了一种半导体封装件,包括:引线架;芯片,位于引线架中;介电层,包覆引线架和芯片;重布线层,位于芯片的主动面以及介电层上,重布线层接触芯片的主动面,重布线层具有延伸在介电层和主动面上的第一阶梯结构,位于介电层上的重布线层的部分低于芯片的主动面。本发明的目的在于提供一种半导体封装件及其形成方法,以优化半导体封装件的性能。

半导体封装件及其形成方法.pdf

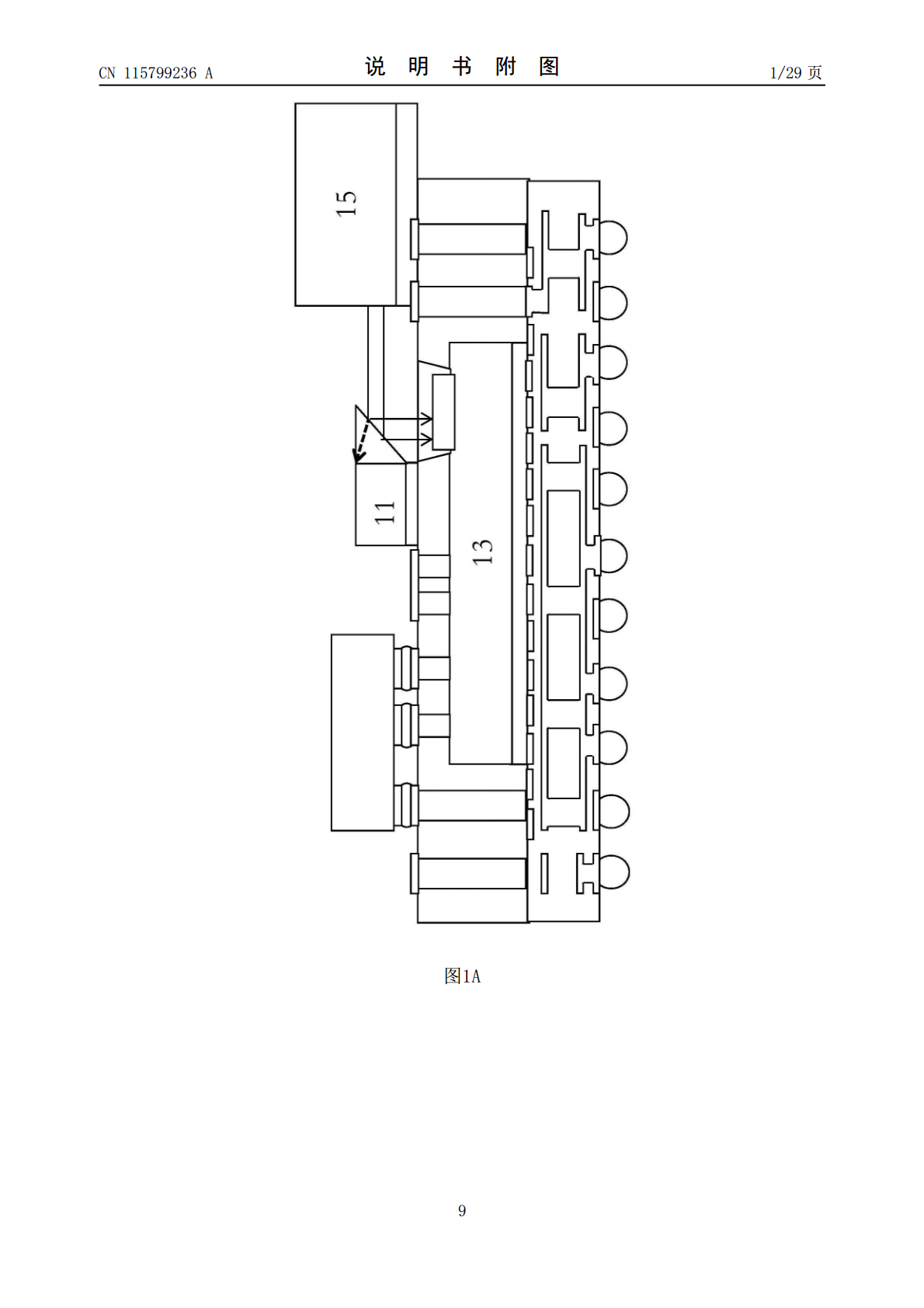

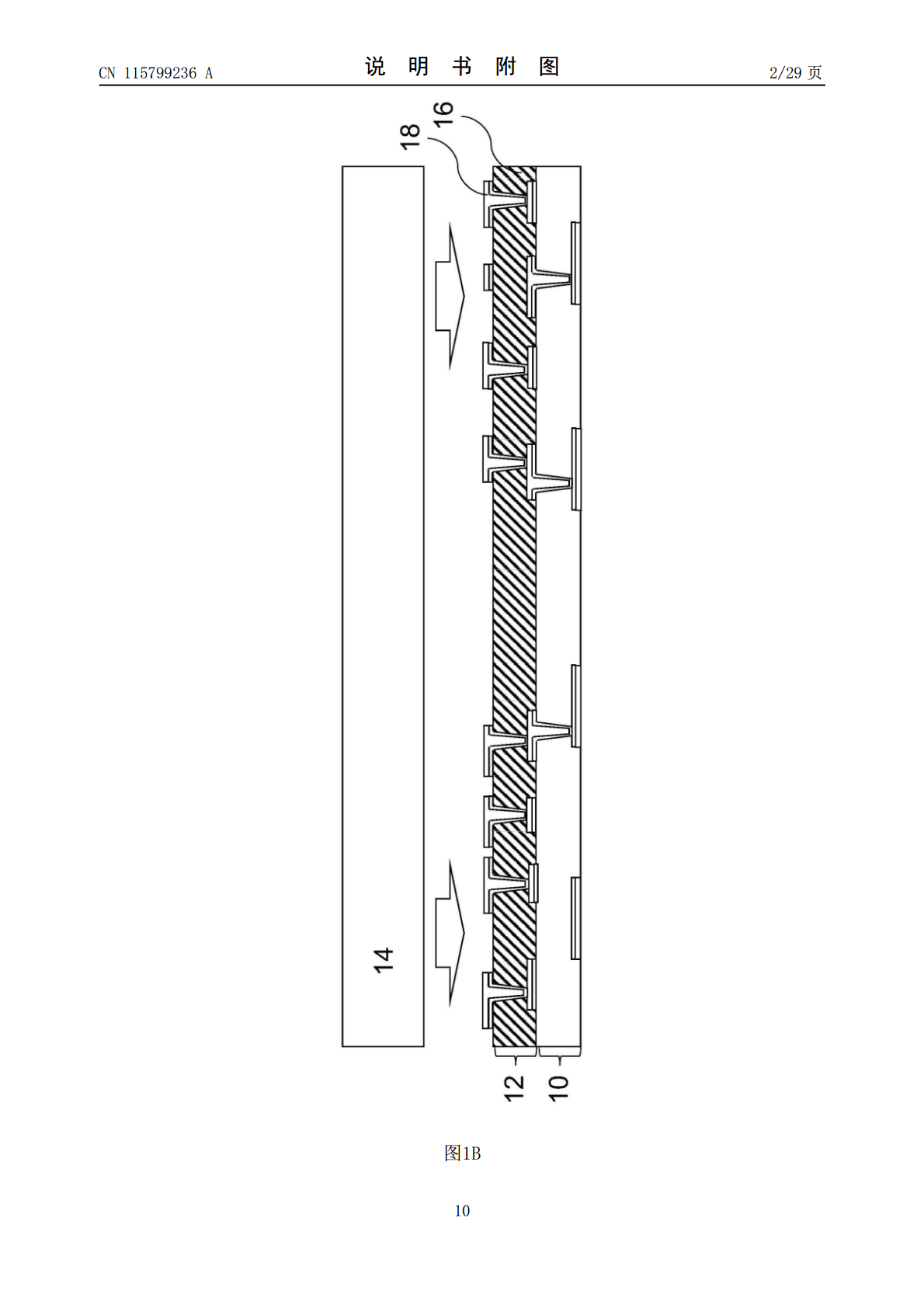

本发明提供了一种形成半导体封装件的方法,包括:提供中介层,中介层上设置有复数个电子元件;在中介层的上表面上进行第一次模制,以形成包覆复数个电子元件的第一模制化合物;在中介层的下表面上设置复数个第一焊球;在中介层的下表面上进行第二次模制,以形成与中介层的下表面接触的第二模制化合物。本发明的目的在于提供一种半导体封装件及其形成方法,以优化半导体封装件的性能。

半导体封装件及其形成方法.pdf

提供了半导体封装件及其形成方法。半导体封装件包括封装衬底和安装在封装衬底的表面上的半导体器件。第一环设置在封装衬底的表面上方并围绕半导体器件。第二环设置在第一环的顶面上方。而且,第一环的顶面和第二环的底面上分别形成突出部分和匹配的凹进部分。突出部分延伸至凹进部分中并与凹进部分啮合,以将第一环与第二环连接。粘合层设置在封装衬底的表面与第一环的底面之间,用于将第一环与上面的第二环附接至封装衬底。