半导体器件及其制造方法.pdf

是向****23

亲,该文档总共60页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体器件及其制造方法.pdf

一种制造半导体器件的方法,包括:在基板上形成目标层,在目标层上形成均匀间隔的多个参考图案;在参考图案的侧表面上形成多个间隔物;在间隔物之间留有的空间中形成多个填充图案;通过在多个填充图案的一部分上执行第一表面处理,形成表面改性的填充图案;通过在多个参考图案的一部分上执行第二表面处理,形成表面改性的参考图案;以及去除多个填充图案和多个参考图案并在目标层上留下表面改性的填充图案和表面改性的参考图案。

半导体器件及其制造方法.pdf

本发明提供一种制造半导体器件的方法,其中能够有效地生长具有许多对量子阱的多量子阱结构并同时确保优异的晶体品质。本发明还提供了通过这种方法制造的半导体器件。本发明制造半导体器件的方法包括形成具有50对以上由III-V族化合物半导体构成的量子阱的多量子阱结构(3)的步骤。在所述形成多量子阱结构(3)的步骤中,通过全金属有机气相淀积法(全金属有机MOVPE法)来形成所述多量子阱结构。

半导体器件及其制造方法.pdf

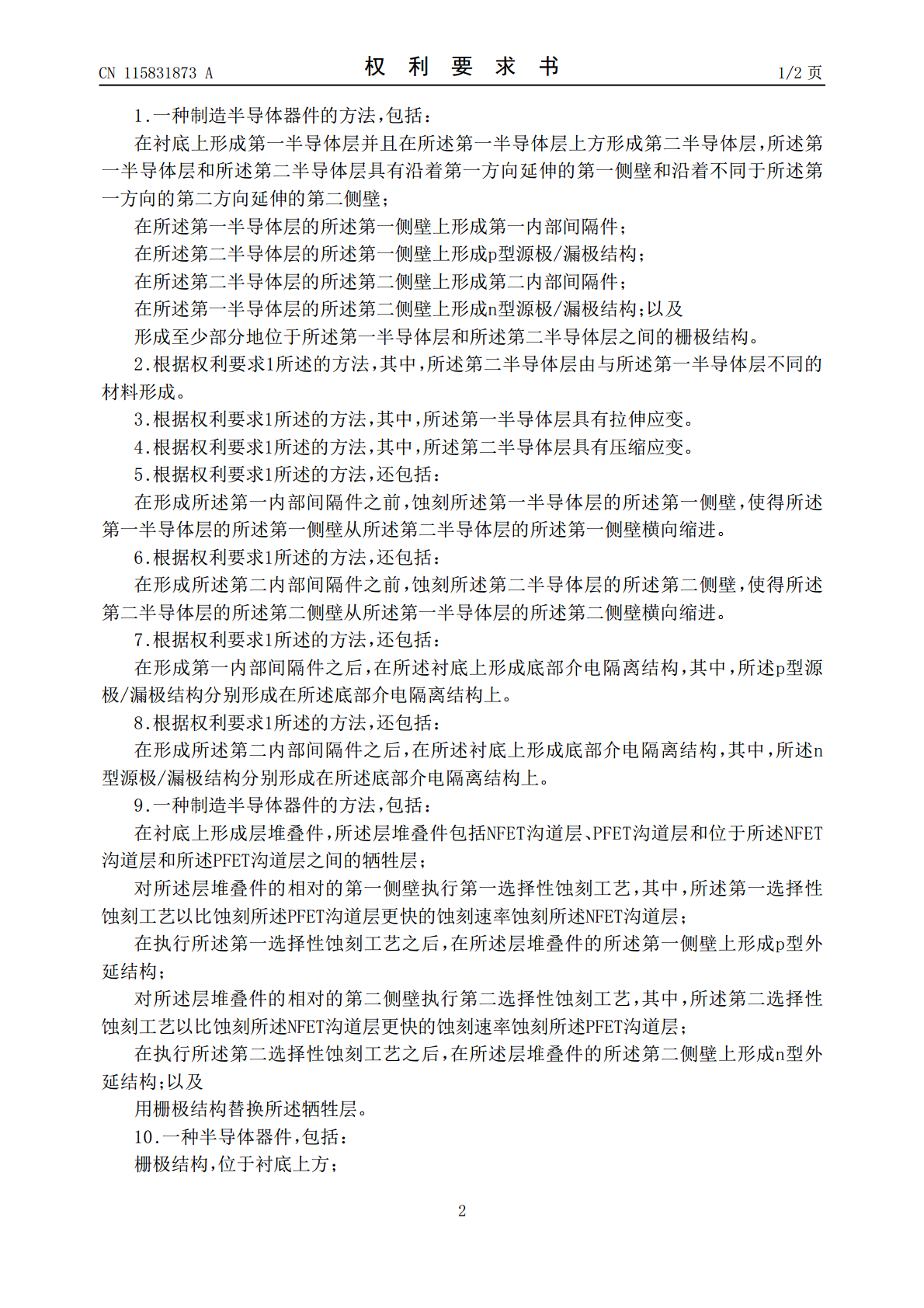

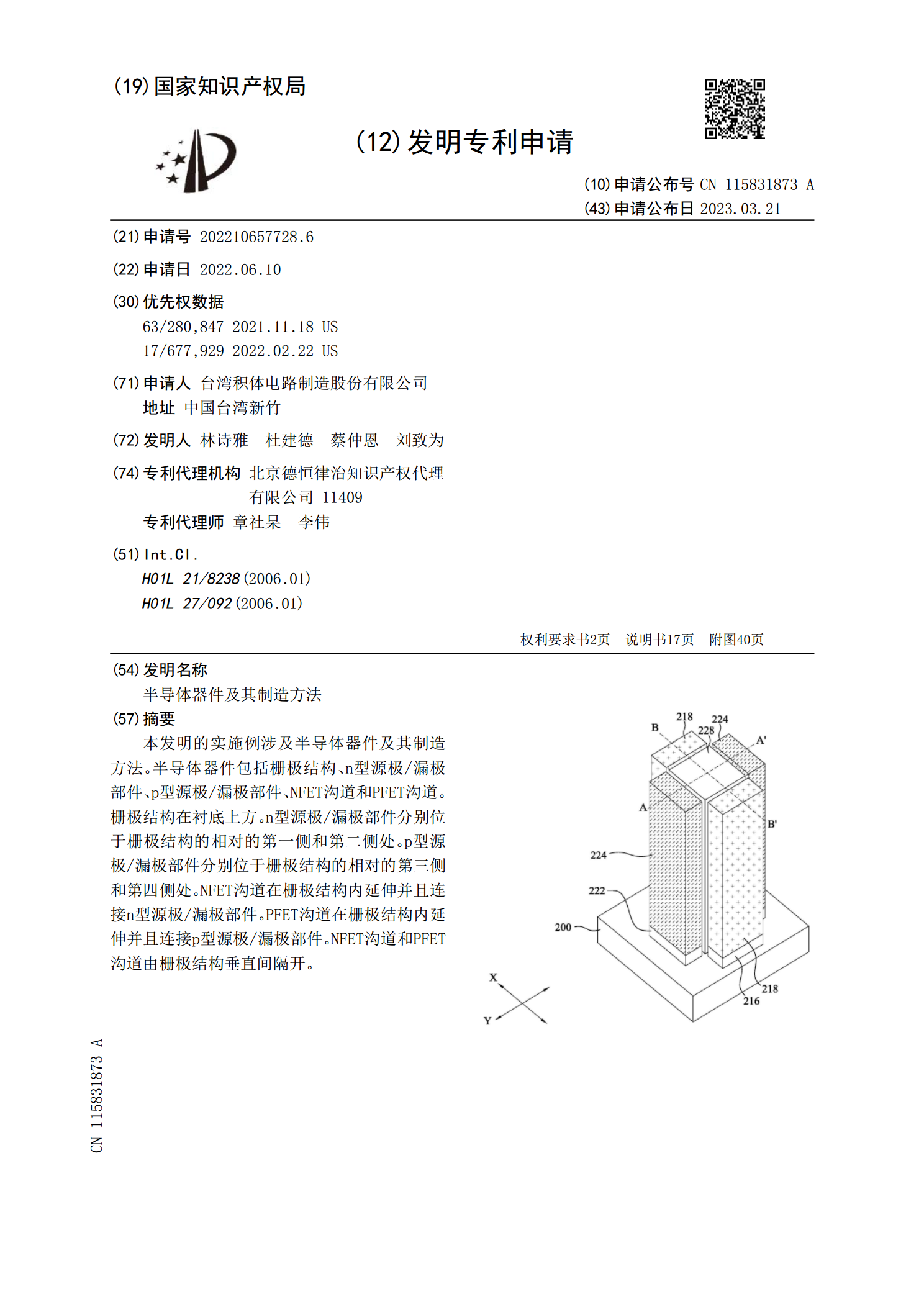

本发明的实施例涉及半导体器件及其制造方法。半导体器件包括栅极结构、n型源极/漏极部件、p型源极/漏极部件、NFET沟道和PFET沟道。栅极结构在衬底上方。n型源极/漏极部件分别位于栅极结构的相对的第一侧和第二侧处。p型源极/漏极部件分别位于栅极结构的相对的第三侧和第四侧处。NFET沟道在栅极结构内延伸并且连接n型源极/漏极部件。PFET沟道在栅极结构内延伸并且连接p型源极/漏极部件。NFET沟道和PFET沟道由栅极结构垂直间隔开。

半导体器件及其制造方法.pdf

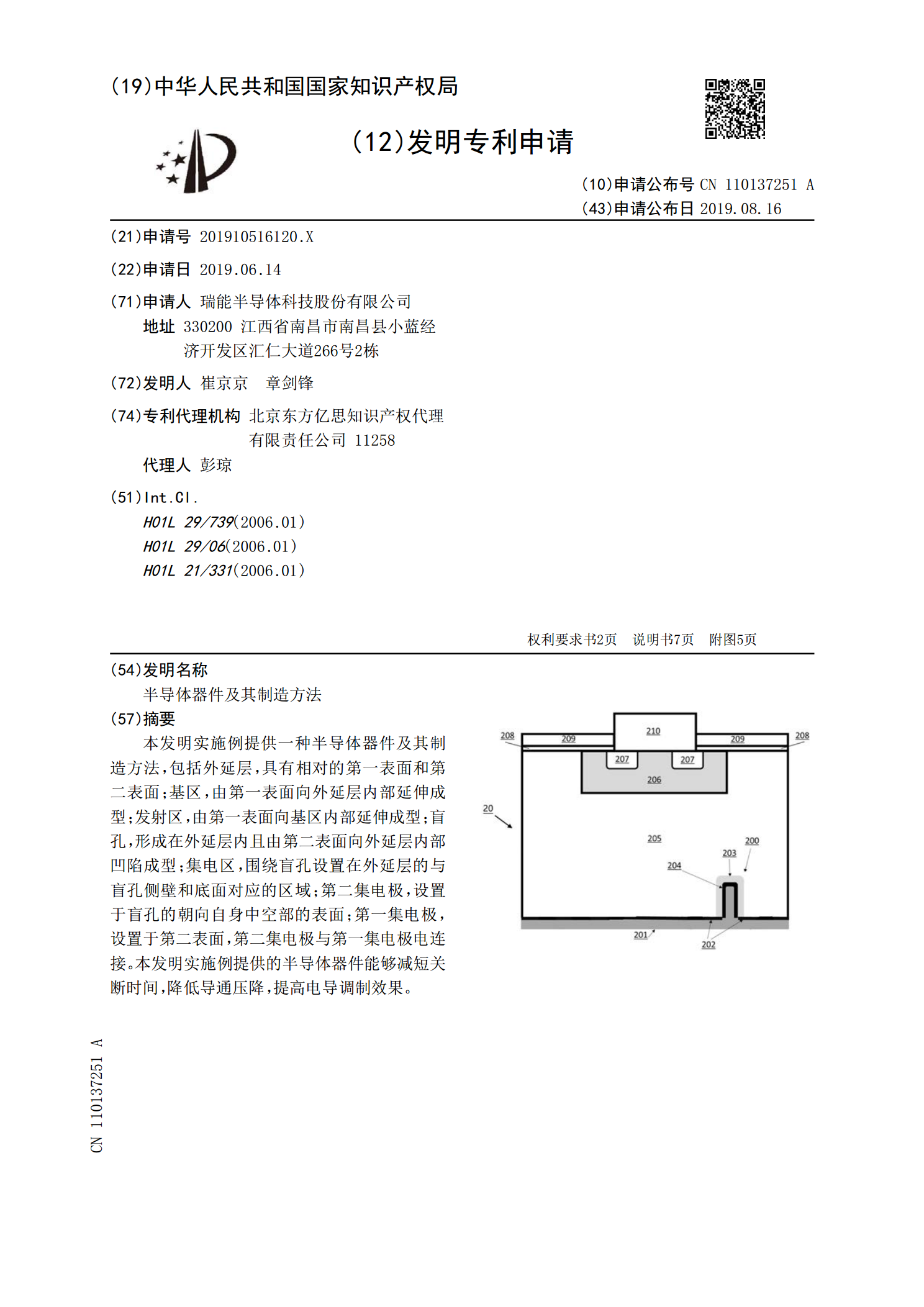

本发明实施例提供一种半导体器件及其制造方法,包括外延层,具有相对的第一表面和第二表面;基区,由第一表面向外延层内部延伸成型;发射区,由第一表面向基区内部延伸成型;盲孔,形成在外延层内且由第二表面向外延层内部凹陷成型;集电区,围绕盲孔设置在外延层的与盲孔侧壁和底面对应的区域;第二集电极,设置于盲孔的朝向自身中空部的表面;第一集电极,设置于第二表面,第二集电极与第一集电极电连接。本发明实施例提供的半导体器件能够减短关断时间,降低导通压降,提高电导调制效果。

半导体器件及其制造方法.pdf

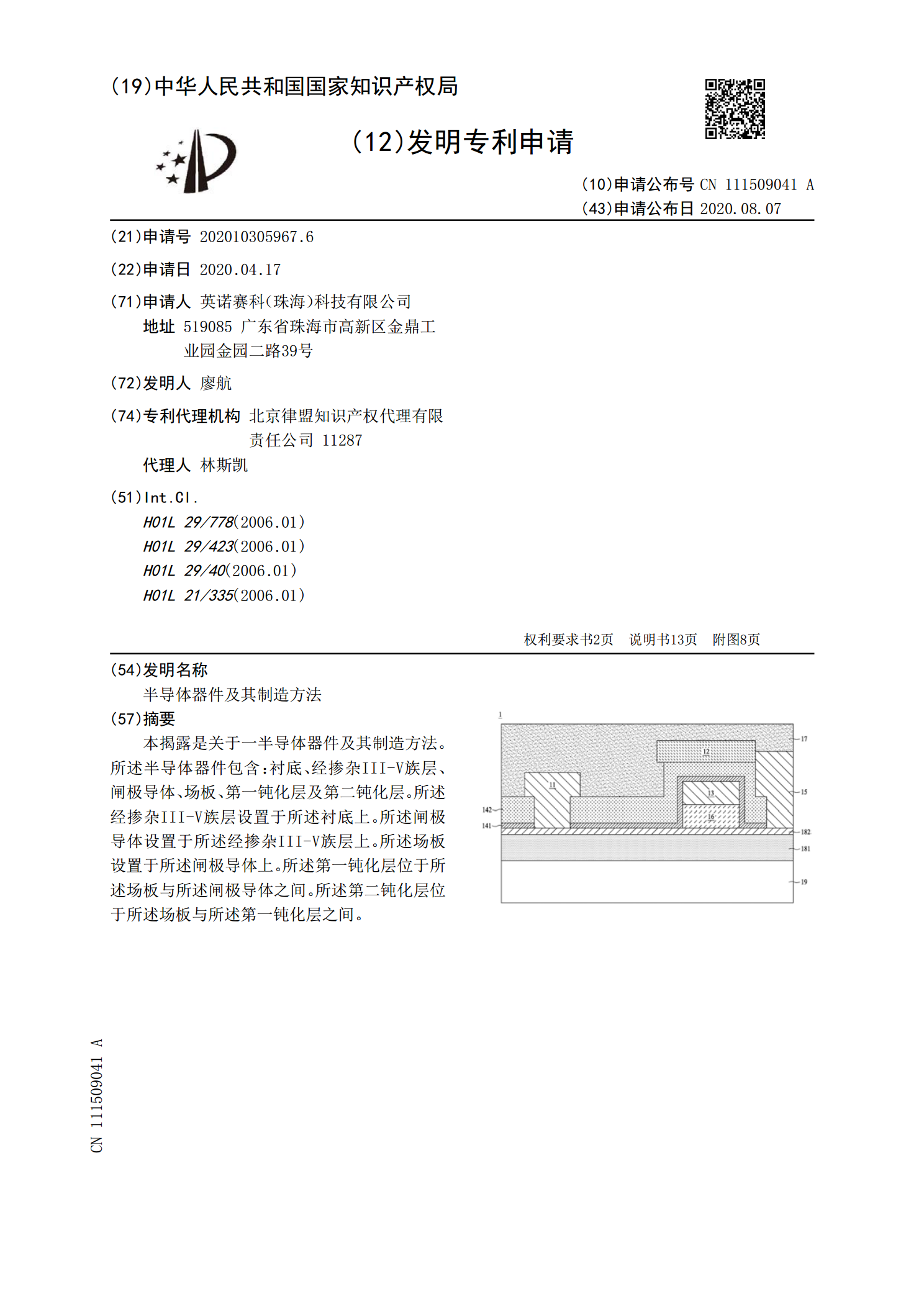

本揭露是关于一半导体器件及其制造方法。所述半导体器件包含:衬底、经掺杂III‑V族层、闸极导体、场板、第一钝化层及第二钝化层。所述经掺杂III‑V族层设置于所述衬底上。所述闸极导体设置于所述经掺杂III‑V族层上。所述场板设置于所述闸极导体上。所述第一钝化层位于所述场板与所述闸极导体之间。所述第二钝化层位于所述场板与所述第一钝化层之间。